# 修士学位論文

System-on-a-Chip を用いたエレクトロニクス制御回路の開発- 高放射線環境での大規模システムへの応用

( Development of a System-on-a-Chip based control board- Application to a large-scale electronics system in a high radiation area )

> 東京大学大学院 理学系研究科 物理学専攻 石野研究室 田中 碧人

> > 2021年1月

# 概要

2027 年開始予定の高輝度 LHC-ATLAS 実験に備え、ATLAS 検出器は大幅にアップグレードされる。 ATLAS 検出器のエンドキャップ部に位置し、陽子衝突点から飛来するミューオンの飛来位置と運動量を 測定する Thin Gap Chamber (TGC) 検出器においても、読み出し・トリガー回路システムがアップグレードされる。各フロントエンド回路では FPGA が使用され、放射線環境下に置かれる。FPGA のコンフィギュレーションに加え、Single Event Upset (SEU) を監視し必要に応じて自動修復を行う新たな制御系が必要となる。この要求に対しフロントエンド回路を監視・管理するハブモジュールを中心とした制御系の開発を進めている。

本研究では、FPGA と CPU を組み合わせた Xilinx 社製の Zynq SoC デバイスをメインドライバーとして搭載した制御回路を開発している。制御回路には主に 4 つの機能が実装される。

- i. 制御回路の Zynq と ATLAS 実験室外を光ケーブルを介して接続し、イーサネット通信を行う機能

- ii. 各フロントエンド回路の FPGA を JTAG 通信でコンフィギュレーションするハブ機能

- iii. 回復不可能な SEU が起きたフロントエンド回路へ回復信号を自動で送り修復する機能

- iv. 不揮発性メモリの放射線損傷を想定し冗長性を持って起動する機能

本制御回路を含む電気回路システムの実証試験を行うため、制御回路の試作機の設計と製造を行った。また、試作機にて制御回路の全機能の動作試験を達成した。更に、動作試験の結果を踏まえて必要な修正を加え、量産機の生産に向けた最終デザインの確立も実現した。

また、本制御回路の開発研究にて得られた成果を通して、大規模システムのコントロールと信頼性の高いシステム構築という点において、Zynq SoC デバイスの素粒子実験における有用性が明らかになった。

# 目次

| 概要  |                                                  | 2  |

|-----|--------------------------------------------------|----|

| 第1章 | ·····································            | 11 |

| 1.1 | 研究背景                                             | 11 |

|     | 1.1.1 ATLAS 実験と TGC 検出器                          | 12 |

|     | 1.1.2 ATLAS 実験のオンライン事象選別                         | 13 |

|     | 1.1.3 高輝度 LHC アップグレード計画                          | 13 |

|     | 1.1.4 高輝度 LHC-ATLAS 実験の Trigger and DAQ system   | 13 |

| 1.2 | 研究目的                                             | 15 |

| 1.3 | 本論文の構成                                           | 16 |

| 第2章 | 高輝度 LHC-ATLAS 実験における TGC 検出器エレクトロニクスシステム         | 17 |

| 2.1 | Level-0 endcap muon trigger system               | 17 |

|     | 2.1.1 TGC 検出器とフロントエンド機器の位置関係                     | 18 |

|     | 2.1.2 TGC 検出器                                    | 18 |

|     | 2.1.3 Amplifier Shaper Discriminator (ASD) ボード   | 20 |

|     | 2.1.4 PS board                                   | 21 |

|     | 2.1.5 HSC (VME) crate                            | 23 |

|     | 2.1.6 Sector Logic (SL)                          | 24 |

|     | 2.1.7 Front-End LInk eXchange(FELIX)             | 25 |

|     | 2.1.8 アップグレードによる Performance の向上                 | 25 |

| 2.2 | フロントエンド側エレクトロニクスシステムの要請                          | 27 |

|     | 2.2.1 ATLAS 実験室内の FPGA に対して遠隔で configuration を実行 | 27 |

|     | 2.2.2 フロントエンドに堅牢で信頼性の高いシステムを構築                   | 27 |

| 2.3 | 制御系の確立....................................       | 30 |

|     | 2.3.1 制御系の概要                                     | 30 |

|     | 2.3.2 制御系回路の必要数                                  | 31 |

| 第3章 | 制御回路 JTAG Assistance Hub (JATHub)                | 33 |

| 3.1 | 概念設計                                             | 33 |

|     |     | 3.1.1 必要な機能                       | 33 |

|-----|-----|-----------------------------------|----|

|     |     | 3.1.2 ATLAS 実験室内の設備との親和性に関する考察    | 36 |

|     |     | 3.1.3 ハードウェア設計への要請                | 38 |

|     | 3.2 | ハードウェアの設計                         | 40 |

|     |     | 3.2.1 JATHub のインターフェイスと周辺機器       | 40 |

|     |     | 3.2.2 CAT6 ケーブルを使用した他回路との LVDS 通信 | 44 |

|     |     | 3.2.3 等長配線                        | 47 |

|     |     | 3.2.4 電源周り                        | 48 |

|     |     | 3.2.5 評価ボードによる機能のデモンストレーション       | 49 |

|     | 3.3 | JATHub 第1試作機の製作                   | 49 |

|     |     | 3.3.1 部品配置とフロントパネルデザイン            | 50 |

|     |     | 3.3.2 プリント基板 (PCB) レイアウト概要        | 51 |

|     |     | 3.3.3 試作機納品                       | 51 |

| 第4章 |     | JATHub 第1試作機の機能実装と動作試験            | 54 |

|     | 4.1 | 開発環境                              | 54 |

|     |     | 4.1.1 <b>Z</b> ynq 組み込みデザインの開発    | 54 |

|     |     | 4.1.2 テストベンチ                      | 55 |

|     | 4.2 | 光イーサネット通信                         | 58 |

|     |     | 4.2.1 Zynq における光 Ethernet 通信の仕組み  | 59 |

|     |     | 4.2.2 光 Ethernet 通信の動作試験          | 59 |

|     | 4.3 | JTAG 通信による Slave module の制御       | 60 |

|     |     | 4.3.1 Xilinx Virtual Cable(XVC)   | 62 |

|     |     | 4.3.2 SVF player                  | 65 |

|     |     | 4.3.3 開発した JTAG 通信の本番時の運用         | 66 |

|     | 4.4 | Slave module の Recovery 手続き       | 67 |

|     |     | 4.4.1 PS board に対して               | 67 |

|     |     | 4.4.2 隣の JATHub に対して              | 68 |

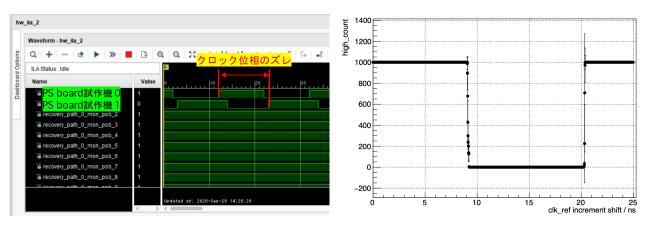

|     | 4.5 | LHC クロック位相のモニター                   | 70 |

|     |     | 4.5.1 モニター方法の実装                   | 70 |

|     |     | 4.5.2 モニター試験                      | 71 |

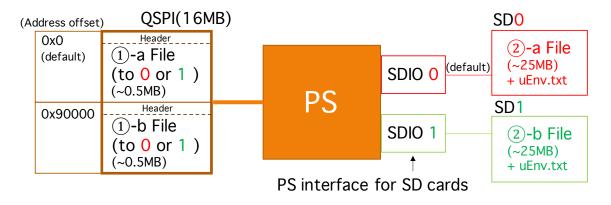

|     | 4.6 | 冗長性のある BOOT システム                  | 72 |

|     |     | 4.6.1 BOOT システムの仕組み               | 72 |

|     |     | 4.6.2 冗長性を保障する動作                  | 73 |

|     | 4.7 | VME 操作                            | 75 |

| 第5章 |     | JATHub 第 2 試作機の製作                 | 76 |

|     | 5.1 | JATHub 第 1 試作機からの修正点              | 76 |

|     |     |                                   |    |

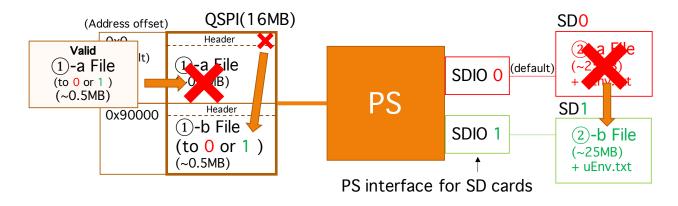

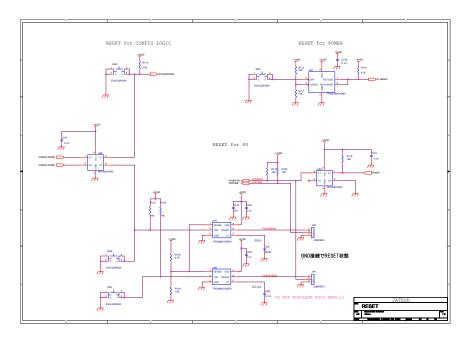

|             | 5.1.1 reset 線における LVDS 通信の動作改善       | . 76  |

|-------------|--------------------------------------|-------|

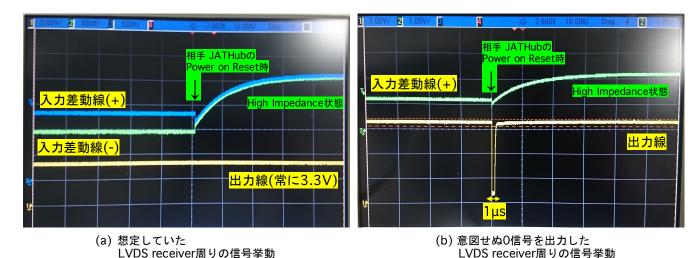

|             | 5.1.2 LHC クロックと同周波数の水晶発振器の実装         | . 79  |

|             | 5.1.3 QSPI flash memory へのアクセスパス追加   | . 79  |

|             | 5.1.4 master としての test-14pin を実装     | . 81  |

|             | 5.1.5 Debug tool の不実装                | . 81  |

|             | 5.1.6 Fuse 回路の最適化                    | . 82  |

| 5.2         | 回路図修正とレイアウト修正                        | . 82  |

| 第6章         | 結論と今後の展望                             | 83    |

| 6.1         | 本研究の結論                               | . 83  |

| 6.2         | JATHub 開発研究の今後の展望                    | . 83  |

| Appendix A  | TGC 検出器エレクトロニクスシステムの全体像とスケール         | 87    |

| Appendix B  | 自動回復不可能な SEU 事象の発生頻度の概算              | 88    |

| Appendix C  | JATHub と Slave module の CAT6 Cabling | 89    |

| Appendix D  | JATHub 試作機の回路図                       | 91    |

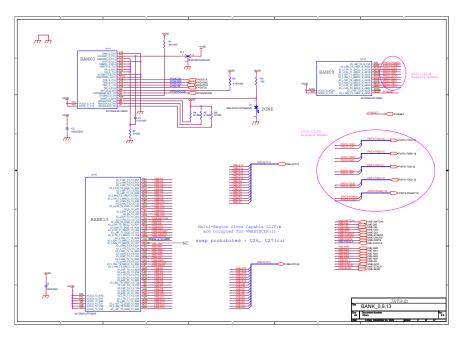

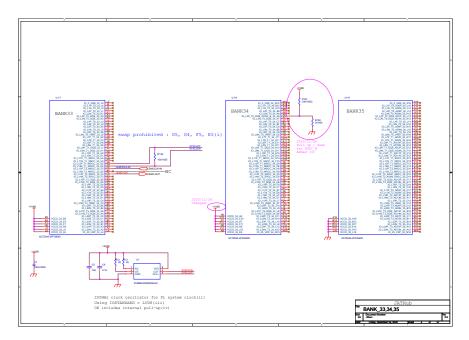

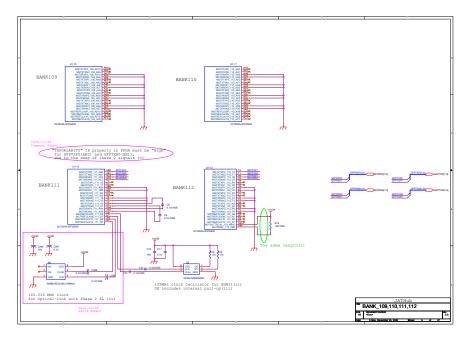

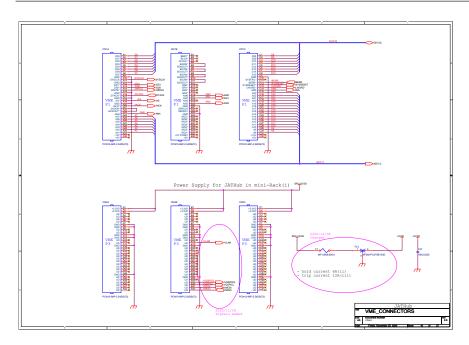

| D.1         | JATHub 第 1 試作機の回路図 (全 26 ページ)        | . 91  |

| D.2         | JATHub 第 2 試作機の回路図 (変更した主なページ)       | . 104 |

| Appendix E  | JATHub 試作機の 14 層構造表                  | 108   |

| Appendix F  | Zynq 組み込みデザインの Diagram               | 110   |

| Appendix G  | PHY chip 不要な Zynq の Ethernet 通信      | 112   |

| Appendix H  | XVC を利用した Debug Bridge 機能            | 113   |

| Appendix I  | SVF ファイルの中身 (Kintex-7 QSPI program)  | 114   |

| <del></del> |                                      | 116   |

# 図目次

| 1.1  | 標準理論を構成する素粒子・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ | 11 |

|------|--------------------------------------------------|----|

| 1.2  | LHC の全体像と 4 つの衝突点                                | 12 |

| 1.3  | ATLAS 検出器                                        | 12 |

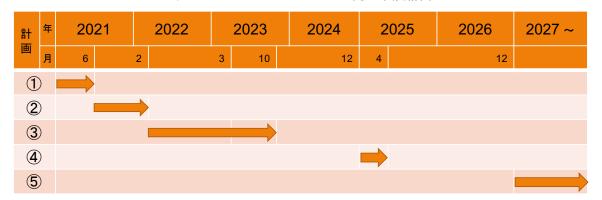

| 1.4  | LHC と高輝度 LHC の運転計画                               | 14 |

| 1.5  | 高輝度 LHC-ATLAS 実験の TDAQ system 概要                 | 15 |

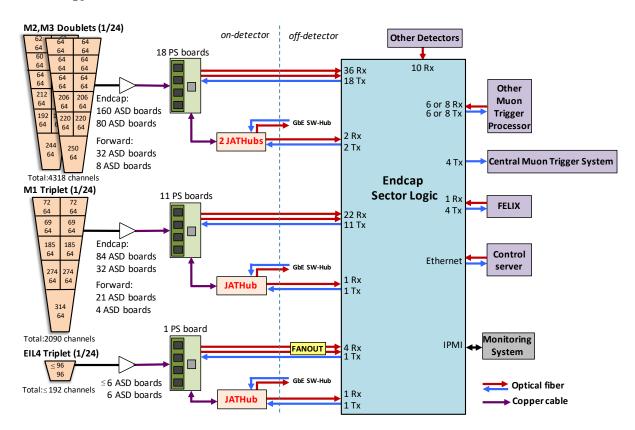

| 2.1  | Level-0 endcap muon trigger system の全体像          | 18 |

| 2.2  | TGC 検出器の正面写真                                     | 19 |

| 2.3  | TGC 検出器の側面図                                      | 19 |

| 2.4  | TGC 検出器の構造                                       | 20 |

| 2.5  | ASD                                              | 21 |

| 2.6  | PS board 概念図                                     | 22 |

| 2.7  | PS board 第 1 試作機の写真                              | 22 |

| 2.8  | mini-Rack 内にある HSC VME crate                     | 24 |

| 2.9  | Sector Logic の概念図                                | 25 |

| 2.10 | 物理 Acceptance 向上の例                               | 26 |

| 2.11 | SEU 回数試験の結果                                      | 29 |

| 2.12 | 制御系の概念図                                          | 30 |

| 2.13 | TGC 検出器の写真 (BW1/12 セクター)                         | 32 |

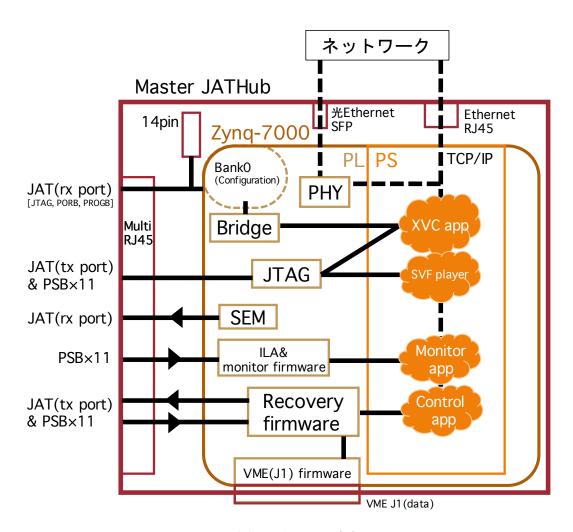

| 3.1  | JATHub の設計概要図                                    | 34 |

| 3.2  | HSC crate 内の JATHub の実装                          | 37 |

| 3.3  | JATHub を制御系の中心として組み込んだ TGC 検出器エレクトロニクスシステム       | 39 |

| 3.4  | Zynq にドライブされる JATHub の周辺機器                       | 41 |

| 3.5  | RJ45 multi-jack の概要図                             | 43 |

| 3.6  | LVDS 接続 JATHub/PSB JTAG パス                       | 45 |

| 3.7  | LVDS 接続 JATHub/PSB Recovery パス                   | 45 |

| 3.8  | LVDS 接続 JATHub/JATHub JTAG パス                    | 45 |

| 3.9  | LVDS 接続 JATHub/JATHub Recovery パス                | 45 |

| 3.10 | LVDS 素子                                          | 47 |

図目次 7

| 3.11 | CAT6 ケーブルの種類                                     | 47  |

|------|--------------------------------------------------|-----|

| 3.12 | 等長配線を指示した信号線・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ | 48  |

| 3.13 | Zynq 電源の供給順序                                     | 49  |

| 3.14 | ZC706 評価ボードによるデモンストレーション                         | 50  |

| 3.15 | 第1試作機での部品配置とフロントパネルデザイン                          | 52  |

| 3.16 | SFP0 の TX 差動線の極性のスワップ                            | 52  |

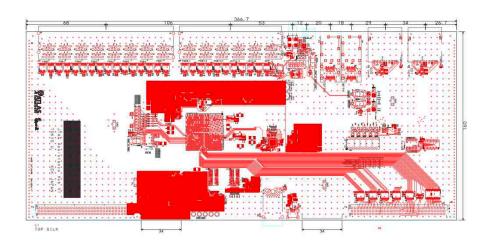

| 3.17 | 第 1 試作機の PCB レイアウト                               | 53  |

| 3.18 | JATHub 第1試作機の写真                                  | 53  |

| 4.1  | テストベンチの概要図                                       | T.C |

| 4.1  | KEK テストベンチ写真                                     |     |

| 4.2  | JATHub 第 1 試作機の RJ45 multi-jack                  |     |

| 4.3  | 光 Ethernet 通信の仕組み                                |     |

| 4.4  | 光 Ethernet 通信試験のセットアップ                           |     |

| 4.6  | 光 Ethernet 通信試験の結果                               |     |

| 4.0  | 元 Ethernet 通信試験の相来                               |     |

| 4.7  |                                                  |     |

| 4.8  | XVC によるハブ機能付き configuration                      |     |

| 4.9  | XVC による ILA の使用                                  |     |

| 4.10 | XVC と SVF を実装した Zynq デザイン                        |     |

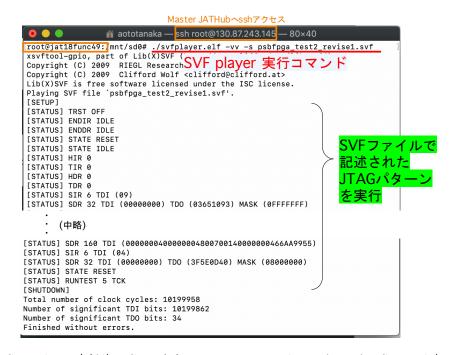

| 4.11 | SVF player 実行時の CUI 画面                           |     |

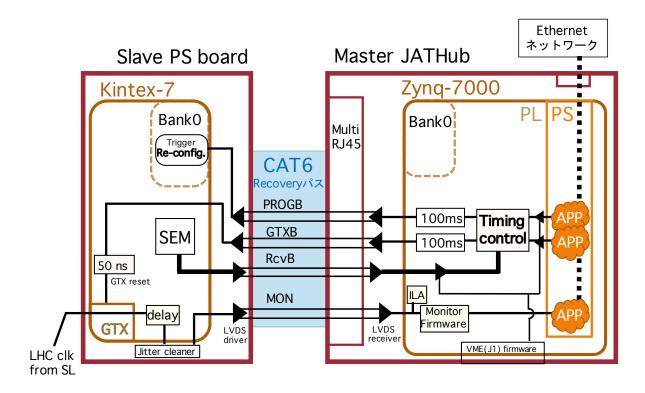

| 4.12 | PSB の Recovery 手続き概要                             |     |

| 4.13 |                                                  |     |

|      | 隣の JATHub の Recovery 手続き概要                       |     |

| 4.15 | LHC クロックモニター方法                                   |     |

| 4.16 | LHC クロックモニダー動作試験結果                               |     |

| 4.17 |                                                  |     |

| 4.18 | 冗長性を保障する動作                                       |     |

| 4.19 | VME による register 操作試験                            | 75  |

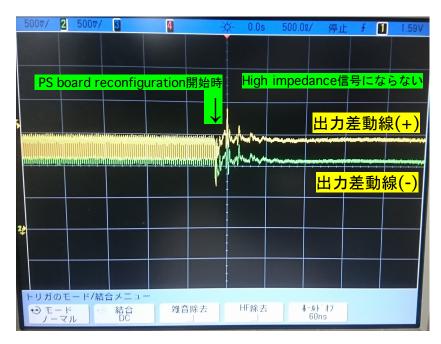

| 5.1  | LVDS receiver の入出力信号の挙動測定結果                      | 77  |

| 5.2  | PUDC_B を GND に落とした際の LVDS driver 差動出力線の様子        | 78  |

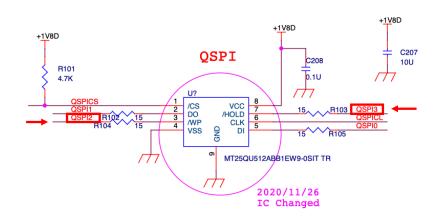

| 5.3  | 第 2 試作機での (Q)SPI 素子アクセスパス概要                      | 80  |

| 5.4  | QSPI 素子の回路シンボル                                   | 81  |

| 5.5  | JATHub 第 2 試作機の簡易部品レイアウト                         | 82  |

| A.1  | TGC 検出器エレクトロニクスの全体像概念図                           | 87  |

| C.1  | JATHub と Slave module の CAT6 Cabling             | 90  |

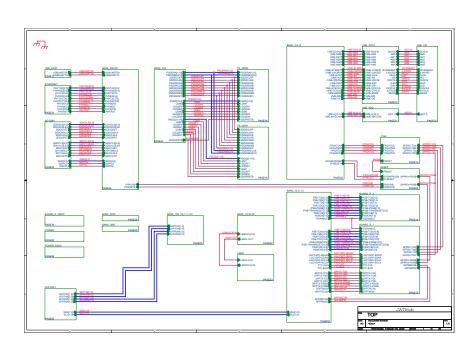

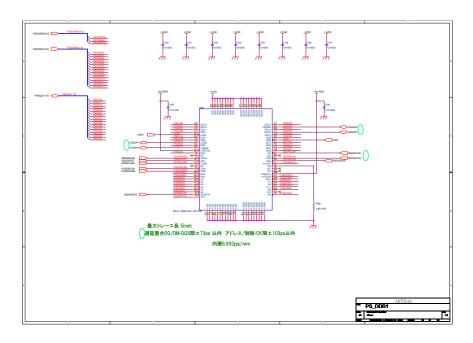

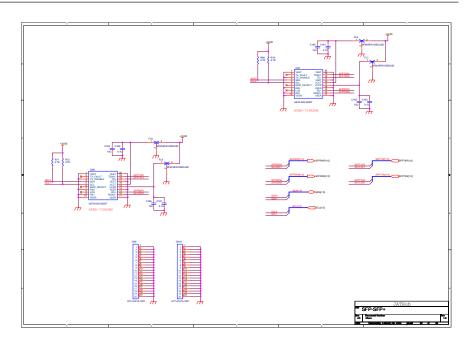

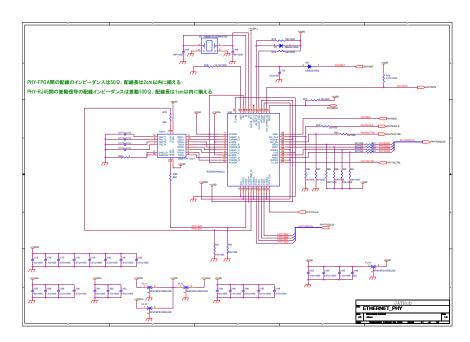

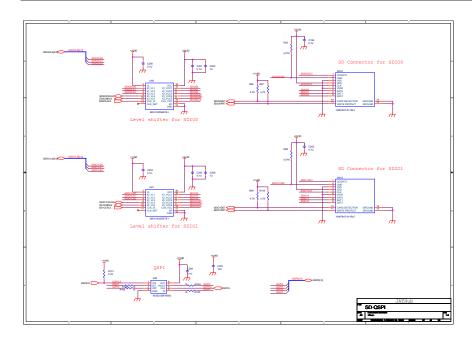

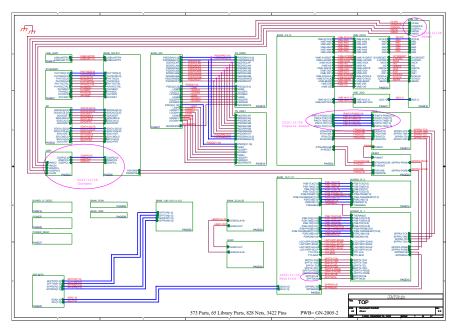

| D.1  | JATHub 第 1 試作機の回路図 TOP                          |

|------|-------------------------------------------------|

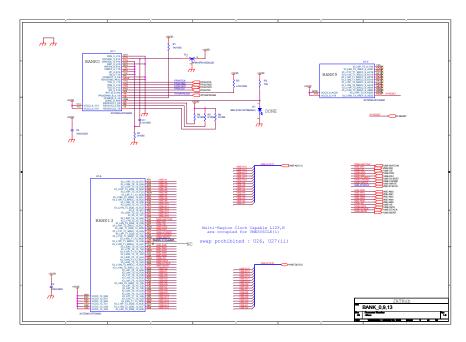

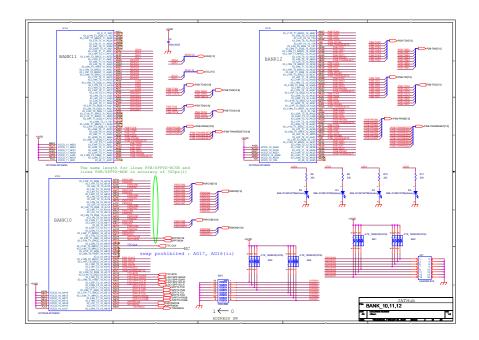

| D.2  | JATHub 第 1 試作機の回路図 BANK 0,9,13                  |

| D.3  | JATHub 第 1 試作機の回路図 BANK 10,11,12                |

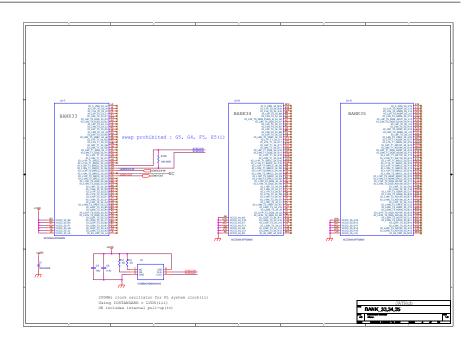

| D.4  | JATHub 第 1 試作機の回路図 BANK33,34,35                 |

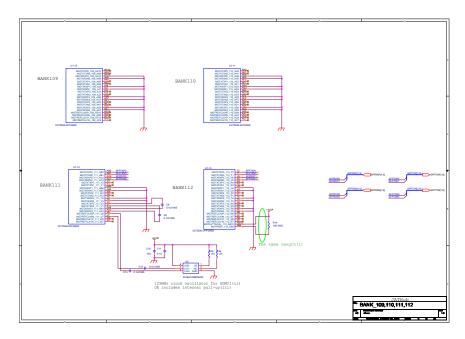

| D.5  | JATHub 第 1 試作機の回路図 BANK109,110,111,112          |

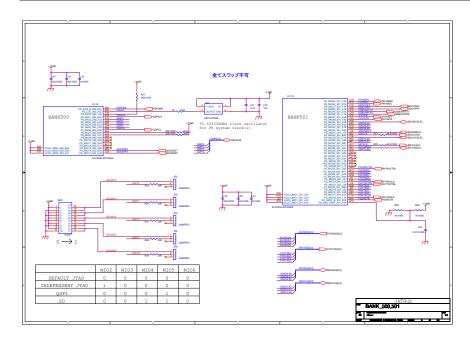

| D.6  | JATHub 第 1 試作機の回路図 BANK500,501                  |

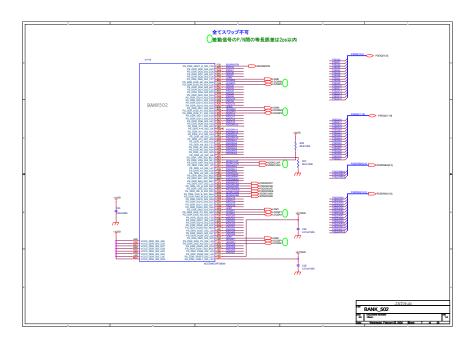

| D.7  | JATHub 第 1 試作機の回路図 BANK502                      |

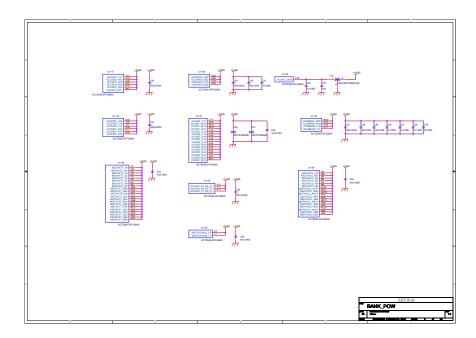

| D.8  | JATHub 第1試作機の回路図 BANK POWER                     |

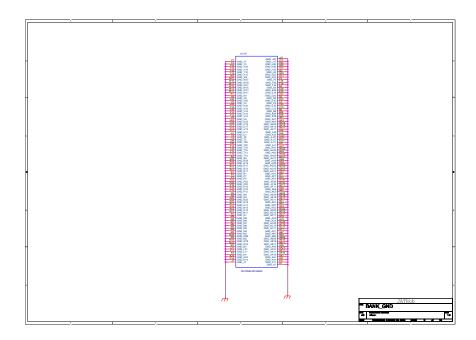

| D.9  | JATHub 第1試作機の回路図 BANK GND                       |

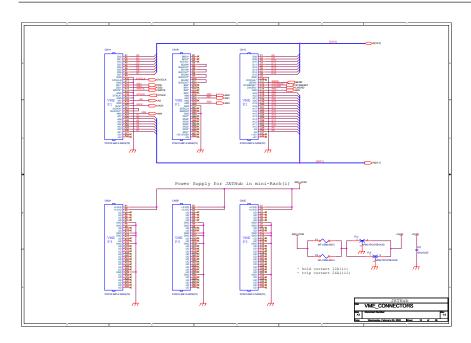

| D.10 | JATHub 第1試作機の回路図 VME CONNECTOR                  |

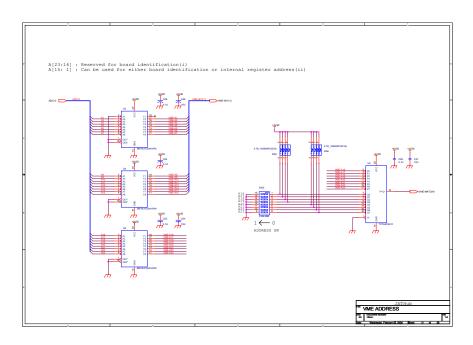

| D.11 | JATHub 第1試作機の回路図 VME ADDRESS                    |

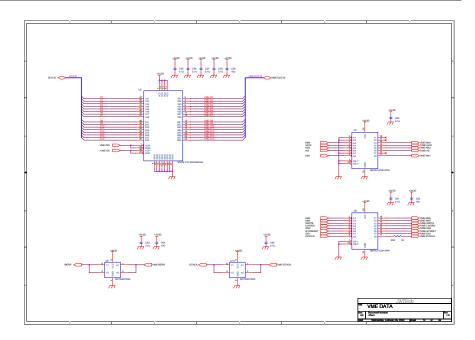

| D.12 | JATHub 第1試作機の回路図 VME DATA                       |

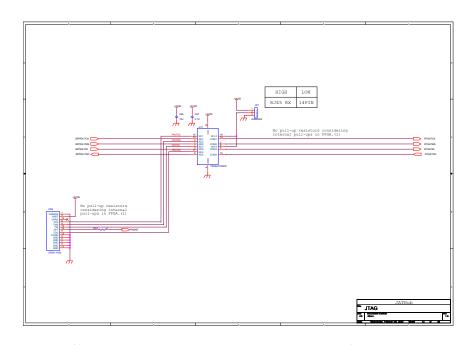

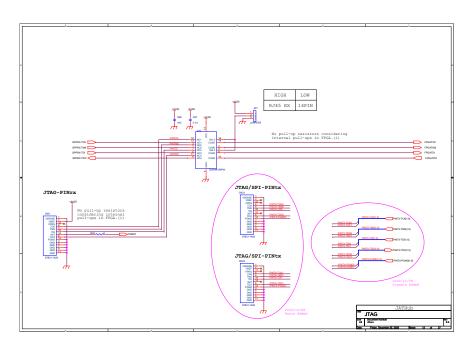

| D.13 | JATHub 第1試作機の回路図 JTAG                           |

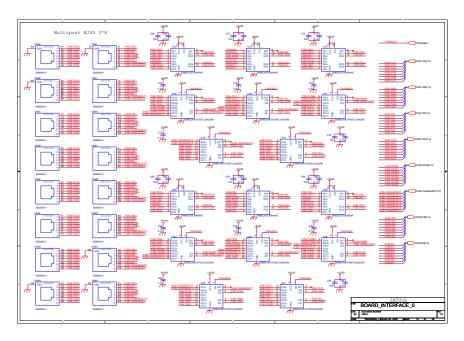

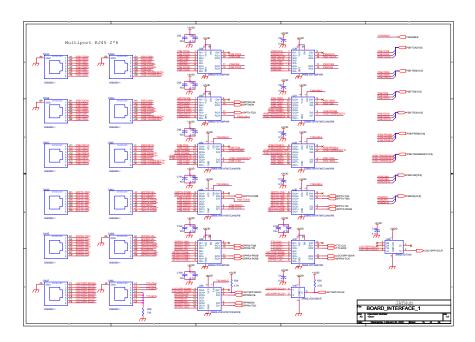

| D.14 | JATHub 第1試作機の回路図 BOARD INTERFACE0               |

| D.15 | JATHub 第1試作機の回路図 BOARD INTERFACE1               |

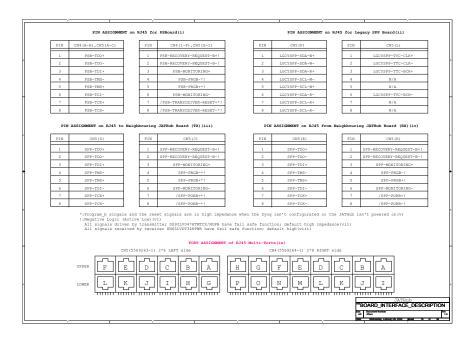

| D.16 | JATHub 第1試作機の回路図 BOARD INTERFACE DESCRIPTION 99 |

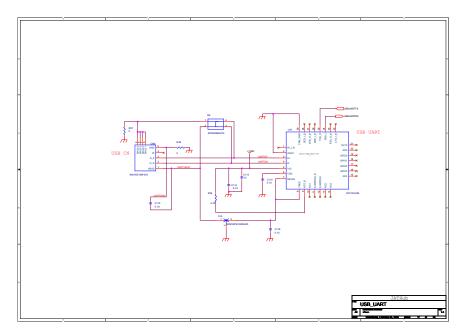

| D.17 | JATHub 第1試作機の回路図 USB-UART                       |

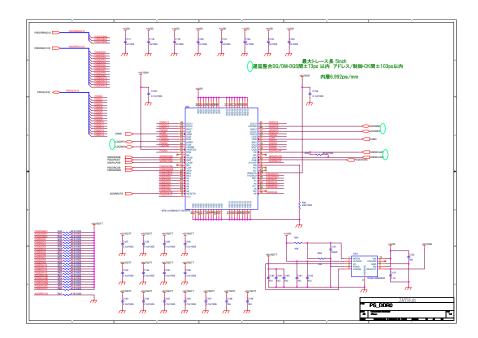

| D.18 | JATHub 第 1 試作機の回路図 PS DDR0                      |

| D.19 | JATHub 第 1 試作機の回路図 PS DDR1                      |

| D.20 | JATHub 第 1 試作機の回路図 SFP                          |

| D.21 | JATHub 第1試作機の回路図 ETHERNET PHY                   |

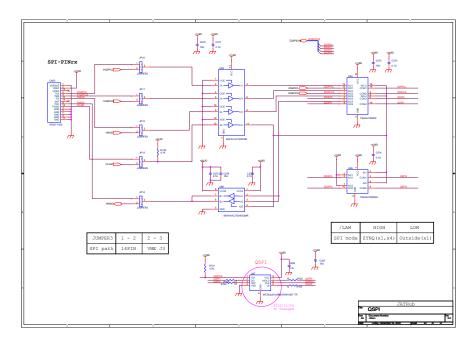

| D.22 | JATHub 第 1 試作機の回路図 SD QSPI                      |

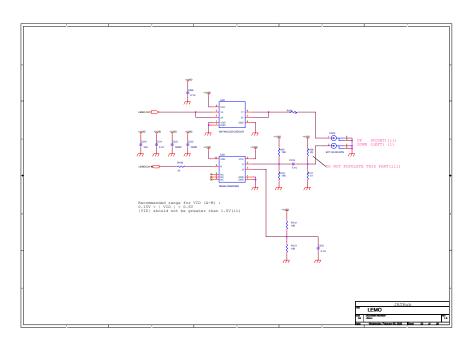

| D.23 | JATHub 第 1 試作機の回路図 LEMO                         |

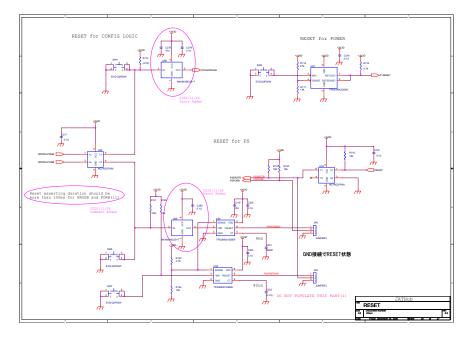

| D.24 | JATHub 第1試作機の回路図 RESET                          |

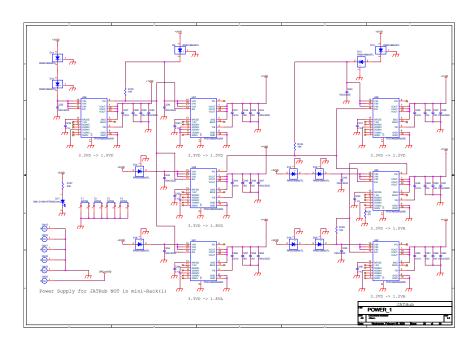

| D.25 | JATHub 第 1 試作機の回路図 電源                           |

| D.26 | JATHub 第 2 試作機の回路図 TOP                          |

| D.27 | JATHub 第 2 試作機の回路図 BANK 0,9,13                  |

| D.28 | JATHub 第 2 試作機の回路図 BANK 33,34,35                |

| D.29 | JATHub 第 2 試作機の回路図 BANK 109,110,111,112         |

| D.30 | JATHub 第 2 試作機の回路図 VME CONNECTOR                |

| D.31 | JATHub 第 2 試作機の回路図 JTAG                         |

| D.32 | JATHub 第 2 試作機の回路図 QSPI                         |

| D.33 | JATHub 第 2 試作機の回路図 RESET                        |

| F.1  | <b>Z</b> ynq に実装した組み込みデザインの全体像111               |

| G.1  | PHY chip 不要な Zynq の Ethernet 通信の概要図             |

| H.1  | Debug Bridge 機能によって PL の信号線をデバックする様子            |

| 図目次 | 9 |

|-----|---|

|     |   |

| I.1 | Vivado HM での SVF ファイル作成方法 | 14 |

|-----|---------------------------|----|

| I.2 | SVF ファイルの中身               | 15 |

# 表目次

| 2.1 | Trigger and DAQ system のレイテンシーと読み出し頻度 | 26  |

|-----|---------------------------------------|-----|

| 2.2 | 制御系にある回路の必要数 $(BW1/12$ セクター単位 $)$     | 31  |

| 2.3 | 制御系にある回路の必要数 (ATLAS 実験室全体)            | 32  |

| 3.1 | RJ45 multi-jack の使用ポートの割り当て           | 43  |

| 4.1 | Zynq 組み込みデザイン開発環境                     | 55  |

| 4.2 | JATHub 第 1 試作機の消費電力                   | 57  |

| 4.3 | 光 Ethernet 通信試験でのネットワーク設定             | 61  |

| 5.1 | QSPI flash memory へのアクセス方法            | 80  |

| 6.1 | JATHub モジュールの今後の開発計画                  | 84  |

| B.1 | FPGA の中性子照射試験の結果 [8]                  | 88  |

| B.2 | PS board 上の URE 発生頻度概算                | 88  |

| E.1 | JATHub 第1試作機の PCB 階層構成                | 108 |

# 第1章

# 序章

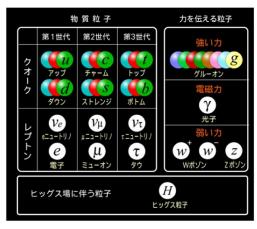

素粒子物理学において、標準理論は物理現象を説明する上で最も成功した理論体系である。標準理論は、6種類のクオーク、6種類のレプトン、4種類のゲージボソン、そしてヒッグス粒子の全 17種類の素粒子 (図 1.1)で構成されており、それらの相互作用を"電磁力"、"弱い力"、"強い力"の 3 つの力で記述した理論である。20世紀の間に素粒子物理実験では数多くの素粒子を発見し、CMS実験と後述する ATLAS 実験における 2012 年のヒッグス粒子の発見を最後に、標準理論が予言した全 17種類の素粒子の存在が証明された。しかし、未だ標準理論では説明できない物理現象は存在する。例えば、暗黒物質の正体や、階層性問題、ニュートリノの質量などである。素粒子物理実験では、高エネルギーフロンティアの開拓を行ったり、測定の精度向上を行う等、実験的なアプローチか

図 1.1 標準理論を構成する素粒子 [1]。

ら、これらの未解決問題に挑戦し続けて、標準理論を超える新物理の探索を行っている。

この実験的なアプローチを確固たるものにするには、大規模な素粒子物理実験を安定して遂行できる運用システムが必須である。その運用システムの中でも、本研究は、放射線環境下のシステム制御に焦点を置いた。更にその制御デザインを ATLAS の将来実験に応用した。本論文では、システム制御の設計とその実現に向けた開発研究について述べる。本章は本題に入る前の研究背景として ATLAS の将来実験について述べていく。

## 1.1 研究背景

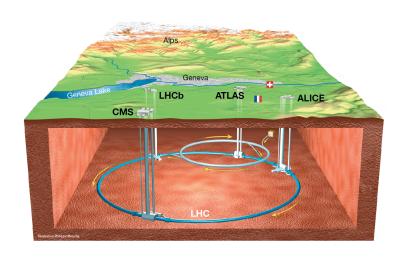

スイスのジュネーブ郊外にある欧州原子核研究機構 (CERN) では、全長 27 km の陽子陽子衝突大型円形加速器である Large Hadron Collider (LHC) (図 1.2) が地下 100 m に設置されている。陽子同士を世界最高エネルギーである重心エネルギー 13 TeV で衝突させ、その結果として生じる物理現象を 4 つの衝突点に設置されている検出器で観測している。その 4 つの検出器とは、Large Hadron Collider beauty (LHCb) 検出器、A Large Ion Collider (ALICE) 検出器、Compact Muon Solenoid (CMS) 検出器、A Toroidal Lhc ApparatuS (ATLAS) 検出器である。本研究は ATLAS 実験に関わる内容である。

12 1.1. 研究背景

図 1.2 LHC の全体像と 4 つの衝突点 [2]。

### 1.1.1 ATLAS 実験と TGC 検出器

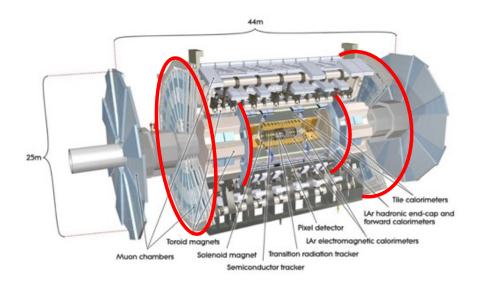

ATLAS 実験は、CMS 実験と同様に、広い領域での新物理探索とヒッグス粒子の精密測定を主な目的としている。ATLAS 検出器 (図 1.3) は全長  $44~\mathrm{m}$ 、高さ  $25~\mathrm{m}$ の大型検出器である。本研究では両サイドの Endcap 部にある muon trigger 検出器である Thin Gap Chamber (TGC) 検出器 (図  $1.3~\mathrm{o}$  の赤枠の検出器) のエレクトロニクスシステムの制御に焦点を当てている。

図 1.3 ATLAS 検出器と TGC 検出器 (赤枠)[3]。 Endcap 部外側の円盤状の検出器が Big Wheel (BW) と呼ばれる TGC 検出器、Endcap 部内側の円盤状の検出器が Endcap Inner (EIL4) と呼ばれる Inner TGC 検出器。

第 1. 序章 13

#### 1.1.2 ATLAS 実験のオンライン事象選別

LHC では能動的に 40 MHz で陽子同士を衝突させるが、ほとんどの衝突事象は運動量移行の小さいパートンの弾性散乱であり、大きな運動量移行が伴うことが期待される ATLAS 実験の物理解析を行う上で興味の無い事象である。一方、興味のある衝突事象が発生した時は、その衝突で得られた生成物が崩壊して特徴量が出現する。そのため、その特徴量を検出し、重要な衝突事象データのみをオンラインで選別して有限な CERN の Permanent Storage に残す必要がある。また、ハドロンコライダーゆえ、興味のある衝突事象も多岐に渡る。検出する特徴量も様々で、それぞれの衝突事象に応じて包括的に事象選別を行う必要もある。

そこで、ATLAS 実験では、電子、ミューオン、光子、ジェット、消失横運動量などに注目し、2 段階でオンラインの事象選別 (Trigger) をしている。初段 Trigger では、高速で信号処理を行うために、専用のHardware を用いている。後段 Trigger では、更に厳しい Trigger 判定を行うために、Software を用いている。

#### 1.1.3 高輝度 LHC アップグレード計画

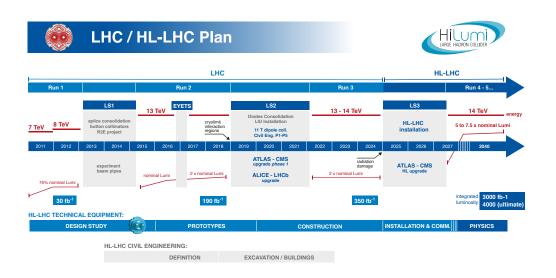

CERN では、現行の LHC 加速器の輝度を大幅に向上させるプロジェクト、「高輝度 LHC アップグレード $^{*1}$ 」に取り組んでおり、2027 年の運転開始を目指している。高輝度 LHC は 10 年間の運転が計画されており、前運転の Run 3 が終了する 2025 年から新しい装置のインストールが始まる予定である。図 1.4 に高輝度 LHC(HL-LHC) の運転計画が記されてある。

高輝度 LHC アップグレードの特徴は、瞬間最高 Luminosity を現行の約 3 倍の  $5^{\sim}7.5\times10^{34}$  cm $^{-2}$ s $^{-1}$  に向上させ、重心衝突エネルギー 14 TeV にて運転することにある。運転期間全体で 3000 fb $^{-1}$  以上の積分 Luminosity に到達する予定である。

高輝度 LHC アップグレードの目的は、興味のある物理事象データの統計量を増大させることである。統計量の増大により大幅な改善がみられる物理解析の例 $^{*2}$ として、現在 LHC でのみ観測可能なヒッグスボソンの精密測定がある。1 例として、 $H \to bb$  崩壊の際の湯川結合定数の精密測定がある。様々な新物理の理論では、その結合定数が標準理論から逸脱することが示唆されている。そのため、高輝度 LHC の高統計量によって標準理論からの逸脱が精密に観測されれば、新物理モデルを絞り込めるので、素粒子物理の将来の方向性が決められると期待されている。

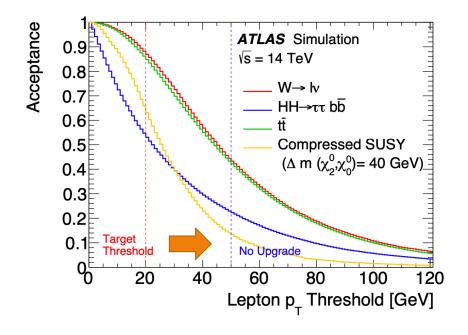

#### 1.1.4 高輝度 LHC-ATLAS 実験の Trigger and DAQ system

ATLAS 実験でも高輝度 LHC アップグレードに合わせて、検出器やエレクトロニクスの多くが一新され、高輝度環境における物理事象観測に備える。ここで、現行システムの Trigger 性能のまま瞬間 最高 Luminosity が増大すると、Trigger をかける横運動量  $(P_T)$  閾値を上げなければならない。しかし、興味のある物理事象データを取得するためには、 $P_T$  閾値を低く抑える必要がある。そこで、高輝度

<sup>\*1 &</sup>quot;Phase 2 Upgrade"、"High Luminosity (HL)-LHC Upgrade"とも呼ばれている。本論文では "高輝度 LHC" と呼ぶ。

<sup>\*2</sup> 他の例としては、余剰次元理論や超対称性理論にて予言された新粒子の直接探索もある。

14 1.1. 研究背景

図 1.4 LHC と高輝度 LHC の運転計画 [4]。 高輝度 LHC の装置実装は 2025 年から行われる予定、高輝度 LHC の運転開始は 2027 年の予定。

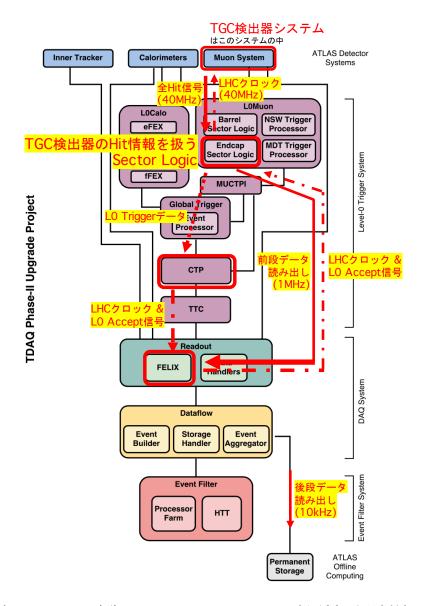

LHC-ATLAS 実験では、Trigger and DAQ system のエレクトロニクスを一新し、Trigger 性能の向上を目指す。Trigger 性能向上の詳細は 2.1.8 節にて述べる。本節では、高輝度 LHC-ATLAS 実験におけるTrigger and DAQ system(図 1.5) について説明する。

高輝度 LHC-ATLAS 実験の Trigger and DAQ system は、Level-0 Trigger、DAQ、Event Filter(EF) に分かれる。

高輝度 LHC-ATLAS 実験における Hardware での初段 Trigger 処理は Level-0 trigger と呼ばれており、ミューオン、カロリーメータ、内部飛跡検出器の Trigger 情報を使用して、有益な衝突事象に対して Level-0 Accept 信号 (LOA) を発行する。包括的な Level-0 trigger 処理と LOA の発行は CTP で行われる。そして、CTP から、ATLAS 全体の読み出しを担う FELIX を経由して、LOA 信号と LHC クロックが各検出器システムに送られる。各システムでは、40MHz で捉えた衝突データを Buffer に保管しており、LOA 信号を受けた場合は、該当する衝突データを FELIX へ送る。FELIX は LOA によって送られた読み出しデータを受け取り、後段 Trigger へ送る。後段 Trigger では EF がソフトウェアベースで DAQ system 内のデータの Trigger 処理を行う。最後まで残った衝突事象データが CERN の Permanent Storage に保存される。

TGC 検出器は ATLAS 検出器の Endcap 部に飛来するミューオンを検出し、運動量と飛来位置を概算し、Trigger 情報を初段 Trigger システムに送る。そのため、図 1.5 のように高輝度 LHC-ATLAS 実験において Level-0 muon trigger system の検出器として機能する。このアップグレードに際して、TGC 検出器のエレクトロニクスシステムも一新される。Level-0 Muon Trigger System の Endcap 部をカバーしているので、TGC 検出器の読み出し・トリガーエレクトロニクスシステムは、本論文では Level-0 endcap muon trigger system と呼ぶ。第 2 章にて、Level-0 endcap muon trigger system について詳細に触れていく。

第 1. 序章 15

図 1.5 高輝度 LHC-ATLAS 実験の Trigger and DAQ system の概要 [5]。本研究対象の TGC 検出器エレクトロニクスに関わる箇所とデータの流れを赤字で示す。

## 1.2 研究目的

高輝度 LHC-ATLAS 実験における Level-0 endcap muon trigger system のフロントエンド回路では、TGC 検出器の全ヒット情報を高速光通信(8 Gbps ) でバックエンド回路へ送信する。その実現のため、新しくフロントエンド回路に FPGA を搭載している。この FPGA は、2.2 節にて議論するように、物理的にアクセスが難しい場所に設置される予定のため、外部から FPGA の Firmware のプログラムやデバック、FPGA の reconfiguration 用 flash memory のプログラムが行える必要がある。また、フロントエンドにおける FPGA の放射線損傷 Single Event Upset(SEU) は、高輝度化において更に厳しいものと

16 1.3. 本論文の構成

なるのだが、フロントエンド回路の安定した運用を保障するため、自己修復できない FPGA の放射線損傷を外部から対応する必要がある (2.2.2.1 節参照)。以上の要請を満たすような制御システムをデザインすることが、本研究の目的である。具体的には、モジュールの考案や Cabling の策定などシステムをデザインし、制御システムの中心として機能する制御回路を開発し、本番での制御回路の運用を可能にすることを目指す。

### 1.3 本論文の構成

第2章では、Level-0 endcap muon trigger system について詳細に説明し、その中でフロントエンド側の要請を明示し、その要請を満たすようデザインした TGC エレクトロニクス制御システムの全体像を示す。第3章では、デザインした制御システムの中心的な役割を担う制御回路の設計概要と回路の設計、試作機製作について説明する。第4章では、制御回路試作機の機能実装と動作試験を行い、自分が開発実装した機能が自分の想定通り動いたことを述べる。第5章では、動作試験によって浮かび上がった試作機の改善点をまとめた後、第2試作機の製作について述べる。最後に、第6章では、本論文の結論と今後の展望を述べる。

# 第2章

# 高輝度 LHC-ATLAS 実験における TGC 検 出器エレクトロニクスシステム

本章では、本研究の対象である TGC 検出器のエレクトロニクスシステムについて説明する。また、TGC 検出器のエレクトロニクスシステムにおいて求められる機能を明確にし、制御系デザインの確立を 実施したことも説明する。

# 2.1 Level-0 endcap muon trigger system

TGC 検出器では ATLAS 検出器の Endcap 部をカバーし、飛来する Muon 粒子を検出し、その Hit 情報を Hardware 的に処理した後に全体の Level-0 trigger 処理システムに送る。本節は、TGC 検出器の Hit 情報を全体の Level-0 trigger 処理システムへ送るまでの、読み出し・トリガーエレクトロニクスシステム (Level-0 endcap muon trigger system)\*1について説明する。

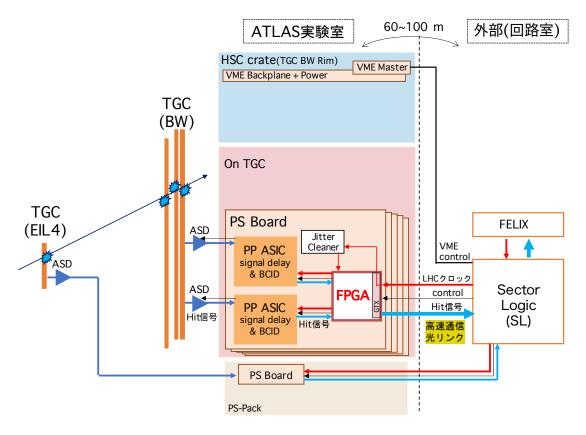

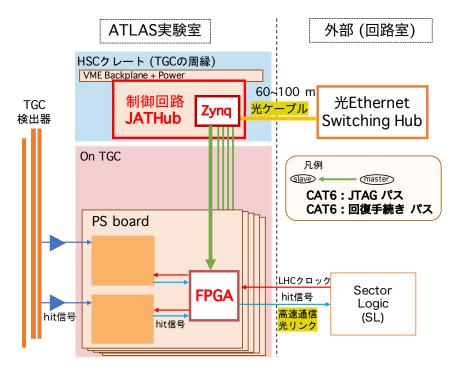

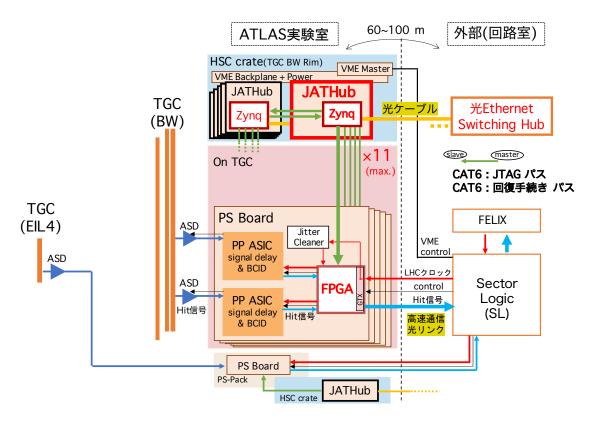

このシステムの全体像を図 2.1 に示す。まず、複数層の TGC 検出器で荷電粒子が検出された際、アナログ電流信号が出力される。TGC 検出器に取り付けられている ASD でその電流信号を電圧信号に変換増幅し、閾値電圧との比較を行い LVDS 信号として出力する (以降 "Hit 信号")。Hit 信号は TGC 検出器の円盤上に設置されている PS board に送られる。他の PS board に送られた Hit 信号とのタイミングのズレを考慮し、PS board 上の PP ASIC でタイミング調節が行われる。そして PS board 上の Field Programmable Gate Array(FPGA) から高速光通信を用いて、60~100 m 離れたバックエンド回路室の Sector Logic(SL) へ光ケーブルで全 Hit 信号が送られる。SL では、TGC 検出器の各地点から送られてきた Hit 信号を元に荷電粒子の横運動量と位置を算出し、L0 Trigger データを全体の Level-0 trigger system に渡す。また、SL では、FELIX から LHC クロックと L0A 信号が配布されるので、L0A 信号に従って Hit 情報を FELIX に読み出す。更に、SL から PS board へ光ケーブルを用いて LHC クロックの配布を行ったり、SL から PS board 上の register の操作を行える設計になっている。以降、詳細を述べる。

<sup>\*1</sup> 制御系は含まずに説明する

図 2.1 Level-0 endcap muon trigger system の全体概念図。

#### 2.1.1 TGC 検出器とフロントエンド機器の位置関係

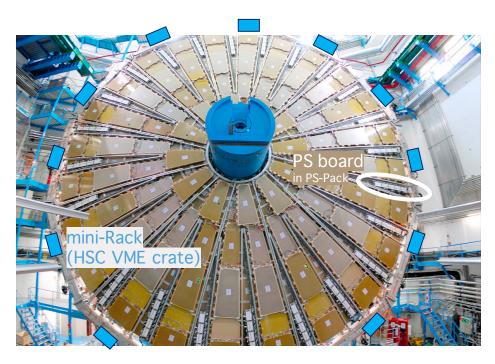

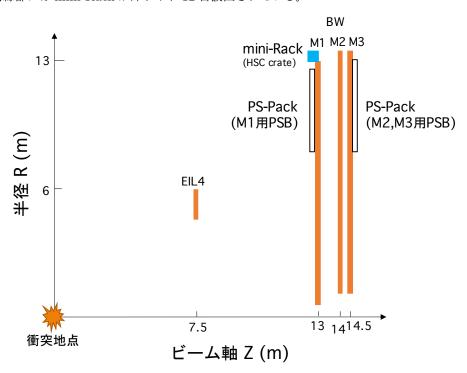

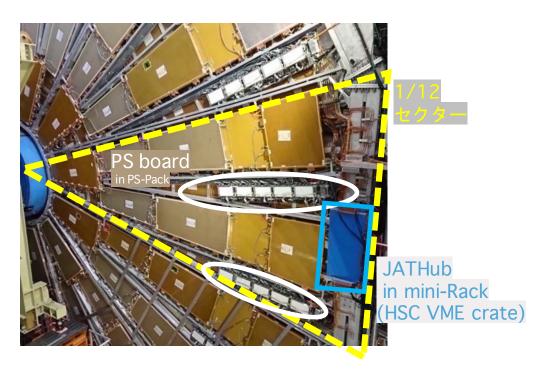

TGC 検出器の全体写真は図 2.2、TGC 検出器設置位置は図 2.3 にて示す。TGC 検出器は ATLAS 検出器の Endcap 部をカバーするようになっている。ATLAS 検出器の最外層には 3 層の円盤状の Big Wheel (BW) があり、衝突点に近い方から M1, M2, M3 と呼ばれている。内側には Endcap Inner (EIL4) が設置されている。外側の BW の直径は 25 m となっており、ビーム軸上の位置は衝突点から 13 m (M1)、14 m (M2)、14.5 m (M3) にある。内側の EIL4 は直径 12 m となっており、ビーム軸上の位置は衝突点から 7.5 m に設置されている。

図 2.2 に写っている検出器上に並べて設置された白い "PS-Pack" の中に後述する PS board がある。図 2.3 の M1、M3 の側面にある白い四角が、PS board が格納されている PS-Pack の設置位置である。また、図 2.2、図 2.3 の M1 の先端、つまり M1 の周縁部分には mini-Rack が片サイド 12 台設置されている。

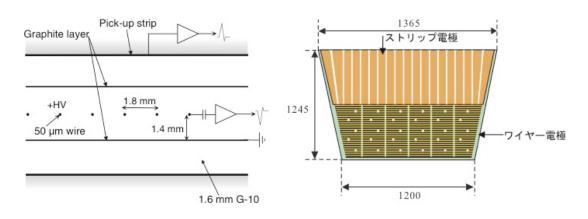

#### 2.1.2 TGC 検出器

TGC 検出器は、Multi-Wired Proportional Chamber (MWPC) 型のガス検出器である。TGC 検出器の断面図は図 2.4 の左図のようになっており、アノードワイヤーとピックアップストリップ電極と

図 2.2 TGC 検出器の正面写真 (M1)。検出器の隙間に並んだ PS-Pack に PS board が設置される。 M1 の周縁部には mini-Rack が片サイド 12 台設置されている。

図 2.3 TGC 検出器の側面図。PS board は PS-Pack の中に複数台 (2.3.2 節参照) 設置される。M1 の周縁部には mini-Rack が設置されており HSC VME crate が収納されている。

Graphite の接地層の構造となっている。アノードワイヤーと Graphite 接地層の間には  $+2.8~\rm kV$  の高電 圧がかかっている。また、このチェンバー内は電子増幅用  $\rm CO_2$  とクエンチャー用  $\rm n$ -ペンタンの混合ガス\*2が充填されている。

TGC 検出器に荷電粒子が通過した際、ガス分子が荷電粒子により電離される。電離した電子は、アノード・カソード間の印加電圧による電場に従って、アノードワイヤーの方向に移動する。アノードワイヤー近傍では、強い電場により、電離した電子の通過を引き金にガスの電離が発生し、電子雪崩が起きて、電子が増幅される。この時発生した正イオンが陰極に向けてドリフトしていく電流信号がアノードワイヤーで検出される。また、鏡像電荷がカソードストリップで検出される。

図 2.4 左:TGC 検出器の断面図、右:TGC 検出器の 1 チェンバー

図 2.4 の右図の通り、アノードワイヤーとピックアップストリップは直交して配置されているため、荷電粒子の位置を 2 次元的に読み出すことができる。この台形チェンバーの縁に ASD が設置されており、 ASD から Hit 信号が PS board へ読み出される。 TGC 検出器の BW や EIL4 は、図 2.4 の右図の台形チェンバーの集合体となっている。 ATLAS 実験室内での TGC 検出器のチャンネル数は全体で約 32 万である。

### 2.1.3 Amplifier Shaper Discriminator (ASD) ボード

ASD は、TGC 検出器のチェンバーから出力されるアナログ電流信号を電圧信号へ変換、増幅、整形した後、閾値電圧以上の電圧信号を PS board の PP ASIC へ渡す。これらの処理は図 2.5 の写真にある 4 つの ASD Application Specific Integrated Circuit (ASIC)\*³にて行われる。これらで TGC 検出器の 16 のチャンネル数をカバーする。PS board の PP ASIC との通信には、放射線などによるノイズに強く電力消費が少ない、Low Voltage Differential Signaling (LVDS) 通信を採用している。ATLAS 実験室内で実装される ASD は約 2 万台となる。

$<sup>^{*2}</sup>$  CO2: 55 %, n-pentane: 45 %

<sup>\*3</sup> ASIC とは特定の用途のために信号処理などを設計し、製造される集積回路である。

図 2.5 Amplifier Shaper Discriminator (ASD)

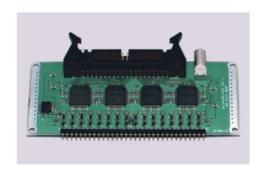

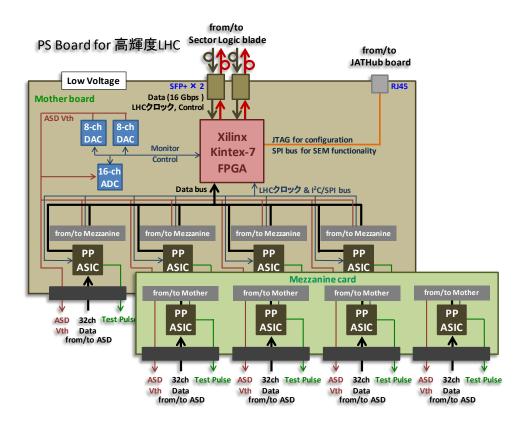

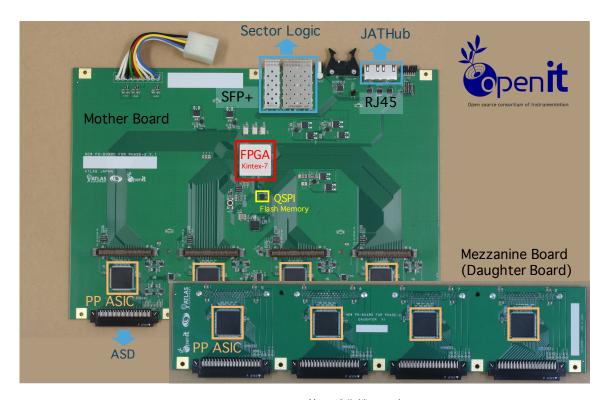

#### 2.1.4 PS board

PS board は、Patch-Panel ASIC (PP ASIC) と Field Programmable Gate Array (FPGA) の 2 種類の集積回路が搭載されており、ASD から受けた全 Hit 信号を "Hit Bitmap"としてバックエンド回路室の SL へ高速光通信を用いて送る。ここで、FPGA とは、ユーザーが何度でも configuration\*<sup>4</sup>でき、Firmware を編集して内部のデジタル回路を編集できる集積回路である。PS board に供給される電源は、PS board 駆動用 3.3 VD(デジタル) と、ASD との LVDS 通信に使用する +3 VA、-3 VA(アナログ) がある。また、M1 の PS-Pack にある PS board は、TGC 検出器 M1 をカバーし、M3 の PS-Pack にある PS board は、TGC 検出器 M2、M3 をカバーする。高輝度 LHC-ATLAS 実験室内で実装される PS board は合計で 1434 台である (小計は 2.3.2 節)。PS board の概念図は図 2.6 に示す。PS board の第 1 試作機の写真は図 2.7 に示す。

■PP ASIC ATLAS 検出器では各衝突事象毎に Bunch Crossing Identification(BCID) を割り振り、どの衝突事象でのデータであるかをラベル付けできるようにしている。そのため、各 Hit 信号を正しい BCID に振る必要がある。そしてその後、40 MHz で同期する回路にて信号が処理されていく。しかし、TGC 検出器のフロントエンドエレクトロニクスでは、衝突地点から荷電粒子が飛来した際、衝突点と検出器間の TOF の違いや、ASD と PS board 間などのケーブル長の違いにより、Hit 信号が PS board へ到達するタイミングが一致しない。そこで、PP ASIC では、LVDS 規格により ASD からの Hit 信号を受け取ると、Relayable Delay による Hit 信号のタイミング調節と、各 Hit 信号への BCID の割り振りが行われる。

LHC では 40 MHz の頻度で陽子を交差させているのだが、LHC 全システムで機器の動作を同期させる ために 40 MHz (25 ns)\* $^5$ の LHC クロックを生成し各システムに配布している。TGC 検出器のエレクトロニクスシステムでは、LHC クロックは、バックエンド回路室の SL から PS board の FPGA を経由して、PP ASIC まで送られてくる。PP ASIC では、この LHC クロックと Hit 信号が同期するように、Hit 信号に delay をかけてタイミング調節を行っている。具体的には、Hit 信号を受けるゲートが開くタイミングをチャンネル毎に 1 ns 以下の精度で微調節し、Hit 信号を LHC クロックの 1 波長分の長さに整える。

$<sup>^{*4}</sup>$  集積回路中の register を設定すること。

$<sup>^{*5}</sup>$  正確には  $40.079 \mathrm{MHz}$

図 2.6 PS board 概念図

図 2.7 PS board 第 1 試作機の写真

ここで、LHC クロックの位相は全 PS board にて十分小さな精度で揃っていなければならないのだが、 上記のタイミング微調節を行うべく、最低でも 1 ns 以下の精度で位相の一致が必要である。現行システム では、300 ps 程の精度で位相を一致させてシステムが動いた実績がある。

また、PP ASIC には Test Pulse 試験用の機能がある。PP ASIC の register を操作することで ASD に Test pulse trigger を送ることができ、Test Pulse を増幅し AC-Coupling を経て ASD に決まったタイミングでチャージ信号を入力することで、Level-0 endcap muon trigger system に試験的な Hit 信号を通す ことができる。

PP ASIC は PS board の mother board に 4 つ、mezzanine board に 4 つ、合計 8 つが設置されており、TGC 検出器の 128 チャンネルをカバーする。

■FPGA on PS board PP ASIC で調節された全 Hit 信号は、FPGA に内蔵されている高速シリアル通信対応の GTX tranceiver から、PS board 上の SFP 光 tranceiver を経由して光ケーブルを繋げて、1 lane につき 8 Gb/s の高速光通信で 60 - 100 m 先のバックエンド回路室にいる SL へ送られる。また、SL から PS board の FPGA へ、同じ高速光通信で、LHC クロックが配布されたり、FPGA の register を操作する信号が送られる。FPGA の register を操作することで、ASD の閾値電圧の操作や監視、PP ASIC の register 操作を行える。

PS board は FPGA を 1 つ搭載し、FPGA は Xilinx 社の Kintex-7\*6を使用している。高速光通信に対応する最新の確立された技術を活用するため、FPGA を使用する。

PS board には、ATLAS 実験全体で定められている放射線耐性の要求を満たした QSPI flash memory も載る。QSPI 上には、FPGA のデジタル回路を記述した Firmware が入った configuration file をプログラムして保持することができる。FPGA の configuration memory は Static Random Access Memory (SRAM) で実装されており、電源が切れると内部のデジタル回路は保存されない。そのため、FPGA の電源を入れ直したり、reconfiguration を行う際は、QSPI 上の file から Firmware を読み込み、FPGA に Firmware をプログラムしてデジタル回路を形成する。

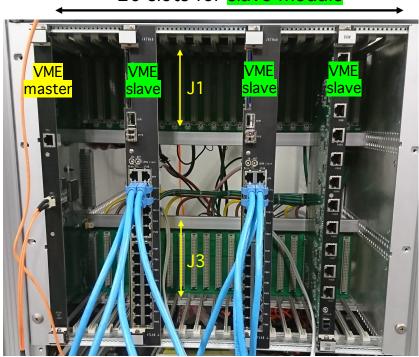

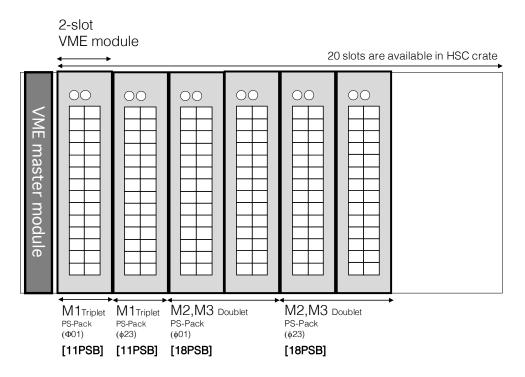

## 2.1.5 HSC (VME) crate

図 2.2 や図 2.3 に示す mini-Rack の中には図 2.8 のような VME crate が収納されており、VME master module と最大 20 枚の VME slave module が挿入できるようになっている。そして、VME master module が VME slave module に対して A24/D16 (AM=0x39) の register 操作を行える。Backplane は VME 規格の J1 とユーザー定義の J3 で構成されている。この VME crate は "HSC crate"と呼ばれている。この HSC crate には 3.3V の電源が供給されている。この Crate は現行システムでも使用\*7されている。高輝度 LHC-ATLAS 実験でも再利用するが詳細は後述する。

<sup>\*6</sup> 型番: XC7K325T-2FFG900C

<sup>\*&</sup>lt;sup>7</sup> 現行のシステムでは crate 内に HPT、SSW と呼ばれる 2 種類の module が実装されているため、"Hpt Ssw Crate(HSC) crate"と呼ばれている。

# 20 slots for slave module

図 2.8 mini-Rack 内にある HSC VME crate。Backplane は J1 と J3 の部分がある。一番左が VME master module で、J1 を通じて他の VME slave module の register 操作を行える。J3 から 3.3V の電源供給を行う。

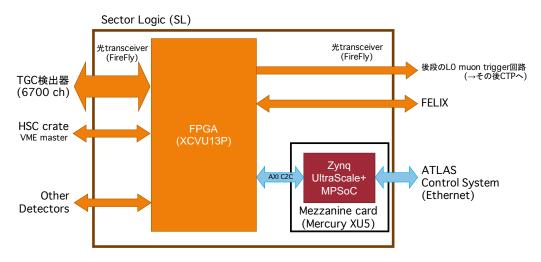

## 2.1.6 Sector Logic (SL)

SL の概念図を図 2.9 に示す。SL では、PS board から高速光通信で送られてきた TGC 検出器 BW の Hit 信号を使用して、Firmware による信号処理を行い、Muon 粒子の候補となり得る荷電粒子の飛跡を 再構成する。飛跡再構成を行う際、FPGA の RAM に予め TGC 検出器での Hit パターンを記録しておき、BW からの Hit 信号を照らし合わせて荷電粒子の飛跡を特定する手法を取っている。補助的な情報として、ATLAS 実験の endcap 部の muon に関わる他の検出器からの Hit 情報も加味して、飛来した荷電粒子の横運動量と位置などの Hit 情報が算出される。そして、後段の L0 muon trigger 回路へ Level-0 Trigger 情報を送る。

SL は FELIX から Level-0 Accept (L0A) 信号と LHC クロックを受け取り、PS board へ LHC クロックを配布し、L0A 信号に従って該当する BCID の Hit 情報を FELIX へ読み出す。

SL と HSC crate の VME master module を光ケーブルで接続し、SL から VME master module を高速光通信を使用して操作する。

SL は ATLAS 実験室から 60 - 100m 離れた回路室に全 48 台設置されている。ATLAS 実験室は LHC 加速器運転中において放射線環境である一方、この回路室は、実験室と回路室の間に用意されたケーブル 用の穴は小さく放射線対策が施されているので、LHC 加速器運転中でもアクセスできる。

図 2.9 Sector Logic(SL) の概念図。SL と他回路との接続の様子を示す。

SL には、Xilinx 社の FPGA Virtex UltraScale+\*8を搭載し大規模処理を可能にした。また、ボード上のコントロールを行うため、Xilinx 社の Zynq UltraScale+ MPSoC\*9を使用する。Zynq UltraScale+ MPSoC は Mezzanine card となっている既存の商品を使用する。SL の試作機は 2020 年 12 月現在製作段階にある。

### 2.1.7 Front-End Llnk eXchange(FELIX)

CTP にて全体の Level-0 trigger 処理が行われると、どの BCID の Hit 情報を解析データとして保存するか検出器全体に教えるための Level-0 Accept (LOA) 信号が発行される。FELIX は、CTP から送られる LOA 信号と LHC クロックを ATLAS 検出器全体に配布する。そして、ATLAS 検出器全体から LOA 信号で許可された BCID の Hit 情報が FELIX へ読み出されるので、FELIX はこれを更に後段へ送る。Software による事象選別が行われる後段の回路へは、1 MHz の頻度で Hit 情報が送られる。

#### 2.1.8 アップグレードによる Performance の向上

高輝度 LHC-ATLAS 実験の Trigger and DAQ system 全体では、エレクトロニクスを一新したことにより、以下 2 つの観点から Trigger 性能の向上を実現する。

- 最新技術の導入により、通信性能を向上させたり、初段 Trigger の処理時間 (レイテンシー) を伸ばす。それにより、Hardware ベースの初段 Trigger で、Software ベースの後段 Trigger と同等レベルの処理が行えるようになり、複雑な Trigger アルゴリズムを実装可能となる。そして、ターゲットとしている物理事象を更に記録することができるようになる。

- LHC では多様な物理過程を解析の対象としている。そこで、現行システムより 10 倍の頻度で Trigger を発行できるようにし、読み出し頻度を向上させる。それにより、可能な限り多くの興味

<sup>\*8</sup> 型番: XCVU9P-1FLGA2577E

<sup>\*9</sup> 型番: Zynq ZU+ C784

のある物理事象データを残すことができるようになる。

レイテンシーと読み出し頻度の向上は表 2.1 に示す通りである。尚、'初段読み出し頻度' は初段 Trigger後 DAQ システムに読み出される頻度を示し、'後段読み出し頻度' は Permanent Storage に読み出される頻度を示す。

| 実験               | レイテンシー ( <i>μs</i> ) | 初段読み出し頻度 (kHz) | 後段読み出し頻度 (kHz) |

|------------------|----------------------|----------------|----------------|

| 高輝度 LHC-ATLAS 実験 | 10                   | 1000           | 10             |

| Run3(現行) 実験      | 2.5                  | 100            | 1              |

表 2.1 Trigger and DAQ system のレイテンシーと読み出し頻度

そして、Trigger 性能を向上させることにより、図 2.10 のように、 $P_T$  閾値を低く抑えることが可能となる。図 2.10 はシミュレーションにより得られた Trigger 性能向上の結果の一例である。横軸は Single lepton の  $P_T$  閾値を示し、縦軸は Trigger 後取得できる Single lepton の量を Trigger をかけない場合と比較した割合 (Acceptance) で示している。尚、凡例はどの物理事象に由来する Single lepton であるかを示す。 Trigger 性能が不変の場合、 $P_T$  閾値は 50 GeV に上がってしまうが、本アップグレードにより  $P_T$  閾値は 20 GeV にまで抑えられ、Acceptance が向上する。

図 2.10 Trigger 性能が向上することにより、物理 Acceptance が向上する例。

Level-0 endcap muon trigger system では、高速データ転送技術を用いて PS board から全 Hit 信号を SL へ送り、そして SL にて一手に Endcap 部の Level-0 muon trigger 処理を行うという機構にすること で、上記 Trigger 性能の向上に貢献している。具体的には、PS board から全 Hit 信号を SL に送る際、性能が上がった最新の FPGA や高速光通信を利用することで、バンド幅による通信制限をかけないように

している。また、PS board ではなく、SL にて Trigger 処理を行うことで、Trigger 処理回路の修正や調節がしやすくなる。そして、SL に読み出し用の大型 Buffer を設けることで、LOA 信号が来るまで十分な量の読み出しデータを保存できる。

### 2.2 フロントエンド側エレクトロニクスシステムの要請

Level-0 endcap muon trigger system のフロントエンド側にて FPGA が新設される。このエレクトロニクスシステムを高い信頼性を持たせて運転させるためには、ATLAS 実験室内に設置される FPGA を安定して稼働させる必要がある。そのため、Level-0 endcap muon trigger system は、フロントエンドのFPGA の安定した動作を確保するために、外部から以下 2 点の制御が行えることを要請する。

- ATLAS 実験室内の FPGA に対して遠隔で configuration を実行する

- フロントエンドに堅牢で信頼性の高いシステムを構築する

#### 2.2.1 ATLAS 実験室内の FPGA に対して遠隔で configuration を実行

PS board は図 2.13 の PS-Pack に設置される。よって、ATLAS 実験室内に設置される FPGA は、物理的に人のアクセスが容易ではない場所に存在することになる。一般的に FPGA を configuration し内部 にデジタル回路を実装するためには、ホスト PC を FPGA の近くまで持っていき、短い JTAG ケーブル でホスト PC と FPGA を接続しなければならない。しかし、PS board の FPGA\*10では、一般的な方法で configuration を行うことが実質的に不可能である。そのため、ATLAS 実験室外から遠隔で PS boardの FPGA を configuration し、FPGA へ Firmware\*11をプログラム、debug できる仕組みが必要である。

#### 2.2.2 フロントエンドに堅牢で信頼性の高いシステムを構築

#### 2.2.2.1 ATLAS 実験室内の放射線対策

LHC 運転中は ATLAS 実験室内は高い放射線環境となる。TGC 検出器の位置では、1 衝突 (25 ns) 毎に 300~500 回の Hit が検出される程荷電粒子が飛来してくる。一方、ASIC や FPGA などの集積回路は、イオン化を行う放射線によって内部 register や memory の bit が反転してしまう Single Event Upset (SEU) 事象や、多量の放射線入射により永久的に素子が機能しなくなる損傷など、放射線損傷を被る場合がある。一般に ASIC は放射線に強いと知られているが、フロントエンドに置かれた Level-0 endcap muon trigger system のエレクトロニクスである ASD、PS board は、この放射線損傷への対策が必要である。

ASD ASIC は放射線照射試験にて耐久性に問題がないことを確認した。PS board の PP ASIC に関しては、高輝度 LHC-ATLAS 実験における PS board 設置位置の想定放射線レベル (6 Gy) に安全係数 4.5

<sup>\*10</sup> デジタル回路の編集の自由度を担保する必要がある

<sup>\*&</sup>lt;sup>11</sup> FPGA に実装するデジタル回路を記述する回路情報体を指す言葉。TGC 検出器エレクトロニクス開発グループでは Xilinx 社の Vivado ソフトウェアで Hardware Design Language からデジタル回路を記述し Firmware のコンパイルを行っている。

をかけた 27 Gy の中でも安定して稼働するよう耐性のある素子を選択している。試作 PP ASIC による放射線照射試験を行った際は 100 Gy まで異常検知されなかった。そのため、両 ASIC ともに、永久的な素子の損傷に関しての対策は問題ない。Level-0 endcap muon trigger の trigger logic では、荷電粒子の飛跡再構成を行う際、各 TGC 検出器での Hit 信号のコインシデンスを取り検出位置を判断する。そのため、ASD ASIC や PP ASIC での SEU 事象により予期せぬデータが数 bit のみ SL に送られても、SL では問題なく飛跡再構成を行うことが可能である。

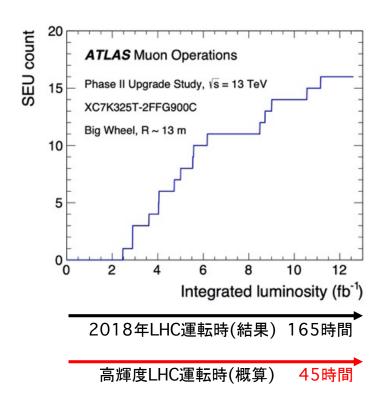

PS board の FPGA は、FPGA の configuration memory で SEU が発生した場合、最悪その PS board から出力される全データが途切れる可能性もある。そのため、FPGA 内の SEU を監視し、即座に回復できる仕組みが必須となる。Xilinx は FPGA 上の SEU などの放射線損傷を自動回復できるロジックパッケージ (Intellectual Property(IP))、"Soft Error Mitigation (SEM)" IP core [6] を提供しており、PS board の FPGA にも実装する。この SEM は内部クロックを使用して常時 FPGA configuration memory の bit flip を監視しており、FPGA 内の 1 つの register で SEU が発生した場合、自動で該当の bit を回復させる。だが、例えば FPGA に対して放射線が斜め方向から照射された時など、同時に 2 つ以上の連続する bit で SEU が発生する場合、SEM でも発生したビット反転を回復できない。このような"SEM でも回復不可能な SEU 事象"が発生した時に備え、外部回路で該当する事象を常に監視し、外部から FPGA を reconfiguration する仕掛けが必要となる。また、SL と PS board 間の高速光通信のパスから FPGA の reconfiguration をトリガーすることは、Kintex-7 の仕様上行えないため、別のパスから reconfiguration のトリガーを行う必要がある。

2018 年の ATLAS 実験 Run2 運転の際、高輝度 LHC-ATLAS 実験用の PS board 第 0 試作機\*<sup>12</sup>を製作し、PS board 上の FPGA における SEU の発生頻度を調査した。PS board 第 0 試作機は本番と同じ型番の FPGA を使用し、ATLAS 実験室内の TGC 検出器上に設置した。結果は図 2.11 の通り、積分 Luminosity 12.6fb<sup>-1</sup> で合計 16 回の SEU を検出した [7]。高輝度 LHC 実験での瞬間最高 Luminosity は現行約 3 倍の 5~7.5×10<sup>34</sup>cm<sup>-1</sup>s<sup>-1</sup> であるため、0.8fb<sup>-1</sup> あたりに 1 回の SEU が発生するということは、高輝度 LHC-ATLAS 実験における 1 台の PS board の FPGA の SEU 発生頻度は 3 時間に 1 回となる。従って、ATLAS 実験室内全体の 1434 台の PS board の内、10 秒に 1 回、どれかの PS board にて SEU 事象が発生していることになる。

2018 年の ATLAS 実験での SEU 頻度調査試験の際、全ての SEU 事象は SEM によって修正された。 しかし、"自動回復不可能な SEU 事象 (UnRecoverable Error (URE))"は観測されなかった。

FPGA Virtex-5 に中性子照射試験を行った実験では、URE 事象が観測され、SEU 事象と URE 事象の比  $^{\sim}$ 300SEUs/URE が得られた [8]。この比と 2018 年の SEU 頻度調査試験から、高輝度 LHC 実験における PS board 上の FPGA の URE 発生頻度を概算した。1 台の FPGA に対して URE が約 900 時間 (約 37 日) に 1 回、ATLAS 実験室内のどこかの FPGA に対して URE が約 40 分に 1 回発生することが予測できる (詳細は B 章)。

従って、Level-0 endcap muon trigger system の安定稼働のためには、"回復不可能な SEU 事象 (URE)" への対処が必須となる。

<sup>\*12</sup> 第1試作機との違いは本研究で開発している制御回路への接続口が無い点。

図 2.11 SEU 回数試験の結果 [7] 2018 年の試験。合計 16 回の SEU が発生し、全 SEU 事象は SEM にて修正された。

#### 2.2.2.2 高速光通信の安定的な確立

PS board の FPGA に組み込まれている GTX tranceiver は、PS board に供給される LHC クロックをソースクロックとして稼働している。リンクが途絶えた時、光通信外部からリンク再確立の手続きをトリガーできる仕組みを作っておくことが必須である。そのため、外部から高速光通信をリセットし、リンクを再確立する機能が必要である。

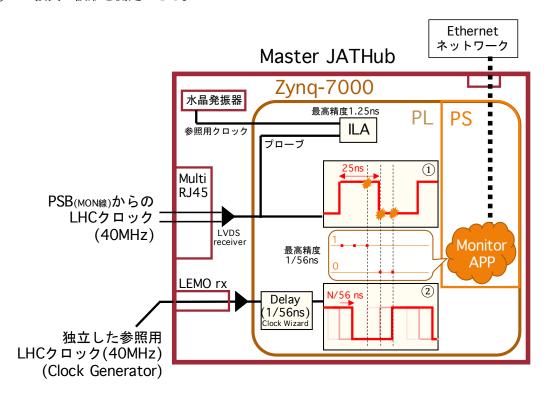

#### 2.2.2.3 LHC クロック位相のモニター

PS board は、BCID を振る際に LHC クロックを使用しており、その LHC クロックの位相が他 PS board と O(100) ps の精度で揃って供給されていることを前提として機能する。そのため、PS board へ配布された LHC クロックを O(100) ps の精度でモニターする必要がある。また、複数の PS board において使用されている各 LHC クロックを同時に比較しモニターできる仕組みも必要となる。

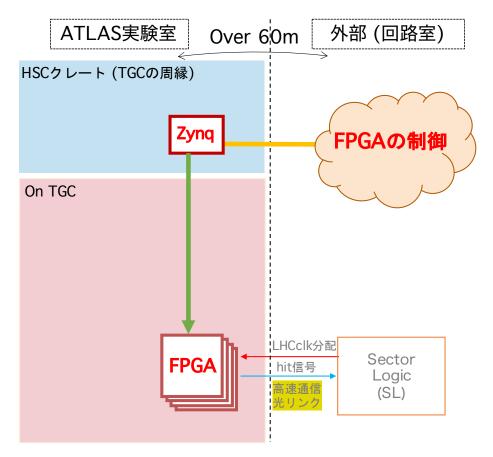

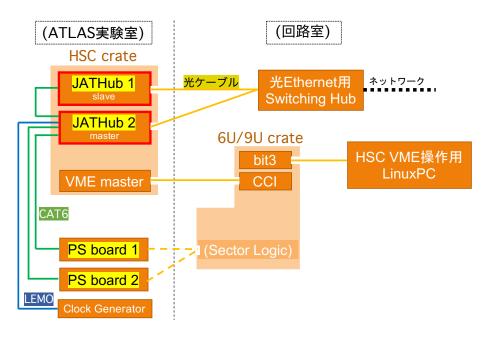

図 2.12 制御系の概念。Zynq を搭載した制御回路を VME crate に挿入し、中継地点として、PS board を制御する。

### 2.3 制御系の確立

#### 2.3.1 制御系の概要

2.2 節の要請を満たすように、本研究では制御系をデザインした。最適化の結果、TGC 検出器フロントエンドエレクトロニクスでは、図 2.12 のように、FPGA とプロセッサーを組み合わせた System-on-a-Chip(SoC) デバイスを搭載した制御回路を中継地点におき、PS board の FPGA を外部からスローコントロール $^{*13}$ で監視、制御できる制御システムを導入することにした。また、実験中と実験外では以下のように用途を使い分けることで、ハイブリッドな制御システムとした。

- 実験時間外: Linux のソフトウェアアプリケーションにより、実験時間外にて必要な制御のハブとして稼働すること。

- 実験中: FPGA の Firmware ロジックにより、実験中に必要な機能のハブとして稼働すること。

この制御系に導入される制御回路には、SoC デバイスとして Xilinx 社の Zynq-7000 を搭載した。Zynq

<sup>\*13</sup> LHC クロックと同期しないで動作するコントロール。

SoC デバイスを採用した理由として主に以下3点が上げられる。

- ◆ 4.3.1 節にて登場する Xilinx Virtual Cable という Xilinx 社開発の Zynq を使った既存技術をこの 制御系に応用すること

- Zyng のプロセッサーで走る Linux を用いることで、自作アプリによる自由な操作、監視を行うこと

- Zynqの FPGA により、要求される信号処理を自由度をもたせて実装すること

また、この制御回路の設置位置として、図 2.13 の mini-Rack にある HSC VME crate を活用した。 そして、本研究の研究開発の対象である、この制御回路は、**JTAG Assistance Hub (JATHub)**\*<sup>14</sup>と名付けられた。第 3 章以降にて、JATHub の詳細と JATHub 試作機の動作試験について述べる。

#### 2.3.2 制御系回路の必要数

TGC 検出器の円盤を 1/12 した扇形を、1/12 セクターと呼ぶ。図 2.13 の黄色扇形で囲まれた区域が 1/12 セクターである。この 1/12 セクター単位で、制御系にある回路の必要数を表 2.2 に示す。TGC 検出器は円周座標を  $\phi$  で表しており、1/12 セクターに 2 つある PS-Pack は  $\phi 0, 1, \phi 2, 3$  と分けて呼ぶ。(この制御系を含めた、TGC 検出器エレクトロニクスシステムのスケールは図 A.1 を参照。)

また、ATLAS 実験室内全体の必要数を表 2.3 に示す。

| 回路       | 設置場所                      | 必要台数 | CAT6 本数 |

|----------|---------------------------|------|---------|

| PS board | PS-Pack (M1 $\phi$ 0, 1)  | 11 台 | 22 本    |

|          | PS-Pack (M1 $\phi 2, 3$ ) | 11 台 | 22 本    |

|          | PS-Pack (M3 $\phi$ 0, 1)  | 18 台 | 36 本    |

|          | PS-Pack (M3 $\phi$ 2,3)   | 18 台 | 36 本    |

|          | 必要数合計                     | 58 台 | 116 本   |

| JATHub   | HSC crate(mini-Rack)      | 6 台  | 12 本    |

表 2.2 制御系にある回路の必要数 (BW1/12 セクター単位)

<sup>\*14</sup> JTAG 通信と補助線によるフロントエンド電子回路を支える Hub module のため、この名前にした。Zynq は Edge Computing として自動車の自動運転技術にも貢献しているデバイスだが、その自動運転技術は Advanced Driver-Assistance Systems(ADAS) と呼ばれている。JATHub の "Assistance"はこの名称を参考にした。

32 2.3. 制御系の確立

図 2.13 TGC 検出器の写真 (BW1/12 セクター)。PS-Pack の列に PS board が設置される。mini-Rack 内の VME crate に制御回路 (JATHub) が設置される。1/12 セクターにつき、4 つの PS-Rack の列と 1 つの青 Rack が設置されている。

表 2.3 制御系にある回路の必要数 (ATLAS 実験室全体)

| 回路       | 設置場所                     | 必要台数                      |

|----------|--------------------------|---------------------------|

| PS board | PS-Pack (Big Wheel)      | $58 \times 12 \times 2$ 台 |

|          | PS-Pack (EIL4)           | $21 \times 2$ 台           |

|          | 必要数合計                    | 1434 台                    |

| JATHub   | HSC crate (BW mini-Rack) | $6 \times 12 \times 2$ 台  |

|          | HSC crate (EIL4 用)       | $2 \times 2$ 台            |

|          | 必要数合計                    | 148 台                     |

# 第3章

# 制御回路 JTAG Assistance Hub (JATHub)

最初に 2.2 節で述べられた TGC 検出器フロントエンドエレクトロニクスからの要請を満たす制御システムとその中心で機能するモジュール JTAG Assistance Hub (JATHub) の概念設計を決めた。そして、概念設計に沿ってハードウェアの設計を行い、試作機を製作した。その後、JATHub 試作機で機能を実装し、動作試験を行った。本章では、JATHub の概念設計と、JATHub 試作機の製作について述べていく。なお、本 JATHub 開発研究は Open-it プロジェクト [9] 支援のもとで進められている。

## 3.1 概念設計

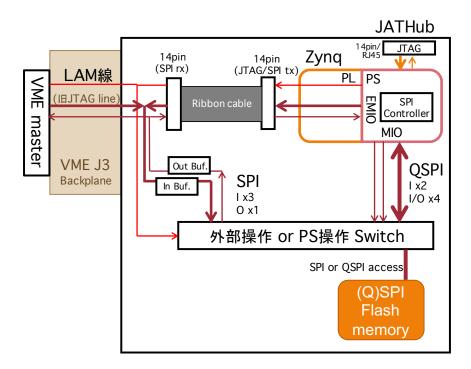

JATHub は外部とネットワークで通信し、複数台の PS board と接続して、各 PS board の FPGA を操作・モニターする。また、JATHub には、プロセッサーと FPGA を組み合わせた Xilinx 社製の Zynq SoC デバイスをメインドライバーとして搭載する。 Zynq は、プロセッサー部分である Processing System(PS) と、FPGA 部分である Programmable Logic(PL, FPGA 部分) で構成されている。この CPU + FPGA の構造が JATHub の必要な機能を実装する上で最適であった。図 3.1 は JATHub を使用した制御システムについて簡易的に示している。

本節では、JATHub の概念設計として、'JATHub に必要な機能の詳細'と 'ATLAS 実験室に実装する上で必要なハードウェア設計への要請'を説明していく。

#### 3.1.1 必要な機能

本節では、2.2 節の要請を満たす制御システムを動かす上で、JATHub に必要な機能を述べる

#### 3.1.1.1 光イーサネット通信

JATHub は Zynq のプロセッサー部分である PS で Linux を起動し、ATLAS 実験室外部と Ethernet 通信を確立し、PS board の制御とモニターを行う。そこで、JATHub は回路室の JATHub 用 Switching Hub と有線で接続して、Switching Hub を介した外部との Ethernet 通信を確立する。このパスを実現するには、JATHub と回路室の Switching Hub の間 約 60 - 100m を有線で接続させる必要がある。また、ATLAS 実験室と回路室を有線で繋ぐ際、回路室を放射線区域外にすべく実験室と回路室の間の穴は最小

34 3.1. 概念設計

図 3.1 JATHub の設計概要図。Zynq をメインドライバーとして、Linux を走らせ、複数の PS board の FPGA を操作・モニターする。

限にするため、幅を取らないケーブルを使用する必要がある。従って、Ethernet 通信用のケーブルには、一般的によく使用させる Copper(LAN) ケーブルではなく、長距離でも安定して高速通信が行え、且つ幅を取らない光ケーブルを使用する。

そのため、RJ45 jack や Ethernet 用 PHY chip、Copper ケーブルを使用した従来の Ethernet 通信方法 は本番環境では使用できないので、JATHub は、光ケーブルで回路室と接続し、光信号によって Ethernet 通信を確立する機能が必要である。

#### 3.1.1.2 JTAG 通信による Slave module の制御

PS board に搭載されている FPGA Kintex-7 は内部のデジタル回路\*<sup>1</sup>を何度でもユーザーが書き直すことができる。しかし、一般的に Kintex-7 へ Firmware を書き込むためには、書き込み用のアプリケーションが走っている Host PC を Kintex-7 の近くまで持っていき、JTAG4 線用の短い Copper ケーブルで Host PC と Kintex-7 を接続させる必要がある。

2.2 節でも示した通り、PS board は TGC 検出器上に設置されており、実験外時間であっても実質的に アクセスできない場所に置かれている。よって、JATHub は、PS board と Copper ケーブルで接続し、 JTAG 通信により PS board の Kintex-7 内のデジタル回路を書き込む機能が必要である。また、複数の PS board の Kintex-7 を一同に操作するハブ機能も必要である。

さらに、同じ HSC VME crate 内の隣の JATHub の Zynq も外部から configuration を行う必要があるので、相互的に master JATHub から slave JATHub へ JTAG 通信する機能が必要である。

<sup>\*1 &#</sup>x27;論理回路' とも言う

#### 3.1.1.3 PS board で自己修復不可能な SEU 事象が発生した際の対処

2.2 節でも説明した通り、高輝度 LHC-ATLAS 実験では、PS board に FPGA を新設するため、FPGA Kintex-7 の放射線損傷へ対処する必要がある。特に注意すべき放射線損傷は、内部 register のフリップさせる Single Event Upset (SEU) 事象である。通常、PS board 上の Kintex-7 は、内部 register の 1 つで SEU 事象が発生しても、Xilinx が提供する Soft Error Mitigation (SEM) により自動修復する。しかし、たまに隣合う 2 個以上の内部 register が同時に SEU を起こした時など、フリップレジスタを修復できない状態に陥ることがある。この "回復不可能な SEU 事象"が発生した場合、外部から Kintex-7 のリセットを掛ける必要がある。また、PS board は全 Hit 信号を SL へ送るデータパスとしての役割があるため、Kintex-7 にて回復不可能な SEU 事象が発生したら自動的にリセットを行う必要がある。本論文では、この対処を "Recovery 手続き"と称する。

そこで、JATHub は PS board と Copper ケーブルで接続し、PS board を常時監視する。そして、Kintex-7 内の自動回復不可能な SEU 事象を検知し、自動的にリセット信号を送り外部から Kintex-7 の機能を回復させるという Recovery 手続き機能が必要である。

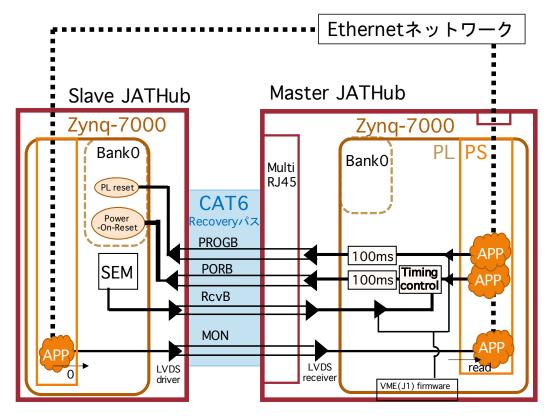

#### 3.1.1.4 隣の JATHub で自己修復不可能な SEU 事象が発生した際の対処

PS board 上の Kintex-7 と同様に、JATHub に搭載される Zynq SoC に関しても、放射線損傷への対策が必要である。FPGA 領域である PL では、同様に SEM 機能が働いており、ほとんどの SEU 事象が自動修復される。しかし、プロセッサー領域である PS では、SEU 事象への対策が存在せず、SEU 事象が起きたらプロセッサーのクラッシュが発生する。JATHub の設置位置において、1 台の Zynq の PS がクラッシュする頻度は 2 時間に 1 回程度になると算出されている [10]。 Zynq SoC では PS と PL の動作は電力系統も含めて独立しているため、PS がクラッシュしても、PL は動き続けることができる。また、JATHub はデータパスに関わっていないため、高輝度 LHC-ATLAS 実験中は、PL が機能している限り、直ぐに PS の回復を行う必要はない。そのため、JATHub は PL で回復不可能な SEU 事象が起きた時のみ、外部から Zyng の再起動を行ってもらう必要がある。

そこで、同じ HSC VME crate 内の JATHub と相互的に Recovery 手続きを行えるようにし、隣の JATHub 上の Zynq PL で自動回復不可能な SEU 事象が起きた時のみ、JATHub が隣の JATHub へ Recovery 手続きを行う機能が必要である。尚、PL の configuration は、Zynq の起動シークエンスの中に 含まれているため、PL のみを reconfiguration することはできず、Zynq の再起動を行う必要がある。

また、高輝度 LHC-ATLAS 実験中、JATHub は PL のみ使用できるため、Slave module の Recovery 手続き機能は PL の Firmware 内で完結させる。そして実験中 JATHub の機能は Slave modules の Recovery 手続きのみに制限する。

#### 3.1.1.5 LHC クロック位相のモニター

LHC クロックの位相は、ATLAS 実験室内の全ての PS board にて O(100) ps の精度で一致している必要がある。LHC クロックは回路室の SL から高速光通信の 8b/10b プロトコルでコーディングされて PS board へ届けられる。そこで、ケーブルの長さ等の要因で、個々の PS board にて LHC クロックの位相は変位する。

36 3.1. 概念設計

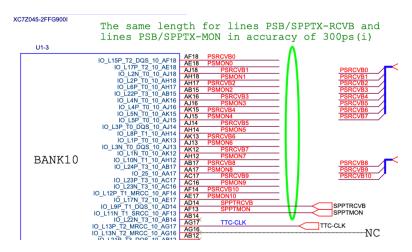

そこで、JATHub は PS board に供給された LHC クロックの位相が ATLAS 実験室内全体で一致していること確かめるために、25 ns(40.079 MHz) の LHC クロックの位相を O(100) ps の精度でモニターする機能が必要である。また、複数の PS board と JATHub の間は、JATHub の PCB レイアウトも含めて等長配線にし、LHC クロックの伝送距離を全線にて揃える必要がある。

#### 3.1.1.6 冗長性のある BOOT システム

JATHub の Zynq は常に再起動が行える状態でいるのが必須で、有事の際にも予備の BOOT システム によって再起動が行える必要がある。

そこで、JATHub は、複数の Boot ファイルを回路上の flash memory に用意し、ある Boot ファイル が放射線損傷を受けても、Zynq が有効な Boot ファイルを選択できるような、冗長性のある Boot システムが必要である。

#### 3.1.2 ATLAS 実験室内の設備との親和性に関する考察

ATLAS 実験室では、Run3(2021-2024) 運転が終了する翌年の 2025 年から、高輝度 LHC-ATLAS 実験の準備が始まるが、そこで効率の良い実験装置の実装が求められている。新しい機材を実装するにしても、一から設備を作り変えるよりも、現行のシステムの設備を再利用する方が、コストも時間も削減できる。本節では、そういった観点から ATLAS 実験室の現行システムの設備を踏まえて JATHub の設計を考察する。

#### 3.1.2.1 HSC (VME) crate の活用

TGC 検出器の現行システムでは、Hit 信号は PS board でコインシデンスを取り HSC crate 内の module に送られる。HSC 内の module は、読み出しデータの buffering とコインシデンスを取る信号処理を行い、回路室にコインシデンスを取ったデータや trigger された読み出しデータを送る。しかし、高輝度 LHC-ATLAS 実験における TGC 検出器のフロントエンドエレクトロニクスでは、全 Hit 信号を PS board が回路室へ直接送るため、この HSC crate が空く。

そこで、この HSC crate に JATHub を置くことで、フロントエンドエレクトロニクスの制御システムを構築した。HSC crate に JATHub を実装する利点について以下の要点が上げられる。

- LHC 運転休止中 ATLAS 実験室に入った際、HSC crate は人が簡単にアクセスできる位置に設置されているため、簡単に crate 内の module を交換できる。

- HSC crate は、衝突点からも遠い位置にある。そのため、crate 内の module の放射線損傷のリスクを軽減できる。

- HSC crate 内の module と PS board は、最大 15m の Copper ケーブル (Category-6 (CAT6) ケーブル) で安定して接続できる距離にある。

上記の点を踏まえて、JATHub が HSC crate に実装できるようハードウェアを設計した。図 2.8 と図 3.2 のように、この HSC crate は縦 9U、奥行き 16 cm の大きさで、VME master module と 20 slots 分の VME slave module が挿入できる構造になっている。また、VME backplane の J1 には、VME 規格

の信号線がある。VME backplane の J3 には、電源供給線と JTAG 通信線、slave module 個別に操作できる信号線がある。JATHub は HSC crate の J3 から電源供給を行う。

#### 3.1.2.2 ケーブルの再利用

TGC 検出器の現行システムにおいて、最大  $15m^{*2}$ の CAT6 ケーブルを使用している。

高輝度 LHC-ATLAS 実験における TGC 検出器制御システムでは、CAT6 ケーブルは再利用して JATHub と PS board の接続に使用する。なお、光ケーブルは新設する。

現行システムの CAT6 ケーブルの本数を踏まえて、現行システムの CAT6 ケーブルを取り外さずに再利用して JATHub と PS board を実装できるようにした。高輝度 LHC-ATLAS 実験において、2.3.2 節 の必要数をカバーすること、JATHub, PS board 間は 8 対 16 線の LVDS 通信を行えるのが望ましいこと も、JATHub 設計に加味した。その結果、JATHub は最大 11 枚の PS board と接続し、各 PS board に 対して 2 本の CAT6 ケーブル (4 対 8 線 x2) を使用する設計にした。加えて、1/12 セクター毎に 1 つの HSC crate が置かれているので、図 3.2 のように、その中に 6 台の JATHub を実装して、1/12 セクター内全ての PS board を操作できるように設計した。現行システムでは 1/12 sector 毎に 122 本の CAT6 ケーブルを使用しており、高輝度 LHC-ATLAS 実験では JATHub, PS board 間にて 116 本の CAT6 ケーブルを使用する予定となっている。

JATHub と PS board の配線図は C 章にて示す。

図 3.2 HSC crate 内の JATHub の実装。VME 規格の 20slots 中、各 JATHub は 2slots を使用し、12 slots 分 6 台の JATHub で 1/12 sector の PS board を制御する。

$<sup>^{*2}</sup>$  M1 用 PS board へは 10m、M2, M3 用 PS board へは 15m の CAT6 ケーブルを使用している。

38 3.1. 概念設計

#### 3.1.2.3 EIL4 区域への JATHub 実装

EIL4 区域の TGC 検出器上に PS-Pack が設置され、EIL4 用 PS board はその PS-Pack に収納される。また、30 m 程離れた場所に EIL4 用の HSC crate が設置されている。JATHub は EIL4 用の HSC crate にも挿入し、30 m の CAT6 ケーブルを使って、EIL4 用 PS board に接続する。

### 3.1.3 ハードウェア設計への要請

制御系の中心的回路である JATHub の必要な機能を思案し、ATLAS 実験室内の設備を考察して、TGC 検出器エレクトロニクスの制御システムの最終設計を図 3.3 のように決めた。その上で、JATHub のハードウェア設計に対して、以下の要請を取り決めた。

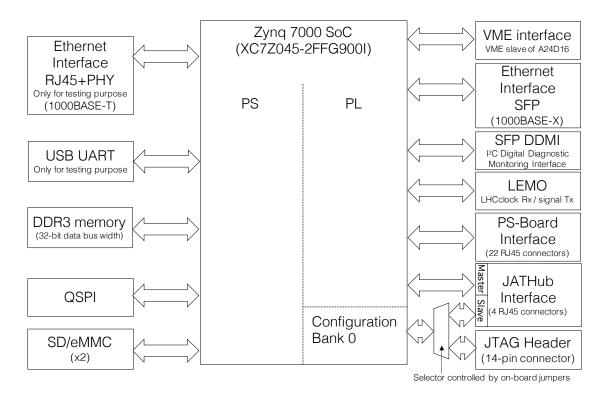

- Arm Cortex-A9 プロセッサーと Kintex-7 FPGA を組み合わせて高速光通信に対応する GTX transceiver も載せた Zynq SoC デバイス (Zynq-7000 シリーズ中の Zynq-7045 型) を搭載すること。

- 光ケーブルによる回路室との光通信に対応するため、光信号と電気信号を相互に変換する SFP (Small Form-factor Pluggable) 光 transceiver をインターフェイスとして使用すること。

- SFP から Zynq の GTX transceiver に伸びる差動線 (+, -) は等長配線であること。

- 最大 11 枚の PS board に対して、CAT6 ケーブルで接続し、JTAG 通信と Recovery 手続きと LHC クロックモニターができるように、RJ45 multijack をインターフェイスとして使用すること。更に、各 PS board に対して、2 本の CAT6 ケーブルを使用すること (JTAG 通信に 1 本、Recovery 手続きとモニターに 1 本)。

- LHC クロック位相のモニターのために、O(100) ps の精度で PCB レイアウトの等長が保障されていること。

- 隣の JATHub1 台に対して、CAT6 ケーブルで接続し、JTAG 通信と Recovery 手続きができるように、RJ45 multijack をインターフェイスとして使用すること。こちらも JTAG パス用、Recovery パス用に 2本の CAT6 ケーブルを使用すること。

- Slave module の reset 操作に関して、active low の reset 信号線を設けて、一定の信号幅の 0 信号 を受信することで slave module が reset されるような仕掛けを作ること。

- 各 PS board から送られる LHC クロックの位相をモニターするにあたって、参照比較用の独立した LHC クロックを取り入れるために、LEMO をインターフェイスとして使用すること。

- PS board からの信号線は等長配線にすること。CAT6 ケーブルは等長として、JATHub の PCB レイアウトでも等長であること。

- 冗長性のある BOOT システムを実現するために、1 つの QSPI flash memory と 2 つの SD カードを使用すること。詳細は 4 章の BOOT システム実装で説明する。

- HSC crate に入るように、回路の大きさは縦 9U、奥行き 16cm とすること。また、VME backplane である J1, J3 に接続するコネクターを使用すること。

- VME 規格に沿ったアクセスが行えること。

- RJ45 multijack で横幅を取るので、HSC crate の slave module 用 20 slots のうち、JATHub1 台 につき 2 slots 使う横幅にすること。

- 電源供給は、HSC crate の J3 backplane から、もしくは、デバック用に外付け電源ケーブルから 行うこと。

図 3.3 JATHub を制御系の中心として組み込んだ TGC 検出器エレクトロニクスシステム。TGC 検出器読み出し・トリガーエレクトロニクスシステムの詳細絵 (図 2.1) に、JATHub を含む制御系の詳細絵を組み込んだ。

ここで、Zyng-7045型を採用した理由について述べる。

第 1 に、JATHub が扱う信号線の必要数分、I/O pin が揃っている Zynq を選んだ。最大 11 枚の PS board の操作用信号線で 88 本、VME slave module としての信号線で 49 本、他にも 50 本程など、JATHub において PL に繋げる信号線は多く、pin 数が多い FPGA が必要になってくる。

第2に、必要十分な処理能力を持つ Zynq を選んだ。Zynq には Zynq MPSoC と呼ばれる複数のプロセッサーを積んだ種類のデバイスも存在する。しかし、今回 JATHub が Linux を起動させて行うのは、Ethernet 通信機能と、PL から伸びる信号線の操作である。つまり、そこまで高度でないアプリケーションの実行に限られているので、Arm 32bit CPU を搭載した Zynq-7000 シリーズのデバイスを選んだ。また、Zynq SoC に組み込まれている FPGA には高速通信 transceiver が優良なデバイスも存在する。しかし、JATHub は、GTX transceiver を利用する機会が光 Ethernet 通信などに限られる。

結果、適切な Zyng SoC デバイスは Zyng-7045 型 FFG900 パッケージであった。

### 3.2 ハードウェアの設計

JATHub の概要設計に従って、JATHub 第 1 試作機を製作し、JATHub の動作検証を行う。そのため、JATHub 第 1 試作機の回路図 (D.1 節参照) を作成した。本節では、下記に示すような、ハードウェア設計の技術的特徴を説明する。また、その後評価ボードを使用した JATHub の機能のデモンストレーションについて説明する。

- i. JATHub のインターフェイスと周辺機器

- ii. CAT6 ケーブルを使用した他回路との LVDS 通信

- iii. 回路上の等長配線

- iv. Zynq に対応した電源機構

### 3.2.1 JATHub のインターフェイスと周辺機器

ハードウェア設計ではまず、JATHub に載せるインターフェイスと周辺機器を洗い出した。そして、メインドライバーとして Zynq SoC が JATHub のインターフェイスや周辺機器を操作できるように回路 図の設計を行った。本節では、Zynq の PS 部と PL 部に分けてインターフェイスや周辺機器を述べる。 Zynq と JATHub 上のインターフェイスや周辺機器の接続関係は図 3.4 に示す。 Zynq は、3.1.3 節の要請に従って、'XC7Z045-2FFG900I' 型番を使用した。

- ■PS 部 Zynq のプロセッサー部である PS 領域から伸びるピン; Multiplexed Input Output(MIO) ピンには、以下の 5 つの周辺機器・インターフェイスを接続させた。 MIO に接続できる周辺機器は Zynq の User Guide[13](Table2-4) にて使用できるピンも含めて指定されている。ユーザーはその制限の元 MIO に接続する周辺機器を選択する。

- SD カード x2: Zynq の Boot ファイルや実行ファイルを保存する、取り外し交換可能な不揮発性 メモリである。Zynq Linux のハードディスクとして使用する。プロセッサー (PS) で走る Zynq Linux により中身の書き換えを行う。

- QSPI flash memory: Zynqの Boot ファイルを保存する、取り外し不可能な不揮発性メモリである。PS で走る Zynq Linux などにより Quad Serial Peripheral Interface(QSPI) アクセスで中身の書き換えを行う。(5.1.3 節にて説明する通り、バイパスとして VME からの直接書き換えを行える仕様も追加した。)

- **DDR3\*3 memory**: 32bit データ幅の Dynamic Random Access Memory(DRAM) である。Zynq Linux のメモリとして使用する。

- Ethernet RJ45 + PHY(Debug 用): LAN(Copper) ケーブルによる Gigabit Ethernet(GbE) 通信を行うためのインターフェイスである。Zynq Linux によるネットワーク通信の実績は当初 Copper ケーブルによるもののみだったため、JATHub 第1試作機にはネットワーク通信のデバッ

<sup>\*3</sup> Double-Data-Rate3

図 3.4 Zynq にドライブされる JATHub の周辺機器。周辺機器をそれぞれ Zynq の適切な Bank のピンに接続した。

ク用として実装した。

- USB UART(Debug 用): Zynq PS のコンソール画面を開くためのインターフェイスである。 Universal Asynchronous Receiver/Transmitter(UART) は非同期シリアル通信を行うデバイスであり、接続相手の HostPC にて Zynq PS の Command User Interface(CUI) を開くことができる\*4。それにより、Zynq Linux が起動する前の PS configuration や Linux 起動の様子が確認できる。JATHub 第1 試作機には PS 稼働の様子を見るためのデバック用として実装した。

- ■PL 部 Zynq の FPGA 部である PL 領域から伸びるピンには、主に以下の 7 つのインターフェイスを接続させた。

Zynqの I/O ピンは機能によって 'Bank' と呼ばれるグループに分けられており、ピンの特性も Bank によって違う。Firmware でデザインすることでユーザーが自由にピンの設定を行える Bank には、自由 度の高い User I/O ピンが付いている。GTX transceiver 用の Bank には、高速通信用の二極信号線と GTX 用水晶発振器のクロック信号線用 I/O ピンが付いている。そして、Zynq を configuration するための Bank('Bank 0') には、JTAG 信号線用のピンや、Zynq の電源サイクルを行うリセット信号線 'Power on Reset(POR)' 用のピンや、PL の reset のみを行う信号線 'Program\_b(PROGB)' 用のピンなど、Zynqの configuration に関わる信号線用のピンが付いている。以下で説明するインターフェイスは、それぞれ

<sup>\*4</sup> コンソール画面にて、'screen' コマンドが非常に使いやすかった。

の信号線の特性に合わせて、適切な PL のピンに接続した。

- **VME**: VME 規格の J1, J3 backplane に接続するためのインターフェイスである。HSC (VME) crate に挿入された際、VME slave module として、Zynq 内の PL の簡単な register 操作を行うために設けた。アドレス 24bit 幅、データ 16bit 幅で設計した。User I/O ピンに接続しており、PL の Firmware にて、VME 規格の信号を処理する。

- **Ethernet (SFP)**: 光 Ethernet 用のインターフェイスである。SFP は光信号と電気信号を相互変換する光 transceiver である。JATHub では、外部からの 1000BASE-X 規格の光信号を SFP で電気信号に変え、PL の GTX transceiver に渡す。機能実装の詳細は 4 章の光 Ethernet 通信にて説明する。

- **SFP DDMI**: SFP は環境情報も内部 register に記録しており、I2C 通信によりその register を読むことができる。これを Digital Diagnostic Monitoring Interface(DDMI) と呼ぶ。JATHub では DDMI により SFP のモニタリングを行う。

- **LEMO jack(tx/rx)**: LEMO 規格 copper ケーブルのインターフェイスである。JATHub では、 PS board から送られた LHC クロックをモニターするために、PS board とは独立した LHC クロックを受け取るための LEMO rx を実装した。また、PL で生成した信号を送り出すための LEMO tx も実装した。User I/O ピンに接続した。

- **PS board** 用 **RJ45 multi-jack**: 対 PS board 用のインターフェイスである。最大 11 台の PS board に 2 つの CAT6 ケーブルを繋げられるように、2×11 の RJ45 ポートを実装した。この信号 線は User I/O ピンに接続されており、Firmware によって自由度を保って信号処理が行える。詳 細は 3.2.1.1 節。

- 隣 JATHub 用 RJ45 multi-jack: 隣の JATHub と相互通信を行うためのインターフェイスである。master として 2×1 の RJ45 ポートを、slave として 2x1 の RJ45 ポートを実装した。slave JTAG('JTAG rx') 用 RJ45 ポートの信号線や slave reset 線は configuration bank 0 へ接続し、他の信号線は User I/O ピンに接続した。詳細は 3.2.1.1 節。

- 14pin JTAG rx connector(Debug 用): JATHub が JTAG slave として Host PC と接続するためのインターフェイスである。一般的に Xilinx 社製の FPGA, Zynq デバイスでは JTAG rx 通信による configuration を行う場合、14pin connector を使用している。 Xilinx 社製の 'Platform Cable USB II' を使用して、14 pin connector と HostPC の USB を接続し、HostPC から直接 FPGA, Zynq を configuration する仕組みになっている。そこで、JATHub にも Zynq configuration の Debug 用に 14pin connector を実装した。また、slave JTAG 用のピンは bank 0 に 1 つしかないため、隣 JATHub からの JTAG rx 信号線と干渉しないように、Jumper pin を使ったスイッチを設けた。

#### 3.2.1.1 Front-panel に設けたインターフェイス

図 2.8 の HSC crate に隙間なく全ての module を挿入するため、簡単に VME slave module のインターフェイス機器\*5を取り扱うことができるのが手前側のみとなる。他にインターフェイス機器を取り扱うことができるスペースは、HSC crate の裏側の J1, J3backplane の間にあるスペースのみであるが、アクセスが難しく、ATLAS 実験室の本番の HSC crate では手が届かない。そのため、HSC crate に実装することに留意しつつ JATHub にインターフェイス機器を設置した。また、JATHub は手前側に Front-panel を用意し、crate 挿入状態でも手前側のどこに何のインターフェイスが用意されているか分かるようにした。Front-panel のデザイン詳細は 3.3.1 節にて述べる。JATHub を HSC crate に挿入した状態でも取り扱う必要のあるインターフェイス機器は、2 つの SD card スロット、2 個の SFP、LEMO tx/rx、RJ45 multi-jack である。これらのインターフェイス機器は Front-panel 側に設けた。特に、RJ45 multi-jack は図 3.5 の通りに 2x6 の部品と 2x8 の部品を使用した。これにより、最大 11 台の PS board と JTAGパス、Recovery パスで接続し、隣の JATHub とも相互的に JTAG パス、Recovery パスで接続できるようにした。図 3.5 は RJ45 multi-jack の部品を示しており、表 3.1 に従って各ポートの信号線を RJ45 multi-jack に繋いだ。

パスの種類 接続先の他回路 本 JATHub 図 3.5 中の RJ45 のポート番号 11 台 PS board JTAG パス CN4 O A,B,C,D,E,F,G,H, CN5 O A,B,C Master Master 11 台 PS board Recovery パス CN4 O I,J,K,L,M,N,O,P, CN5 O G,H,I Master 隣の JATHub(S) JTAG パス CN5 ODMaster 隣の JATHub(S) Recovery パス CN5 OJSlave 隣の JATHub(M) JTAG パス\*6 CN5のE Slave 隣の JATHub(M) Recovery パス CN5のK

表 3.1 RJ45 multi-jack の使用ポートの割り当て

#### PORT ASSIGNMENT of RJ45 Multi-Ports(ix)

CN4(5569264-1) 2\*8 RIGHT side

UPPER С С В  $\mathbf{E}$ D В Α Η G F Ε D Α G Ρ LOWER

図 3.5 RJ45 multi-jack の概要図。図の左側が JATHub の上向きとなるように設計した。この並び で Frontpanel に設置した。

CN5(5569263-1) 2\*6 LEFT side

<sup>\*&</sup>lt;sup>5</sup> VME インターフェイスは裏側にあり、VME backplane に接続する。

<sup>\*6</sup> 文中の 'JTAG rx'

### 3.2.2 CAT6 ケーブルを使用した他回路との LVDS 通信

CAT6(Category-6) ケーブルは 4 対 8 線の導線で構成されており、4 種類の差動信号線 (+,-) を通すことができる。JATHub では、LVDS(Low Voltage Differential Signaling) 通信を採用し、他回路とCAT6 ケーブルで信号線を接続する設計にした。

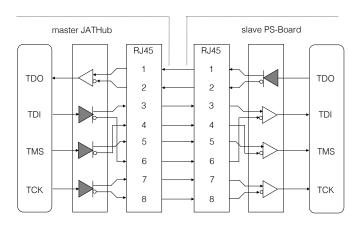

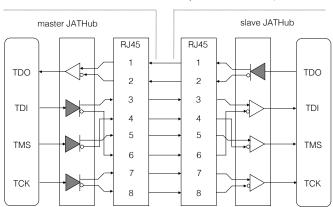

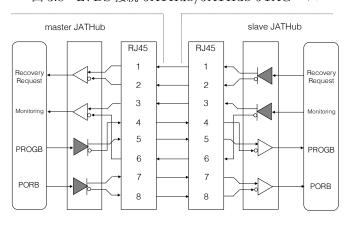

JATHub を master として、slave の各回路に対して 2 本の CAT6 ケーブルを接続するが、その信号線と RJ45 ピン配置は図 3.6、図 3.7、図 3.8、図 3.9 にて示している。ここで、灰色の三角 LVDS 素子が driver 素子を示しており、白色三角 LVDS 素子が receiver 素子を示している。

#### ■対 PS board の場合

- JTAG パスでは 4 つの信号線、TCK (Master → Slave)、TMS (M → S)、TDI (M → S)、TDO (S → M) を配線した。(図 3.6)

- Recovery パスでは、Recovery Request['Recov']  $(S \to M)$ 、Monitor['MON']  $(S \to M)$ 、PROGB reset  $(M \to S)$ 、GTX reset  $(M \to S)$  を配線した。詳細は 4 章。(図 3.7)

#### ■対隣 JATHub の場合

- JTAG パスでは 4 つの信号線、TCK (Master → Slave)、TMS (M → S)、TDI (M → S)、TDO (S → M) を配線した。(図 3.8)

- Recovery パスでは、Recovery Request['Recov'] (S → M)、Monitor['MON'] (S → M)、PROGB reset (M → S)、PORB reset (M → S) を配線した。詳細は 4 章。(図 3.9)

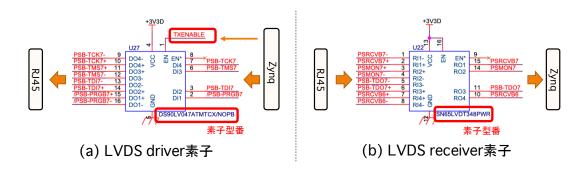

### 3.2.2.1 LVDS 通信

LVDS 通信は低電圧差動信号による伝送技術を指している。図 3.10 のような、(a) driver と (b) receiver の素子の間で、1.4 V -1.0 V の範囲の低電圧差動信号を作り出し、一方通行の信号伝送を行っている。'1'信号 (3.3 V) を送るとき、driver 素子は (+) 差動線にて 1.4 V、(-) 差動線にて 1.0 V を receiver 素子に流す。'0'信号 (0 V)を送るとき、driver 素子は (+) 差動線にて 1.0 V、(-) 差動線にて 1.4 V を receiver 素子に流す。この LVDS 通信による利点は 4 点ある。

- i. 安定したデータ伝送: LVDS 信号は receiver 素子にて差動線 (+)(-) の差分を評価して、信号を出力する。そのため、外的電気ノイズが両差動線に発生しても、差分は不変なので、出力される信号が一定に保たれる。また、差動線の電流方向は逆であるので、並走する差動線から発生する磁場は安定する。そのため、内的電気ノイズは発生しにくい。従って、伝送の安定性が保たれる。

- ii. 長距離データ伝送: LVDS 信号は差動線 (+)(-) に電位差が生じていればよいので、長距離伝送中の電圧降下によって信号振幅が減衰しても正しく信号を伝送できる。

- iii. 低消費電力: LVDS の素子は定電流回路 (3.5 mA) を内蔵しているため、終端抵抗 (100  $\Omega$ ) により 常に一定の低電力消費を行っている。スイッチ動作によって電力を多く消費する CMOS(1 線) 信号 と比較すると、消費電力は抑えられている。

図 3.6 LVDS 接続 JATHub/PSB JTAG パス

図 3.7 LVDS 接続 JATHub/PSB Recovery パス

図 3.8 LVDS 接続 JATHub/JATHub JTAG パス

図 3.9 LVDS 接続 JATHub/JATHub Recovery パス

iv. 大量高速データ伝送: LVDS の差動信号の振幅は  $0.4~\rm V$  程と狭いため、 $3.3~\rm V$  振幅などの信号と比べると高周波数の伝送が可能となる。

利点 i.、ii. は、ATLAS 実験室内における JATHub と PS board 間 (最大 15 m) の安定したデータ伝送を実現する上で都合がよい。そのため、CAT6 ケーブルの差動線を LVDS 通信に使用した。尚、利点 iv. に関して、JATHub は LHC クロックに同期しないスローコントロールで他回路を制御するため、今回この利点は重要ではない。

#### 3.2.2.2 LVDS 素子による Fail Safe 機能

信号の伝送を行う際、意図しない状況で信号が意図しない動きをすることがある。JATHub は特に他回路の reset を取り扱うため、誤って active low の reset 線に 0 信号を送ることは避けたい。そこで、意図しない状況で安全装置が作動し slave module が 0 信号を受信しないようにするという Fail Safe 機能の実装がハードウェア設計のレベルで重要になってくる。LVDS 素子は Fail Safe 機能を実現できる組み合わせを選定した。

図 3.10 の (a) の driver 素子は、'EN' ピン (TXENABLE 信号線) に '1' 信号 (3.3V) が入力されると、Zynq からの入力信号 (0 or 1) は対応する LVDS 差動信号 ('0' or '1') に変わり RJ45 ポートへ出力される。しかし、EN ピンに '0' 信号 (0V) が入力されると、Zynq からの信号関係無しに、High impedance の LVDS 差動信号が出力される仕様になっている [12]。High impedance 信号とは、信号線が切断された状態と同様の状態であることを表している。

図 3.10 の (b) の receiver 素子は、'0' or '1' の LVDS 差動信号を入力すると、対応する '0' or '1' 信号を出力する。しかし、LVDS 差動信号線にて High impedance 信号が入力されると、自動的に出力線が pull up されて、'1' 信号が出力される仕様になっている [11]。

これにより、driver 素子と receiver 素子が CAT6 ケーブルで接続していない場合、receiver 素子には High impedance 信号が入力されている状態なので、Fail Safe 機能によって常に '1' が出力される。また、driver 素子の EN ピンは Zynq の PL から伸びている TXENABLE 信号線によって操作できるよう設計した。そのため、CAT6 ケーブルで素子間が接続されていても、回路の電源が入っていなかったり、Zynqが configuration されていない時 TXENABLE 信号線は '0' 信号になっているので、driver 素子は High impedance 信号を出力し、receiver 素子は同様に Fail Safe 機能によって '1' 信号が出力される。

このように、CAT6 ケーブルで 2 つの回路が接続されていても、一方が積極的に '0' 信号を送らない限り、もう一方に '0' 信号が届かないよう、Fail Safe 機能を実装した。また、同時に、どの信号線もアイドル状態は '1' 信号になる設計となった。また、回路間でこの LVDS 通信の Fail Safe 機能が働くように、JATHub はもちろんの事、LVDS 通信相手である PS board の LVDS 素子も図 3.10 の素子で統一した。

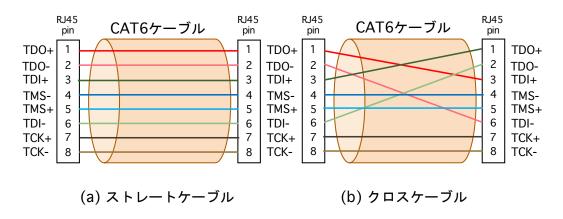

#### 3.2.2.3 CAT6 ケーブルの種類

CAT6 ケーブルには、ストレートケーブルとクロスケーブルが存在する。図 3.11 のように、ストレートケーブルは 8 つの線それぞれが同じ番号のピンに繋がるが、クロスケーブルは違う番号のピンにスワップして繋がる。Ethernet 通信では master-slave でピンの配置を変え、その間でストレートケーブルが使えるようになっている。クロスケーブルは、昔の Ethernet 通信の master module 同士を繋ぐ際に同種のピ

図 3.10 LVDS 素子。(a) が driver の素子で、(b) が receiver の素子。(a) の driver 素子の EN ピンは Zynq PL から操作できるようになっている。

ン配置でも通信できるように使用していた物であった。現在の Ethernet 通信では master module 同士でも、module 側で自動でピンのスワップを行っているので、ストレートケーブルも使用できる。そのため、最近ではクロスケーブルは市場に出回っていないが、運悪く拾ってしまうこともある。

しかし、JATHub で採用している LVDS 通信では、ストレートケーブルを使用することを想定して設計した。従って、使用時は CAT6 ケーブルの種類を慎重に選ばなければならない\*<sup>7</sup>。見極め方としては、CAT6 ケーブルのプラグの透明な部分にて信号線に色が付いているのが確認できるので、両端で配色順が一致していることを確認する方法が簡単である。

図 3.11 CAT6 ケーブルの種類。(a) ストレートケーブル or (b) クロスケーブル。JATHub の LVDS 通信ではストレートケーブルを使用しなければならない。ここでは、例として JTAG 通信における RJ45 のピン配置を示している。

### 3.2.3 等長配線

各回路との Recovery パスには、Recovery Request(Recov) 信号線と Monitor(MON) 信号線がある。 この 2 本の信号線において等長配線が要請されている。そのため、図 3.12 のように、PCB にて 300 ps

<sup>\*7</sup> Copper ケーブルの Ethernet(Debug) はクロスケーブルでも繋がる

(60 mm) 精度で等長配線にするように、Zynq PL の同じ Bank に信号線を固めて、それらの信号線がお互いに近い Zynq ピンに繋がるように設計した。

図 3.12 等長配線を指示した信号線。緑色の信号線。他回路から同時に送られる信号は同時に受信されなければならない。

また、ハードウェア設計の要請に従って、SFP と Zynq 間の差動線は PCB レイアウトにて等長配線になるように設計した。詳細は 3.3.2 節にて述べる。

### 3.2.4 電源周り

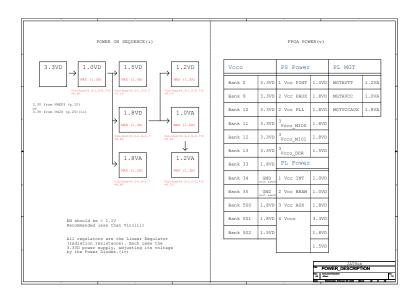

Zynq にはいくつもの Bank が存在するが、それぞれ個別の電源がある。これら Bank への電源供給には順序が存在する [13]。 PS と PL は独立した電源系統となっている。以下、電源供給の順序である。それぞれの Bank に必要な電圧は図 3.13 の 'FPGA POWER' に示してある。

- i. PS PINT | PL INT, PL BRAM, (PL Vcco)

- ii. PS PAUX, PS PLL, PS MIO, PS DDR | PL AUX, PL Vcco, MGT(GTX bank) AUX

- iii. MGTAVCC

- iv. MGTAVTT

ここで、放射線耐性が確認されている Linear Regulator という電圧制御素子を使用して、電源供給を調節する。Linear Regulator は降圧のみ可能な素子で、電源と負荷の間に直列に接続させ、定電圧直流電源を出力する。また、今回選定した素子は Enable ピンに '1' が入力されると降電圧を出力し始め、出力が定まったら Open-drain の PG ピンから '1' を出力する。そこで、JATHub では Linear Regulator の PG ピンと EN ピンを繋げて、図 3.13 の 'POWER OF SEQUENCE' のように、3.3 VD  $\rightarrow$  1.0 VD  $\rightarrow$  1.5 VD, 1.8 VD, 1.8 VA  $\rightarrow$  1.2 VD, 1.0 VA  $\rightarrow$  1.2 VA の順で電源が上がるように設計した。ここで、3.3 VD のみ外部から JATHub へ供給し、それ以外の電圧電源はダイオードで電圧を可能な限り下げて Linear Regulator での熱の発生を抑える設計にした。

3.3 VD は、VME J3、もしくは、外付け電源ケーブルから電源供給できるように設計した。合流地点にてフューズを設けて、ホールド電流値 12A、トリップ電流値 24A に設計した。ここで、トリップ電流値と

図 3.13 Zynq 電源の供給順序。Linear Regulator を使用している。

は、それ以上の電流が流れ込む場合、フューズが切れて電源供給を切断する電流値を指す。ホールド電流値は、フューズが切れることなく、安定して電源供給できる上限の電流値を指す。 (5.1.6 節で議論する通り、第 1 試作機の動作試験の結果により Fuse 容量の最適化を行い、最終的にホールド電流 6 A、トリップ電流 12 A とした。)

### 3.2.5 評価ボードによる機能のデモンストレーション

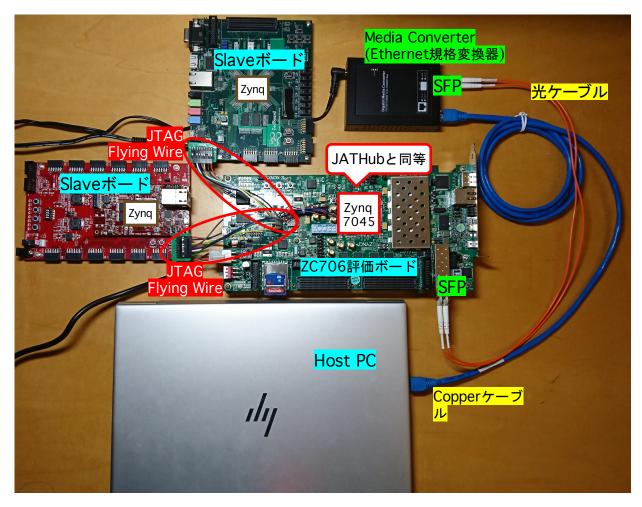

回路図作成と同時並行で、Xilinx 社製の ZC706 評価ボードを使用して、JATHub に実装予定の機能をデモンストレーションした。Zynq の開発に慣れて JATHub 第 1 試作機の動作試験にスムーズに入れるように知見を蓄えることを目的とした。デモンストレーションにあたり、Zynq の基本的な使い方に関して、Zynq に関わる開発作業ページ [14] や、同研究室の過去の作業マニュアル [15] を参照した。

ZC706 評価ボードには、JATHub 第 1 試作機と同様の型番の Zynq-7000 SoC が搭載されており、更に、SFP や JTAG 用 4 本テストピンが備わっていた。そのため、JATHub の光 Ethernet 通信機能と、JATHub の Zynq Linux が JTAG 通信をして slave module を操作する機能 (図 3.14) をデモンストレーションした。ここでは、他回路との接続は CAT6 ケーブルではなく、リボンケーブルを使用した。

結果、無事に機能が動作することを ZC706 評価ボードにて確認できたので、評価ボードの回路図も参考にしながら JATHub のハードウェア設計を進めた。

また、Zynq の組み込みデザイン (Zynq PS の組み込み Linux と Zynq PL の Firmware のデザイン) の 開発手続きも、このデモンストレーションの研究で完成させた。

### 3.3 JATHub 第1試作機の製作

回路図を作成し、JATHub 第 1 試作機のハードウェアの設計を決定した後に、JATHub 第 1 試作機の回路製作を行った。回路の部品配置の大まかなデザインと、フロントパネルのデザインを決めた

図 3.14 ZC706 評価ボードによるデモンストレーション。HostPC から Media Converter を経由して光 Ethernet 通信で ZC706 の Zynq にアクセス、そして Slave module の Zynq を JTAG 通信で操作した。

後に、第1試作機のプリント基板 (PCB) 製作と部品実装を外部業者 (有限会社ジー・エヌ・ディー http://www.gn-d.com) に発注した。

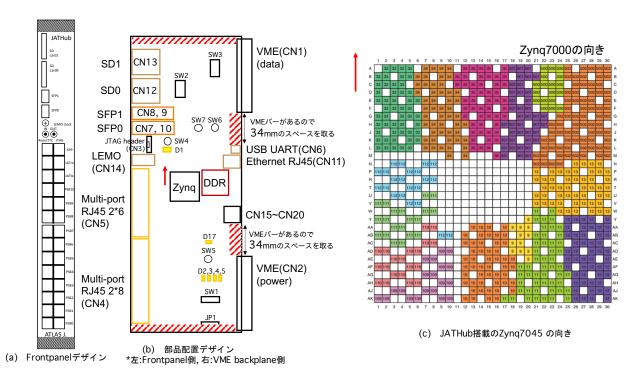

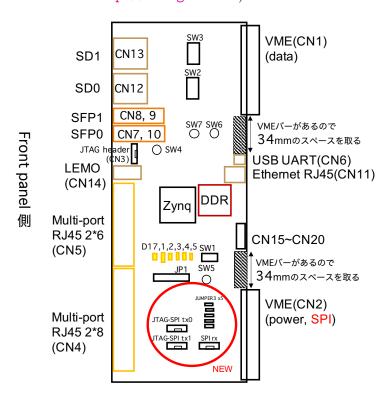

### 3.3.1 部品配置とフロントパネルデザイン

3.2.1.1 節の Front-panel 側のインターフェイスでも述べた通り、図 3.15 の (a) のように Front-panel を設計した。JATHub の上から SD card 0、SD card 1、SFP 0、SFP 1、LEMO tx/rx、RJ45 multi-jack を設置した。HSC crate に挿入できるよう、Front-panel の縦は crate 9U の大きさに、幅は 2 slots 分の大きさに設計した。

また、Front-panel の設計と並行して、JATHub 第 1 試作機上の主要な部品の配置デザインも行った。図 3.15 の (b) がその部品配置のデザインである。HSC crate に挿入できるよう、奥行きは 16cm で描いた。HSC crate への挿入を考慮した結果、縁の赤斜線領域がインターフェイス機器を置けない位置となった。左側が Front-panel 側で、Front-panel のデザインに合わせてインターフェイス機器を置いた。右側

が VME backplane 側で、3.2.1.1 節で言及した通り、VME connector P1, P3 と、Debug 用の Ethernet RJ45 と USB UART を置いた。VME backplane を支えるためのバーがインターフェイス機器と干渉してしまうため、backplane 側にも赤斜線領域がある。RJ45 と UART の機器はこの領域を避けて配置した。

Zynq I/O はその機能により Bank と呼ばれるグループに分かれており、(c) は JATHub に搭載する Zynq7045 のそれぞれの Bank から伸びるピンの位置を示している [16]。 Zynq の右上にある Bank500, 501, 502 が PS 領域から伸びたピン。左下の Bank109, 110, 111, 112 が GTX tranceiver から伸びたピン。Bank33, 34, 35 が PL 領域のクロックを取り扱う Bank から伸びたピン。そして、それ以外の Bank 番号が PL 領域の様々な信号を取り扱う Bank から伸びたピンとなっている。

部品の配置デザインでは図 3.15 の (c) にある Zynq-7000 SoC の設置向きに注意した。この Zynq7045 の PS 領域と接続するインターフェイス機器は Zynq よりも上側に設置した。GTX transceiver に繋がる SFP や、Bank109 に繋がる LEMO は、Zynq の左横に近い位置に設置した。そして、RJ45 multi-jack の信号線は Bank9-12 に接続するので、RJ45 multi-jack は Front-panel の下側に設置した。

図 3.15 の (b) では、reset 線を on-board の押しボタンでも操作できるようにするため、スイッチを導入した。PL の reset を行う PROGB reset (SW4) や、Zynq の再起動を行う PORB reset (SW7) もスイッチで行えるように設計した。また、JATHub の状態確認を目的として、LED も設置した。具体的には、電源供給されると点灯する LED (D17) や、Zynq の PL が configuration されたことを示す LED (D1)\*8、PL の User I/O から伸びる Firmware で制御可能な LED (D2-5) を設置した。

また、VME P3 近くの CN15-20 から外付け電源ケーブルが伸びるように設計した。EIL4 区域では、こちらのコネクタを用いて電源供給する。

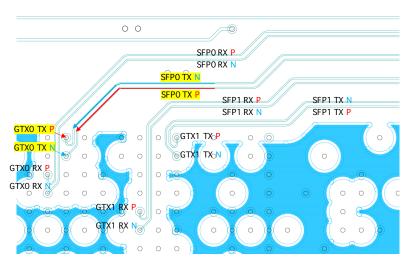

### 3.3.2 プリント基板 (PCB) レイアウト概要

回路図を作成し、部品の配置デザインや Front-panel のデザインを決定した後は、外部業者に委託して PCB の製作と部品実装を実施した。委託先業者と協議を重ねていき PCB レイアウトは図 3.17 のようにした。PCB レイアウトは等長配線も考慮して実施した。特に、SFP 光 transceiver と Zynq GTX transceiver 間の信号差動線 (P: +, N: -) は、等長配線にするためのスペースを取ることが難しかった。そのため、SFP0 の TX 線の差動線 (P, N) は、図 3.16 のようにスワップさせた。この差動線の極性の不一致は Zynq PL の Firmware にて修正できるので、Zynq は SFP0 を問題なく使用できる。

また、PCB は 14 層構造にした。階層構成は表 E.1 に示した。インピーダンス値は、単線の信号線に関しては特性インピーダンス (Zo): (40  $\Omega$  or 50  $\Omega$ ) となり、極性がある差動信号線に関しては差動インピーダンス (Zdiff): (80  $\Omega$  or 100  $\Omega$ ) となるように設計した。

### 3.3.3 試作機納品

2020 年 4 月 17 日に、JATHub 第 1 試作機 (図 3.18) が 2 台、KEK へ納品された。納品直後は部品が正しく実装されているか 1 つずつ確認した後に、外付け電源ケーブルから 3.3V を電源供給して正常に動くか検査した。この時、消費電流値は 0.8A であった。また、部品から煙が立つこともなく、正常に電

<sup>\*8</sup> Zynq の PS と PL は独立に機能する。この LED は PL の configuration のみを示している。

図 3.15 第1試作機での部品配置とフロントパネルデザイン。

図 3.16 SFP0 の TX 差動線の極性のスワップ。Zynq PL の Firmware にて "TXPORLARITY"を High と設定すると、Firmware がスワップ差動線の極性を更にスワップして扱う。それにより、Zynq は問題なくこの信号線を操作できる。

源供給できたことを確認した。更に、全てのレギュレーターから出力された電圧が正しいこと、Zynq の Programming 等基礎動作が正常に行えたことも確認した。

手前側が Front-panel で、奥側が VME backplane 用 connector である。中心に Zynq-7000 SoC が搭載されており、Front-panel の SFP、もしくは奥側の RJ45 から Ethernet で外部と通信できるようになっている。 Zynq の PL に Firmware を焼き、Frontpanel の RJ45 multi-jack の信号線を Hardware 的に処

図 3.17 第1試作機の PCB レイアウト。業者に委託して製作してもらった。

理できるようになる。また、Zynq の PS で起動する Zynq Linux 上で適切なドライバーやアプリを用意すると、それらの信号線を操作することができるようになる。また、Zynq の起動には、2 つの SD card と 1 つの QSPI flash memory を使用する。

次章では、この JATHub 第 1 試作機の Zynq に機能を実装し、動作試験を行って、設計通りに稼働することを確認した話を述べる。

### VME backplane側 RJ45 Ethernet通信 外付け電源ケーブル用 **UART** Chumina minimana VME P3 (Power) VME P1 (data) 📲 RJ45 multi-jack JTAG パス Recovery パス SD card ×2 11 PS boards Bootシステム JATHub | JATHub 光Ethernet通信 (slave, rx) LEMO tx/rx Front-panel側

図 3.18 JATHub 第 1 試作機の写真。2020/4/17 に KEK へ 2 台納品された。

# 第4章

# JATHub 第1試作機の機能実装と動作試験

JATHub のメインドライバーである Zynq SoC に機能を実装し、製作した JATHub 第 1 試作機の動作 試験を行った。

Zynq への機能実装において重要となるのは、FPGA 部分である PL のデジタル回路を構築する Firmware のデザインと、プロセッサー部分である PS で走る Zynq Linux や自作アプリケーションなどの 組み込み Linux (Software) のデザインである。本研究では、これらの Zynq 組み込みデザインを開発し、JATHub の機能を実装した。実装した機能は 3.1.1 節で述べた "JATHub の必要な機能"に加え、'VME 操作'も含めた全 6 項目であり、これらの機能を使ってフロントエンド回路の制御やモニターを行う。本 番環境においてもこの 6 項目の機能を持って、JATHub を稼働させる予定である。この章では、開発環境のセットアップについて述べた後、各機能の実装における Zynq デザインの開発詳細と、試作機による動作試験の詳細を説明する。最終的な Zynq デザインの Diagram は F 章に載せている。また、開発した Zynq デザインは Open-it の JATHub プロジェクトページ [9] にて公開予定である。

### 4.1 開発環境

### 4.1.1 Zynq 組み込みデザインの開発

Zynq 組み込みデザインの開発に使用したツールを表 4.1 にまとめた。

Zynq 組み込みデザインの開発には Windows 10 Pro の開発 PC を使用した。Zynq の PL 部にプログラムする Firmware の開発や PS 部のハードウェア的設定 (MIO ピンの設定や、プロセッサーの駆動クロック、メモリの設定など) は、Xilinx 社が提供するアプリケーション "Vivado IDE 2018.2"を Windows 10 上で使用し行った。Vivado IDE では、Xilinx 社から提供された特定の機能を実装するための Package(IP(Intellectual Package)) を導入したり、Verilog などの HDL(Hardware Design Language) を使用して自作の信号処理を書くことで、Firmware をデザインする。また、Zynq の User I/O ピンがどの信号線に使用するかなどの制約を行う。最後に Firmware をコンパイルし、バイナリーファイル "Bitstream"を生成する。そして、Bitstream を含む HDF(Hardware Design File) を出力する。

Zynq の PS 部で走る Zynq Linux の開発は、Xilinx 社が提供するクロスコンパイラー "petalinux tool 2018.3"を Ubuntu16.04 上で使用し行った。ここで、Ubuntu16.04 は Windows 10 上で走る仮想マシン

(VMware) で起動している。また、クロスコンパイラーとは、開発環境とは異なる環境で実行可能なファイルをコンパイルするツールを指す。Petalinux では、Vivado で出力した HDF を読み込ませて、ハードウェアの設定に沿ったデバイスドライバー、デバイスツリー、Root File System の設定を行うことで、Zynq Linux という Zynq 上で走る OS をクロスコンパイルすることができる。また、自作アプリケーションを Zynq Linux に組み込むこともできる。そして、クロスコンパイルした Zynq Linux 用の Boot ファイルを、Zynq の flash memory(SD card and QSPI flash memory) にプログラムし電源を入れることで、Zynq を configuration して Zynq Linux を起動することができる。Boot ファイルには Bitstream も含まれているので、Firmware の PL へのプログラムは一連の Zynq 起動 sequence の中で行われる。Boot ファイルなどの詳細な説明は 4.6 節で行う。尚、Zynq Linux 上で走る自作アプリケーションは"Vivado SDK 2018.2"上でデバックやコンパイルを行い開発した。

HostPC には Windows 10 Pro を使用し、Xilinx 社提供のソフトウェア "Vivado Hardware Manager(Vivado HM)"と Xilinx Software Commandline Tool(XSCT) を走らせた。GUI で操作する Vivado HM では、ターゲット回路の FPGA、Zynq の configuration やプログラム、'デバック' を行い、QSPI のプログラムも行った。また、CUI で操作する XSCT では、FPGA、Zynq、QSPI の configuration とプログラムを行った。

| OS                  | 開発アプリ             | 出力ファイル            | Zynq 組み込みデザイン開発詳細                            |

|---------------------|-------------------|-------------------|----------------------------------------------|

| Windows 10          | Vivado IDE 2018.3 | HDF(Bitstream など) | Zynq PL Firmware 開発や Zynq PS の設定             |

| Windows 10          | Vivado SDK 2018.3 | 自作アプリの実行ファイル      | Zynq Linux 上の自作アプリ開発                         |

| Ubuntu $16.04^{*1}$ | petalinux 2018.3  | Zynq Boot ファイル    | Zynq Linux のクロスコンパイル                         |

| Windows 10          | Vivado HM(GUI)    |                   | FPGA, Zynq の configuration や 'debug',        |

|                     |                   |                   | QSPI flash memory $\mathcal O$ program       |

| Windows 10          | XSCT(CUI)         |                   | FPGA, Zynq, QSPI $\mathcal O$ configuration, |

|                     |                   |                   | program                                      |

表 4.1 Zynq 組み込みデザイン開発環境

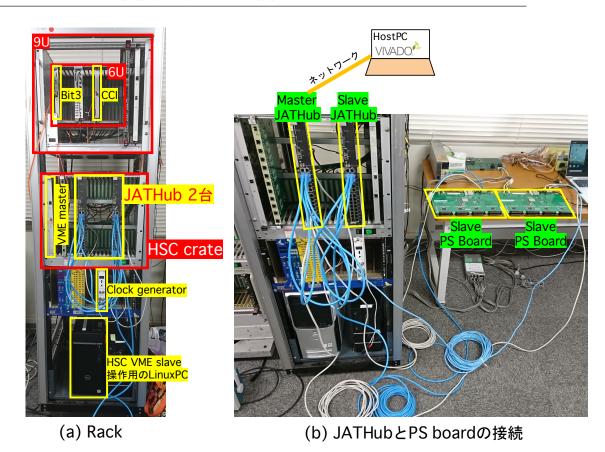

#### 4.1.2 テストベンチ

動作試験を実施するに際して、東京大学と KEK(高エネルギー加速器研究機構) に試作機を稼働させる ためのテストベンチを準備した。テストベンチは ATLAS 実験室の TGC 検出器周辺のエレクトロニクス 設備に近い環境になっており、実際の本番設備に出向かなくても開発回路の動作試験や TGC 検出器エレクトロニクスシステムの実証試験が実施できるようになっている。

テストベンチの概要は図 4.1 の通りである。回路室側には、6U/9U\*2の crate を置き、HSC crate 内の master module を操作するために Bit3 と Crate Control Interface (CCI) を挿入する。本論文では述べないが SL もこの crate に置く。また、その他に HSC VME 操作用の LinuxPC や光 Ethernet 用の Switching Hub を設置する。実験室側には、HSC crate を置き、VME master と 2 台の JATHub 第 1 試

<sup>\*1</sup> Windows 10 上で走る仮想マシン (VMware) で起動している。

<sup>\*2 6</sup>U や 9U とは crate の縦の大きさを表す。

56 4.1. 開発環境

図 4.1 テストベンチの概要。本番の TGC 検出器エレクトロニクスとほぼ同様のシステムを構築し、開発回路の動作試験を行う。今後は SL や ASD なども加えて TGC 検出器エレクトロニクスシステムの実証試験も行う予定である。

作機を挿入する。また、PS board 試作機や Clock Generator も設置する。

Switching Hub から JATHub へ光ケーブルを接続する、もしくは、LAN ケーブルを直接 JATHub に接続することで、JATHub 第 1 試作機がネットワークに繋がるようにする。そして、JATHub から CAT6 ケーブルで slave module に接続する (詳細は本節後半)。また、HSC VME master module を操作するために、LinuxPC から Bit3 へ光ケーブルを伸ばし、Bit3 が VME backplane 経由で CCI を操作し、CCI から HSC VME master module へ光ケーブルを繋げるパスを準備する。更に、本来 Level-0 trigger system の上流から LHC クロックを配布するが、当テストベンチでは LHC クロックを擬似的に Clock generator から出力し LEMO ケーブルで配布する。

実際に東京大学と KEK にテストベンチを作成した。図 4.2 は KEK のテストベンチの様子である。 JATHub 第 1 試作機を稼働させるための手段として、卓上で LV 電源から電源供給する方法、もしくは、当テストベンチの HSC crate に挿入し VME J3 backplane から電源供給する方法があり、どちらの手段も実施できるようにする。また、KEK テストベンチでは、図 4.2 の (b) のように隣の作業台に 2 台の PS board 試作機を置いた。

なお、必要な機能を全て実装し本番環境に近い状態で JATHub 第 1 試作機を稼働させた際の、最終的な消費電流値は表 4.2 に示す。JATHub には 3.3V の直流電源を供給しており、電流値測定にはクランプメーターを使用した。

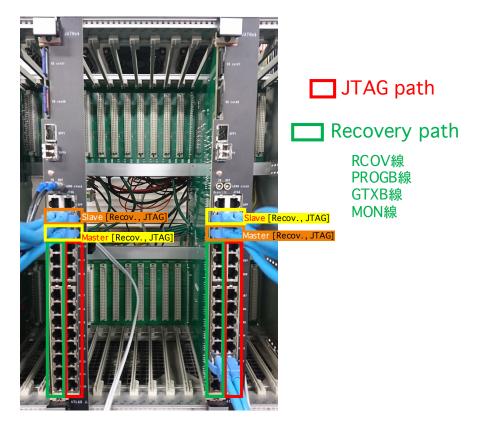

■JATHub 第 1 試作機 2 台間の接続 JATHub は隣の JATHub とお互いに制御できる設計になっており、図 4.3 のように、当 JATHub が隣 JATHub の master として JTAG 通信や Recovery 手続きを行うための RJ45 ポート、そして、隣 JATHub の slave module として JTAG 通信や Recovery 手続きをされるための RJ45 ポートが取り付けられている。今回両テストベンチで 2 台の JATHub 第 1 試作機を稼働

図 4.2 KEK テストベンチの写真。(a)6U/9U と HSC crate を収納した Rack の様子と、(b)Rack の隣の机に置いた PS board 試作機と JATHub 第 1 試作機の接続の様子を示す。(b) では、master JATHub から 2 台の PS boards へ 15m の CAT6 ケーブルで接続している。青色ケーブルは JTAG パス、白色ケーブルは Recovery パスである。

表 4.2 本番環境に近い状態での JATHub 第 1 試作機の消費電力. 電源供給は直流 3.3VD。

| JATHub 第1試作機の状態             | 消費電流値 (A) |

|-----------------------------|-----------|

| Zynq(PS+PL) configuration 中 | 1.61      |

| PS 上の Zynq Linux 起動中        | 2.25      |

| 定常待機状態                      | 2.08      |

| JTAG 通信機能 実行中               | 2.09      |

| 最大使用電流値 (A)                 | 2.25      |

させるにあたり、2 台間でお互いに制御できるかも試験した。その際、1m の CAT6 ケーブル 4 本を使用して JATHub 第 1 試作機同士を接続した。繋げたポートは図 4.3 に示されており、CAT6 ケーブルで接続する RJ45 ポート同士は同じ配色で示した。slave として接続する場合は上の RJ45 ポートを、master として接続する場合は下の RJ45 ポートを使用した。

本番環境では、 $1 \mathrm{m}$  の  $\mathrm{CAT6}$  ケーブルは長いため、 $0.5 \mathrm{m}$  程の  $\mathrm{CAT6}$  ケーブルを準備する予定である。

図 4.3 JATHub 第 1 試作機の RJ45 multi-jack. JATHub 間相互接続用 RJ45 ports は CAT6 ケーブルで接続する ports 同士を同じ配色にした。

■JATHub 第 1 試作機と PS board 試作機の接続 今回準備したテストベンチには、図 4.2 のように、卓上にて LV 電源を使用して 2 台の PS board 試作機を稼働させた。また、master JATHub(左) から本番環境を想定した 15m の CAT6 ケーブルを 4 本伸ばし、2 本ずつを各 PS board 試作機に接続した。青色ケーブルは JTAG パス、白色ケーブルは Recovery パスである。JATHub 第 1 試作機において、JTAGパス用の青色 CAT6 ケーブルは図 4.3 の 'JTAG path'へ、Recovery パス用の白色 CAT6 ケーブルは図 4.3 の 'Recovery path'へ繋げた。

また、図 4.2 の KEK テストベンチでは、1 台の master JATHub 第 1 試作機の配下に、1 台の slave JATHub 第 1 試作機と 2 台の PS boards 試作機がある状態で接続試験を行った。

# 4.2 光イーサネット通信

JATHub が外部とネットワークで通信できるように、JATHub と 60m-100m 程離れた回路室の光 Ethernet 用 Switching Hub を光ケーブルで繋げる。そのために、光 Ethernet 通信の機能を Zynq デザインに組み込んだ。この光 Ethernet 通信機能は、Xilinx が提供している光 Ethernet 通信用の Zynq デザイン例 [17] を参考に JATHub 第 1 試作機へ実装した。

### 4.2.1 Zyng における光 Ethernet 通信の仕組み

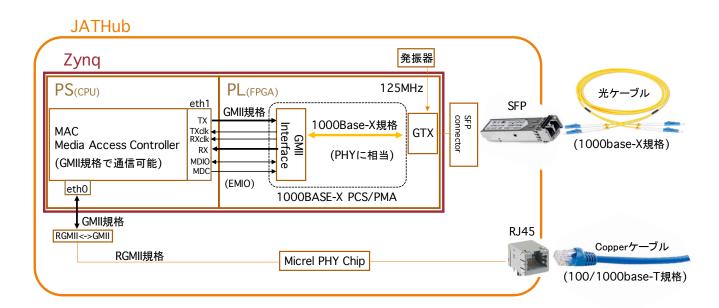

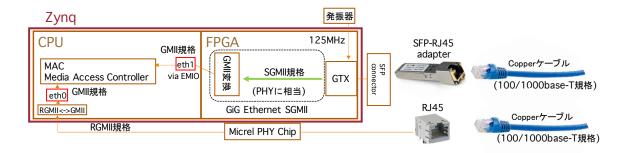

Zynq はプロセッサー PS を搭載していることから、TCP/IP 規格の Ethernet 通信を行い、外部からアクセスすることができる。CPU が Ethernet 通信を行うためには、物理層 (PHY) において Ethernet 信号を処理し、CPU が取り扱える信号に変換する必要がある。一般的には、PHY の集積回路 (PHY chip) を同回路上に実装する。しかし、Zynq は PHY の信号処理を PL 領域で行うことができる。そのため、Zynq の CPU は、PHY chip を使用しなくても、PL の GTX transceiver に繋がる SFP connector を経由してネットワークに接続できる。SFP connector には、SFP 光 transceiver と SFP-RJ45 adapter どちらでも設置することができ、SFP-RJ45 adapter を使用すると PHY chip を用いない LAN ケーブルによる Ethernet 通信も可能となる (詳細は G 章)。JATHub 第 1 試作機では、図 4.4 のように、SFP 光 transceiver と光ケーブルを使用して Ethernet 通信の確立を行った。

JATHub 第 1 試作機の Zynq PS は、Ethernet 通信を行う MAC(Media Access Controller) を搭載しており、GMII 規格による通信が可能である。GMII 規格は TX、RX、TX 用クロック、RX 用クロック、MDIO、MDC の 6 種類の信号線を使用する。この MAC には 2 つのインターフェイス 'eth0', 'eth1' があり、2 種類のパスから Ethernet 通信を同時に確立することができる。'eth0' は、MIO ピンと接続する回路上素子の PHY chip を介して、一般的な LAN(Copper) ケーブルによる Ethernet 通信に使用した。そして、'eth1' は、PS-PL 間を繋ぐ Extended MIO(EMIO) ピンを介して、光 Ethernet 通信に使用した。

Zynq の PL には GMII 規格のインターフェイスを設けた PHY(1000BASE-X PCS/PMA と呼ばれる IP ブロック) を実装した。この PHY は 1000BASE-X 規格の信号への変換を行う。1000BASE-X 規格 は上下 2 対 (tx,rx) の信号線を使用した場合の Ethernet 通信の規格であり、SFP から伸びる 2 対の光ケーブルの信号線に使用できる。よって、この PHY で MAC の eth1 と GTX transceiver を接続すると、Zynq の MAC は光ケーブルで外部と 1000BASE-X 規格の Ethernet 通信を確立できる。

またテストのために、eth0 側では、MAC と PHY chip 間は (R)GMII 規格、PHY chip からは 1000BASE-T 規格の信号で Ethernet 通信を行っていた。Copper ケーブルの場合 4 対 8 線の信号線があるので、1000BASE-T 規格の信号が使用できる。

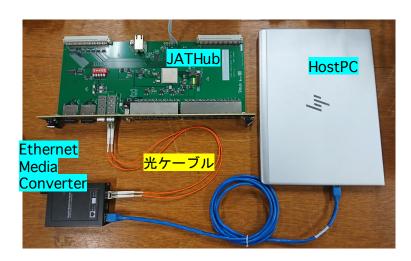

### 4.2.2 光 Ethernet 通信の動作試験

セットアップとしては、図 4.5 のようにした。HostPC には光ケーブル用のポートがなかったため、Media Converter を介して通信試験を行った。HostPC から伸ばした Copper ケーブルを Media Converter に繋げ、規格変換を行い、Media Converter の SFP ポートから光信号による通信を行った。Media Converter の SFP ポートと JATHub 第 1 試作機の SFP ポートを光ケーブルで繋げ、JATHub 第 1 試作機が 1000BASE-X 規格の光信号と通信できるようにした。IP address を表 4.3 の通りそれぞれ設定し、ローカルネットワークを HostPC と JATHub 第 1 試作機の間で構築できるようにした。

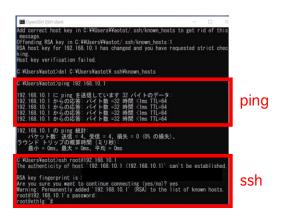

結果、図 4.6 の通り、HostPC から JATHub 第 1 試作機へ ping, ssh を送ることができた。また、ssh によって JATHub 第 1 試作機上で稼働する Zynq Linux にアクセスすることもできた。以上の事から、JATHub 第 1 試作機と光 Ethernet 通信を確立することに成功した。

図 4.4 光 Ethernet 通信の仕組み。PL 領域にて PHY を実装し、SFP からの 1000BASE-X 規格 Ethernet 通信を CPU の MAC に繋げる Zynq デザインにした。

図 4.5 光 Ethernet 通信試験のセットアップ。HostPC に光ケーブル用のポートがないため、Media Converter を介して光ケーブルによる接続を行った。

## 4.3 JTAG 通信による Slave module の制御

一般的に、FPGA や Zynq を制御するためには、Vivado HM が走る HostPC を近くに置き、短い JTAG ケーブルを繋げなければならない。 しかし、ATLAS 実験室で実装される FPGA や Zynq 搭載の回路は実質的にアクセス不可能な場所に置かれている。そこで、JATHub は中継役となって、CAT6 ケーブルで繋がる複数の遠隔回路を JTAG 通信により制御できる設計になっている。 JTAG 通信で行う動作は以下 3 点である。

| デバイス                | IP address   |

|---------------------|--------------|

| HostPC (Windows 10) | 192.168.10.2 |

| JATHub 第1試作機        | 192.168.10.1 |

表 4.3 光 Ethernet 通信試験でのネットワーク設定

図 4.6 光 Ethernet 通信試験の結果。HostPC から JATHub 第 1 試作機へ ping, ssh を送れた。

- FPGA に直接 Firmware をプログラムする。

- QSPI flash memory にプログラムする。FPGA 用 QSPI には Firmware 情報が入った configuration file をプログラムし、Zynq 用 QSPI には Boot ファイルをプログラムする。

- Zynq、FPGA 内の Firmware のデバックをする。

module にリセットをかけた際、QSPI 内のファイルが読み込まれて、reboot や reconfiguration が行われる。そのため、フロントエンドでの本番運用時に一番重要な動作は QSPI プログラムである。

図 4.7 JATHub による JTAG 制御概要図。XVC による操作と SVF による操作が行える。

JATHub 第1試作機には、以下の2種類のJTAG 通信手段を実装した。

- i. **Xilinx Virtual Cable(XVC)**: Vivado HM の GUI や Xilinx Software Commandline Tool(XSCT) の CUI を使用して、TCP/IP 通信を介して遠隔の slave module を制御する機能

- ii. **SVF player**: JATHub の Zynq Linux にアクセスして、Zynq Linux の CUI を使用して遠隔の slave module を制御する機能

JTAG 通信の動作試験では、図 4.7 と図 4.2 の通りセットアップし、1 台の master JATHub 第 1 試作機から、1 台の slave JATHub 第 1 試作機と 2 台の slave PS board 試作機へ JTAG 通信した。PS board FPGA(Kintex-7) 用の 2 種類 Firmware を用意し、一目で Firmware の Program が成功したか確認できるようにした。2 つの Firmware の違いは LED が点灯、もしくは点滅するかである。そして、PS board の QSPI flash memory へ program 試験も実施するために、それぞれの Firmware の情報を入れた configuration file も準備した。

以下、それぞれの JTAG 通信手段の実装と動作試験、そして、本番時の運用スタイルについて述べる。

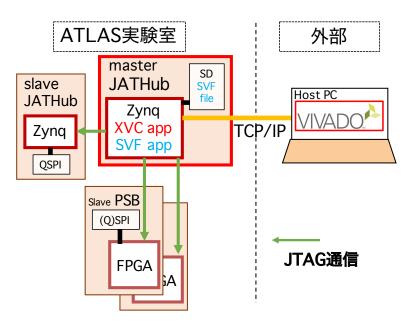

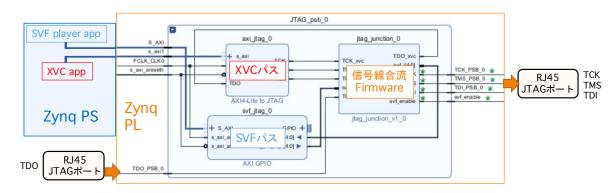

### 4.3.1 Xilinx Virtual Cable(XVC)

Xilinx Virtual Cable(XVC) は、図 4.7 のように、TCP/IP 通信で Zynq SoC にアクセスし、専用のアプリケーション (XVC app) を Zynq SoC 内で走らせることで、Zynq SoC が別回路の FPGA や Zynq に JTAG 通信するプロトコルである。この XVC プロトコルを利用することにより、Xilinx ソフトが走る HostPC がネットワークで master Zynq SoC にアクセスできれば、遠距離の slave 回路上の FPGA や Zynq に対してあたかも近くで繋いでいる様に Xilinx ソフトの機能を使用することが可能となる。Xilinx ソフトには Vivado HM と XSCT があるが、Vivado HM の機能は使い勝手が良く、具体的には以下のような機能が XVC 下で使用できる。

- **FPGA** のプログラムや **QSPI** flash memory のプログラム: FPGA や Zynq PL 部に Firmware をプログラムすることができる。また、回路上の FPGA に接続する QSPI flash memory に configuration file をプログラムすることもできる。尚、Zynq に接続する QSPI は、Zynq PS 領域にある QSPI controller が管理しており、FPGA による QSPI 操作と仕様が大幅に異なるため、 Zynq 用 QSPI への Boot ファイルのプログラムは XVC ではサポートされていない。

- Integrated Logic Analyzer(ILA): FPGA や Zynq の User I/O pin に繋がる信号線の挙動を、 オシロスコープでプローブするように見ることができる。Firmware 開発では信号処理のデバッグ 用ツールとして重宝されている。

- Integrated Bit Error Ration Test(IBERT): GTX transceiver の監視及び性能評価を行う ことができる。SFP などを使った高速光通信の信号中のノイズや、通信速度などを測ることができ る。光通信のパフォーマンス試験に使用する。

#### 4.3.1.1 XVC の開発と実装

Xilinx 社は XVC の Zynq デザイン例 [18] を提供している。Zynq Linux で XVC app が実行され、Zynq PL 内の Buffer を通って PL から伸びる JTAG4 線をドライブする仕掛けになっている (図 4.11)。 しかし、この Zynq デザイン例で使用される評価ボードは違う型番の Zynq デバイスを使用しているため、 JATHub の Zynq に適合するようにパラメータやソースコードを編集して実装した。具体的な変更点は以下の通りである。

- XVC app にて記述されていた Zynq 内のメモリの大きさを、JATHub に搭載した Zynq の値に直した。

- Zynq デザイン例では、master Zynq1 台に対して slave 1 台を JTAG 制御するデザインとなっていた。これを最大 12 台 (PS board: 11 台, JATHub: 1台) の slave module に対して JTAG 制御できるように大幅な変更を加えた。

- PS board との接続では 15m の JTAG ケーブルを使用するので、ケーブルのデータ伝送によって 遅延時間が増え、同一のクロック位相内で Master と Slave 間のデータ通信ができなくなる。その ため、JTAG のクロック (TCK) 周波数を遅くしてクロック位相の幅を広げ、データが遅延しても 同一位相内で読めるようにした。尚、通信状態が安定する最も速い JTAG の TCK 周波数は、slave PS board: 2.5MHz、slave JATHub: 3.125MHz であった。TCK 周波数はこの値で設定した。ま た、EIL4 用 PS board との接続に 30 m の CAT6 ケーブルを使用するので、今後 30 m の CAT6 ケーブルでの JTAG 通信試験も行う。

- master Zynq が自らの configuration bank に接続し、master Zynq 内の信号線の様子を debug できる "Debug Bridge"という機能も、XVC の仕組みを利用することで実装できた。詳細は H 章。

#### 4.3.1.2 XVC の動作試験

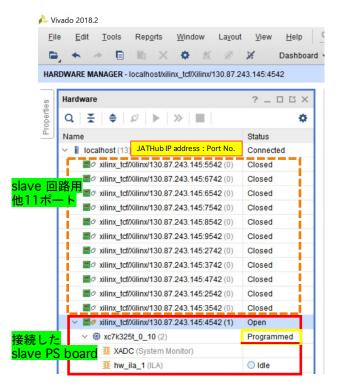

図 4.2 の KEK テストベンチを使用して、XVC の動作試験を実施した。master JATHub で、XVC app を走らせ、HostPC で開いている Vivado HM から slave JATHub と slave PS board の操作を試みた。図 4.8、図 4.9、図 4.10 が Vivado HM の GUI 画面である。

- ■Hub 機能を持った slave module の configuration XVC を使用して slave module を Vivado HM に認識させるには、まず master JATHub の 'IP address' を指定し、master JATHub のどのポート (図 4.3) を開けるか 'Port No.' を指定した。すると、Vivado HM にて、図 4.8 のように slave module 全 12 台分のポートで接続準備が完了した。ここで、一度に接続して JTAG 通信を行えるポートは 1 つだけであった。また、実際に slave PS board 試作機を CAT6 ケーブルで繋げているポートを開けると、PS board の FPGA(Kintex-7) を正常に認識した。この Kintex-7 に新たな Firmware を 'Program'(図 4.8) することもできた。CAT6 ケーブルを他のポートに付け直して同様の試験を行い、PS board 用の全 11 ポートにおいて XVC の機能が使えることが確認できた。

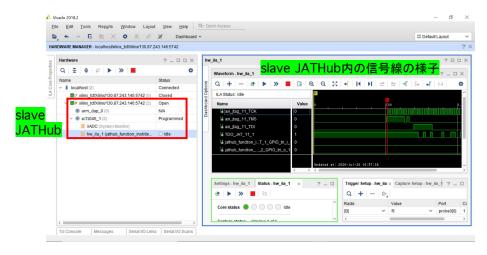

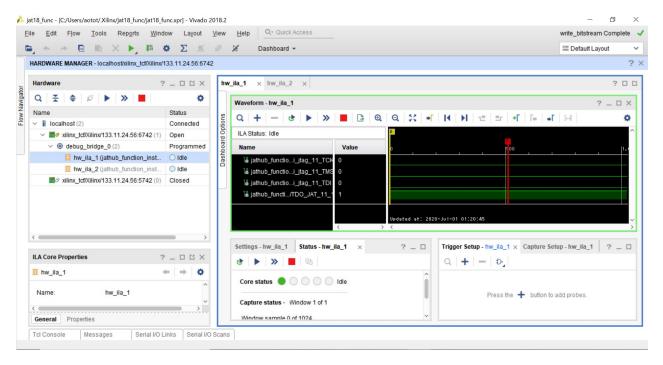

- ■slave JATHub の認識と ILA の使用 slave JATHub 第 1 試作機も PS board と同様に Vivado HM に おいて認識した。更に、この接続では、slave JATHub の Zynq 内で駆動している信号線の様子を、図 4.9

図 4.8 XVC によるハブ機能付き configuration。Vivado HM において、Hub 機能を持ってポートを開通でき、接続した slave module は正常に configuration した。

のように、ILA にて確認し、成功した。図 4.9 の ILA では slave JATHub がドライブできる JTAG パス の信号線をプローブしてみた。 $TCK(JTAG\ のクロック)$  の立ち上がりをトリガーし、 $JTAG\ 線の信号の 変動を捉えることができた。また、<math>JTAG4$  線の下にある 2 つの信号線は、JATHub 間の Recovery パス の MON 線の上り線と下り線を捉えている。JATHub の MON 線は特に PS から操作しない限り 0 信号をお互いに出力するようにしており、この設定を ILA で確認することができた。

従って、遠隔でもターゲット回路の信号線を ILA でプローブし、設計通りの挙動をしているか確認できることがわかった。

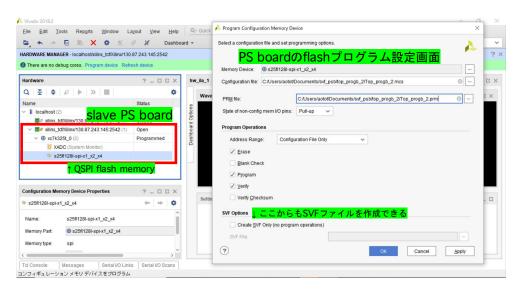

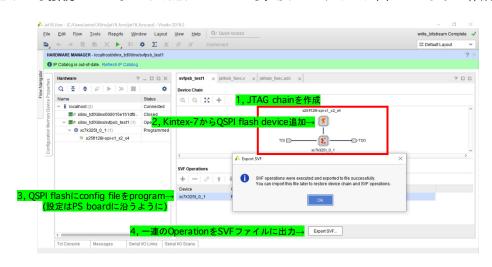

■QSPI flash memory をプログラム PS board 上の Kintex-7 に繋がっている QSPI flash memory に対して、XVC を使用して Vivado HM から configuration file をプログラムできるか確認した。結果、図 4.10 のように設定を行い、QSPI flash memory に新たな configuration file をプログラムすることができた。ここで、Hardware 欄で認識されている Kintex-7 を右クリックし QSPI device を追加してからプログラムを行った。また、図 4.10 の設定は、PS board のハードウェア設計に沿って決めたものである。

ただし、JATHub 上の Zynq-7000 に繋がっている QSPI flash memory に対しては、XVC 経由でプログラムすることができなかった (Zynq QSPI の使用詳細は 4.6 節)。14pin Ribbon Cable が付いた Platform Cable USB II で HostPC と JATHub を直接接続すると成功したが、この条件では本番環境にて遠隔で Zynq の QSPI flash memory をプログラムできない。XVC は Zynq QSPI のプログラムをサポートしていないので、遠隔で Zynq QSPI をプログラムする方法を確立する必要がある (5.1.3 節)。

図 4.9 XVC による ILA の使用。Vivado HM だからこそ使える機能の 1 つである ILA を使用して、 実際に slave JATHub の Zyng 内の信号線をプローブした。

図 4.10 XVC による QSPI flash memory のプログラム。PS board に対しては成功した。JATHub に対しては、Zynq QSPI Program が XVC でサポートされてないので失敗した。

### 4.3.2 SVF player

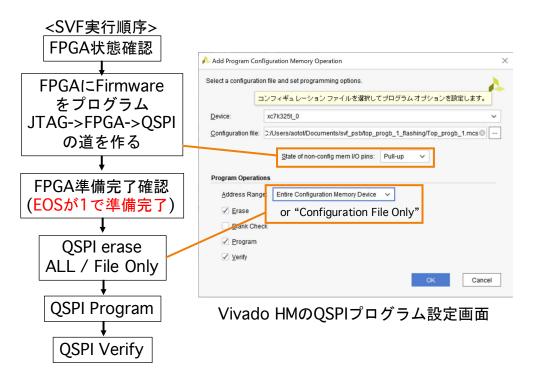

SVF(Serial Vector Format) ファイルは JTAG4 線をドライブするパターンを記述した ACSII(テキスト) ファイルである。JATHub では TCP/IP 通信を介さない JTAG 操作を可能にするために、図 4.7 の青字のように、SVF ファイルと SVF player を使って JTAG4 信号線をドライブし、slave module を操作する機能を設けた。ネットワーク経由 (SCP) で SD card に SVF ファイルを置き、Zynq Linux 上で走る SVF player アプリケーションがその SVF ファイルに従って bit-banging 形式で JTAG4 線を操作する。

#### 4.3.2.1 SVF player の開発と実装