# 修士学位論文

# LHC-ATLAS実験 Run 3 の開始に向けたミューオントリガー回路系の高速読み出しと統合制御の実現

(The Realization of High-Speed Readout and Integrated Control of the Muon Trigger System for LHC-ATLAS Experiment Run 3)

東京大学大学院 理学系研究科 物理学専攻素粒子物理国際研究センター 奥村研究室

杉崎海斗

2021年2月28日

Large Hadron Collider (LHC) は欧州原子核機構 (CERN) によって建設された世界最高エネルギーを誇る陽子陽子衝突型の円形加速器である。LHC-ATLAS 実験では、ATLAS 検出器を用いて陽子陽子衝突によって生成された粒子を観測することで、素粒子の標準模型の精密測定や標準模型を超える新物理の探索を行なっている。

陽子陽子衝突実験では衝突の全断面積が極端に大きい一方で、新物理によって予言される現象の断面積は一般にその全断面積よりも 12 桁以上も小さい。このような実験環境で限られた読み出し帯域とオフラインの計算リソースを最大限に活用するためには、重要な衝突事象のみをオンラインで選別するトリガーシステムが必要となる。 LHC-ATLAS 実験では、Level-1 トリガーという初段のハードウェアトリガーを用いて  $2.5~\mu s$  以内にトリガー判定を行い、事象レートを 40~MHz から 100~kHz まで落とす。その Level-1 トリガーの一種である Level-1 ミューオンエンドキャップトリガーでは、Thin Gap Chamber (TGC) 検出器を用いて陽子陽子衝突に由来するミューオンを検出し、概算したそれらの運動量を基に事象選別を行う。

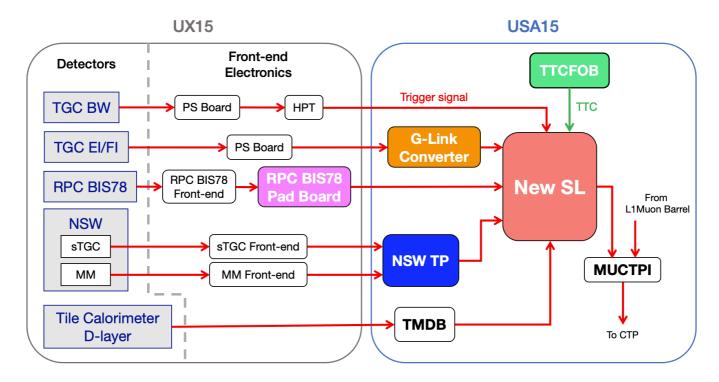

2021年1月現在、LHC-ATLAS 実験では第三期運転 (Run 3) に向けてアップグレード作業を進めている。特に Level-1ミューオンエンドキャップトリガーでは、陽子陽子衝突から生じたミューオンに由来しない偽のトリガー信号を削減するべく、New Small Wheel や RPC BIS78という新しいミューオントリガー検出器を導入する。これらの検出器の導入に伴い、トリガー判定を担うエレクトロニクスも新たに開発された。その中核をなす 72 台の New Sector Logic (New SL) ボードは、5 種類の検出器エレクトロニクスからミューオンのヒット情報を受信し、Level-1ミューオンエンドキャップトリガーの最終的なトリガー判定を出力する。またこのトリガーの性能をオフラインで評価するために、Software-based ROD (SROD) という新たな読み出しソフトウェアを用いることで、New SL のトリガー論理回路の入出力データを読み出す。

本研究では全72台の New SL を中心とする Level-1 ミューオンエンドキャップトリガーの新しいエレクトロニクスを同期制御するためのオンラインソフトウェアを開発し、システム全体の統合制御を実現した。まずは New SLを中心とした新しいエレクトロニクスやソフトウェアアプリケーションを ATLAS 検出器の制御系に組み込むために、対応するオブジェクトおよびそれらの依存関係を ATLAS のソフトウェアデータベースである Object Kernel Support (OKS) に定義した。次に、各エレクトロニクスの初期化やエレクトロニクス間の光通信リンクの確立を正しい手順で行えるように、エレクトロニクス制御アプリケーションを開発した。これらの OKS とソフトウェアアプリケーションの開発によって、Run 3 の新しい Level-1 ミューオンエンドキャップトリガーシステムが Run 2 でも使用していた TGC の検出器システムと同期して制御できるようになった。さらに新しいエレクトロニクスのモニタリング機能を実装することで、検出器システムの誤動作やその兆候を検知できるようにし、高い堅牢性を持つシステムを構築した。このような形で統合制御システムを開発することで、New SL を中心とした大規模システムを運転制御できるようにし、Run 3 に向けたコミッショニングを大幅に加速させた。

また新しいトリガーデータ読み出しソフトウェアである SROD を開発することで、100 kHz におけるデータ読み出しを実現し、検出器フロントエンドから CERN のコンピューティングセンターまでのデータ読み出しパスを確立した。はじめに、ATLAS 回路室に新たに導入された全 6 台の PC 上で、ATLAS 検出器の制御系の一部として SROD が起動するように、SROD の OKS とソフトウェアアプリケーションを開発した。さらに幾度にもわたる試験と性能改善を通して、100 kHz でのトリガーデータの読み出しを可能にするとともに、安定した動作を保証する ための機能を実装した。最後に、本研究で開発した SROD ソフトウェアおよび確立した読み出しパス全体の性能評価を行うことで、これらが Run 3 の物理ランで安定動作するために十分な性能を持つことを確認した。これらの開発研究を通して、Run 3 に向けた Level-1 ミューオンエンドキャップトリガーシステムの高速読み出しと統合制御を実現した。

# 目次

| 第1章   | 序論                                                                                                          | 1  |

|-------|-------------------------------------------------------------------------------------------------------------|----|

| 第2章   | LHC-ATLAS 実験が目指す物理                                                                                          | 3  |

| 2.1   | 素粒子の標準模型                                                                                                    | 3  |

|       | 2.1.1 標準模型の概要                                                                                               | 3  |

|       | 2.1.2 標準模型が抱える問題点                                                                                           | 5  |

| 2.2   | 標準模型を超える物理                                                                                                  | 6  |

|       | 2.2.1 超対称性                                                                                                  | 6  |

|       | 2.2.2 余剰次元                                                                                                  | 8  |

| 第3章   | LHC-ATLAS 実験                                                                                                | 10 |

| 3.1   | LHC 加速器                                                                                                     | 10 |

| 3.2   | ATLAS 検出器                                                                                                   | 12 |

|       | 3.2.1 座標系                                                                                                   | 12 |

|       | 3.2.2 超伝導電磁石                                                                                                | 13 |

|       | 3.2.3 内部飛跡検出器                                                                                               | 14 |

|       | 3.2.4 カロリメータ                                                                                                | 15 |

|       | 3.2.5 ミューオンスペクトロメータ                                                                                         | 15 |

|       | 3.2.6 トリガーシステム                                                                                              | 20 |

|       | 3.2.7 Timing, Trigger and Control (TTC) システム                                                                | 21 |

| 第 4 章 | Level-1 ミューオンエンドキャップトリガー                                                                                    | 24 |

| 4.1   | Run 2 における Level-1 ミューオンエンドキャップトリガー                                                                         | 24 |

|       | 4.1.1 TGC Big Wheel のトリガーセクターと RoI                                                                          | 24 |

|       | 4.1.2 TGC Big Wheel におけるトリガーの概要                                                                             | 24 |

|       | 4.1.3 トリガーエレクトロニクスとそのロジック                                                                                   | 25 |

|       | 4.1.4 TGC の読み出しエレクトロニクス                                                                                     | 31 |

|       | 4.1.5 TGC のフロントエンド回路制御システム                                                                                  | 32 |

|       | 4.1.6 TGC の TTC システム                                                                                        | 33 |

| 4.2   | Level-1 $\exists$ | 34 |

|       | 4.2.1 New Small Wheel (NSW)                                                                                 | 35 |

|       | 4.2.2 RPC BIS78                                                                                             | 37 |

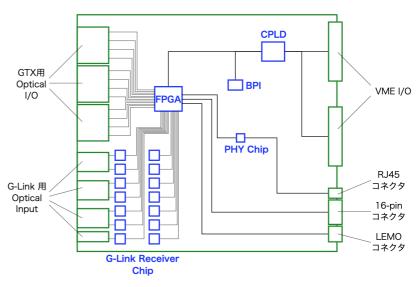

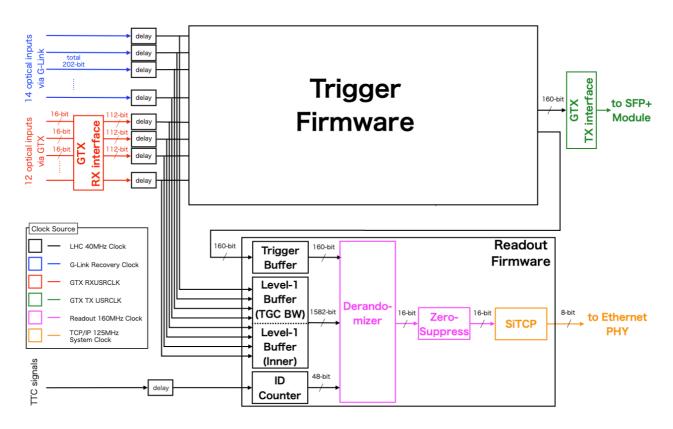

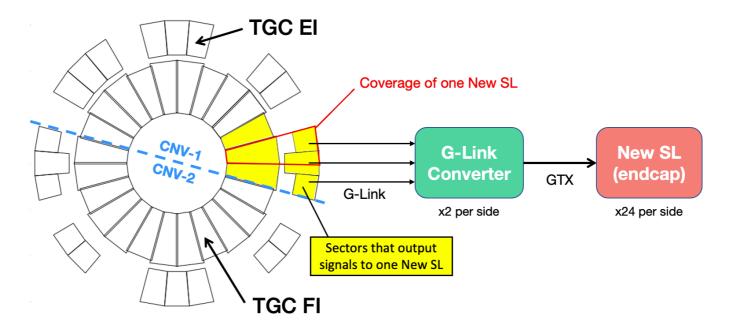

|       | 4.2.3 新しいトリガーエレクトロニクス                                                                                       | 38 |

|       | 4.2.4 トリガーデータ読み出しシステムのアップグレード                                                                               | 43 |

| 第5章   | Level-1 ミューオンエンドキャップトリガーの統合制御の実現                                                                            | 47 |

| 5.1   | ATLAS TDAQ ソフトウェア                                                                                           | 47 |

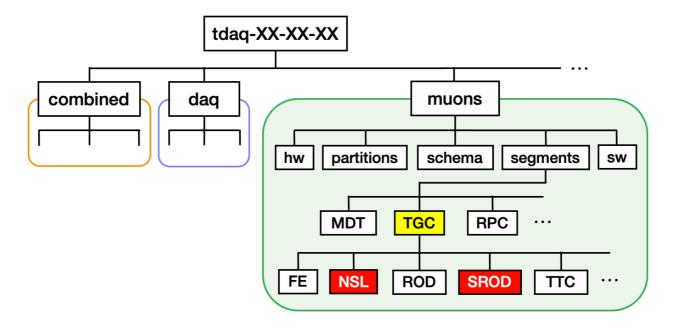

|     | 5.1.1  | OKS データベースの概要と検出器システムの階層構造                                   | 48  |

|-----|--------|--------------------------------------------------------------|-----|

|     | 5.1.2  | TDAQ の Run Control State と State Transition                  | 50  |

|     | 5.1.3  | オンラインモニタリング                                                  | 51  |

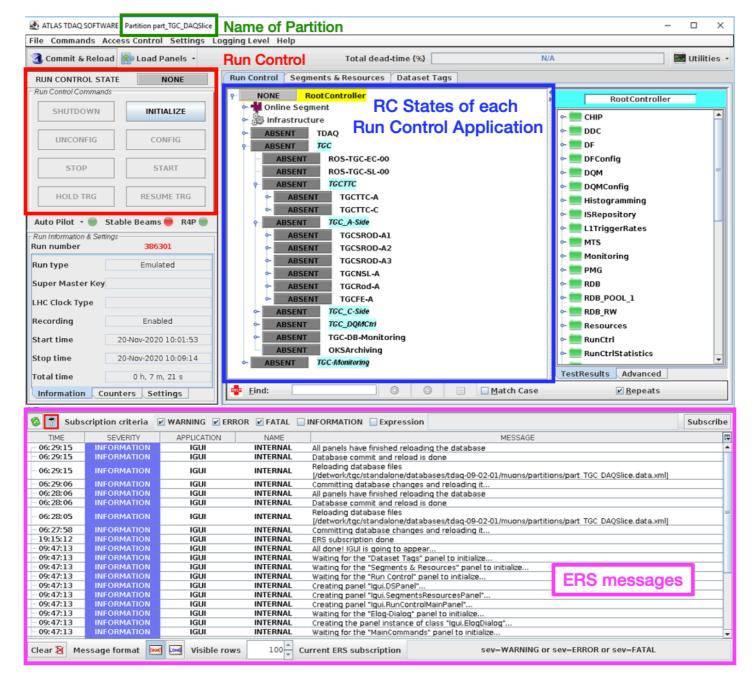

|     | 5.1.4  | Run Control Panel を用いた検出器システムの運転                             | 54  |

| 5.2 | オンラ    | インソフトウェアによる Level-1 ミューオンエンドキャップトリガーと TGC の制御の全体像            | 54  |

|     | 5.2.1  | Level-1 ミューオンエンドキャップトリガーと TGC のオンラインソフトウェアに                  |     |

|     |        | 要求される機能                                                      | 55  |

|     | 5.2.2  | 制御に用いる PC と SBC                                              | 56  |

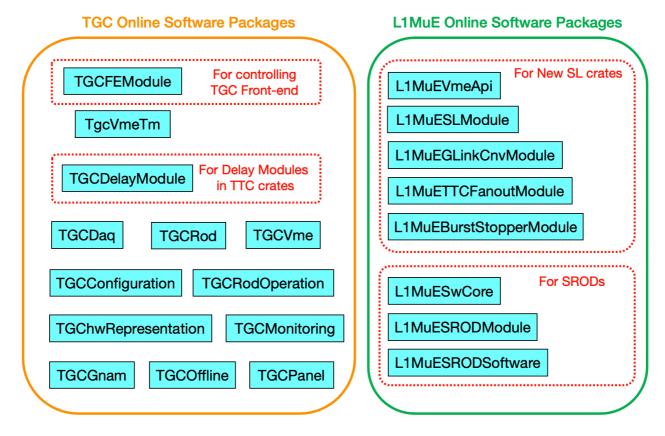

|     | 5.2.3  | 制御に必要なオンラインソフトウェアパッケージ                                       | 58  |

| 5.3 | Level- | 1 ミューオンエンドキャップトリガーおよび TGC の OKS の開発                          | 60  |

|     | 5.3.1  | $\operatorname{Run} 3$ の新規エレクトロニクスを制御するための OKS の開発 $\dots$   | 60  |

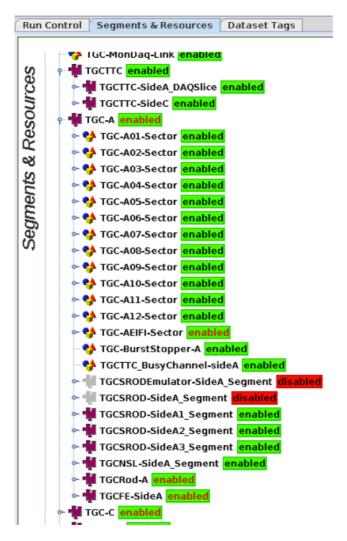

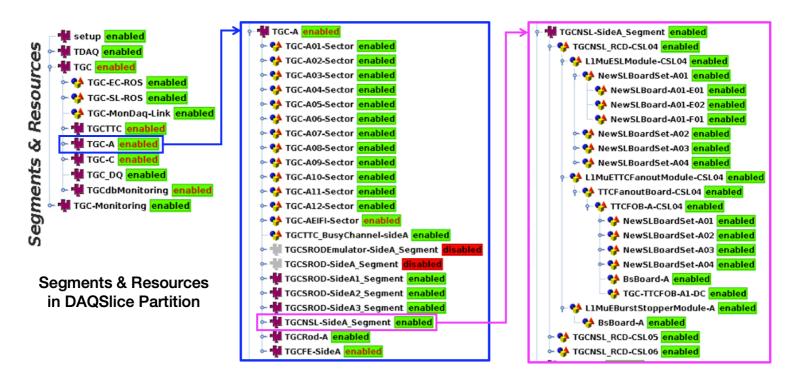

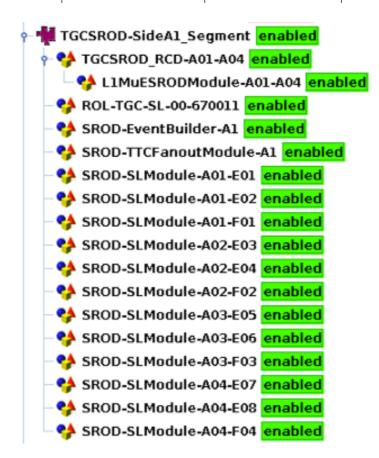

|     | 5.3.2  | Segments & Resources を用いたシステムの階層構造の開発                        | 61  |

| 5.4 | Run 3  | に向けた State Transition の考案とオンラインソフトウェアへの実装                    | 63  |

| 5.5 | モニタ    | リング機能の開発                                                     | 66  |

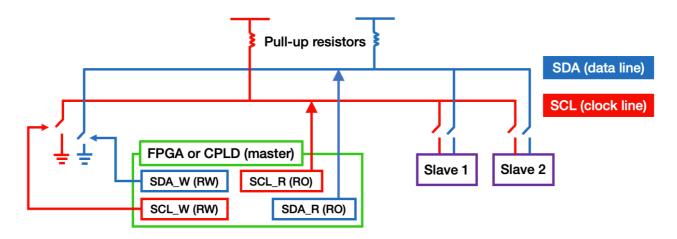

|     | 5.5.1  | I <sup>2</sup> C 通信の概要                                       | 66  |

|     | 5.5.2  | TTCrx のコンフィギューレーションとモニタリング機能の開発                              | 66  |

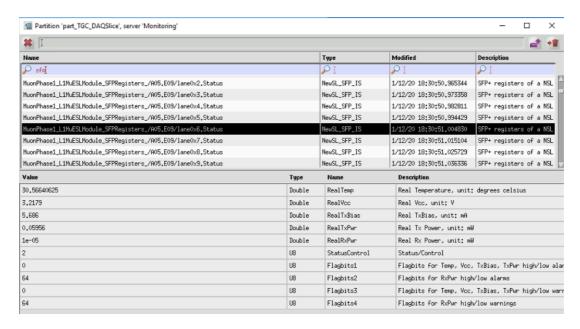

|     | 5.5.3  | SFP+ 光トランシーバのモニタリング機能の開発                                     | 68  |

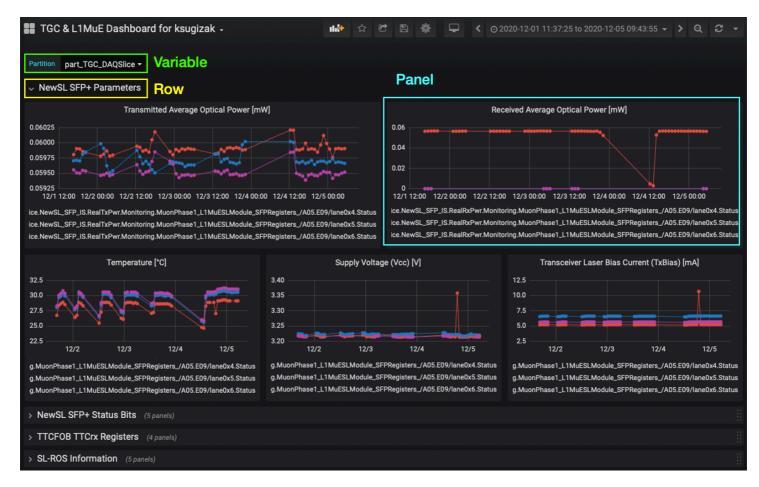

|     | 5.5.4  | Grafana を用いたオンラインモニタリングの実現                                   | 70  |

| 5.6 | 新たに    | 開発した統合制御システムの現状と今後                                           | 72  |

| 第6章 | Level- | 1 ミューオンエンドキャップトリガーの高速読み出しシステムの開発                             | 74  |

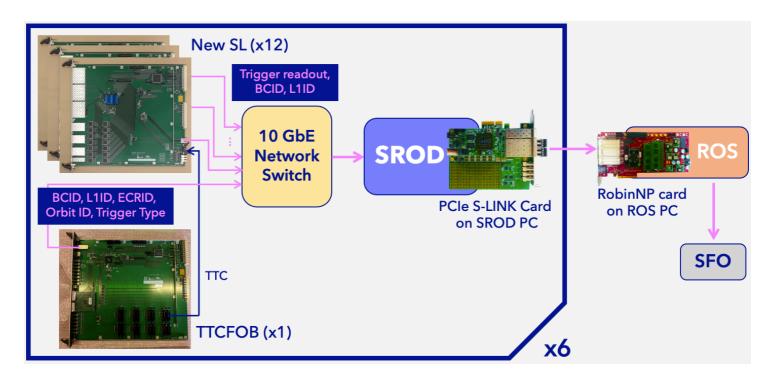

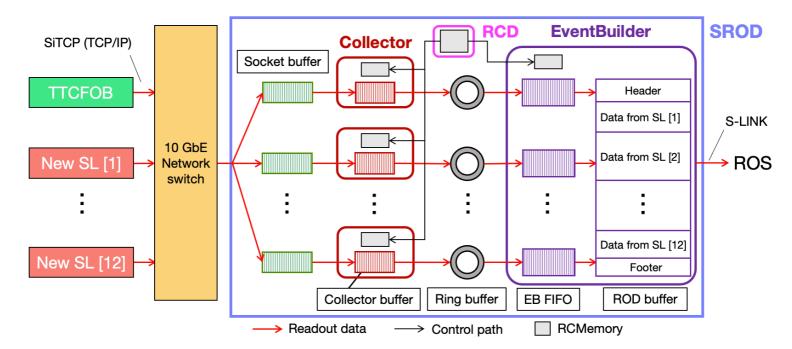

| 6.1 | Softwa | are-based ROD (SROD) の導入                                     | 74  |

|     | 6.1.1  | トリガーデータ読み出しパスの全体像と SROD ソフトウェアの要求性能                          | 74  |

|     | 6.1.2  | SROD ソフトウェアの構造                                               | 75  |

| 6.2 | OKS    | とソフトウェアアプリケーションの相互開発による読み出しパスの開通                             | 78  |

|     | 6.2.1  | OKS の開発による SROD の全台制御の実現                                     | 78  |

|     | 6.2.2  | ソフトウェアアプリケーションの開発による $100~\mathrm{kHz}$ でのデータ読み出しの実現 $\dots$ | 82  |

| 6.3 | Busy   | 信号の出力処理の実装による CTP とのハンドシェイクの実現                               | 84  |

|     | 6.3.1  | Busy 線の配線                                                    | 85  |

|     | 6.3.2  | OKS における busy 線の定義                                           | 85  |

|     | 6.3.3  | SROD ソフトウェアを用いた busy 信号の出力処理の実装                              | 86  |

|     | 6.3.4  | SROD ソフトウェアを用いた busy 信号の出力処理の動作検証                            | 87  |

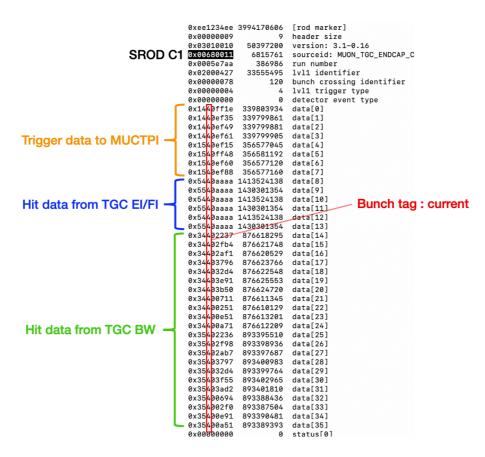

| 6.4 | トリガ    | 一読み出しデータのフォーマットの検討                                           | 88  |

|     | 6.4.1  | SROD の入力データ                                                  | 89  |

|     | 6.4.2  | SROD の出力データ                                                  | 91  |

| 6.5 | L1A l  | ノートが低い場合における読み出しパスの安定性の検証                                    | 93  |

|     | 6.5.1  | L1A レートが低い場合における動作検証試験について                                   | 93  |

|     | 6.5.2  | L1A レートが低い場合に生じる読み出しパスの遅延の原因                                 | 94  |

|     | 6.5.3  | L1A レートが低い場合に生じる読み出しパスの遅延時間の短縮方法の提案と実装                       | 95  |

| 6.6 | SROD   | ) の性能評価                                                      | 96  |

|     | 6.6.1  | SROD 単独の性能                                                   | 98  |

|     | 6.6.2  | 読み出しパス全体の性能                                                  | 103 |

| 6.7 | SROD   | )を用いた統合的なコミッショニングの現状                                         | 108 |

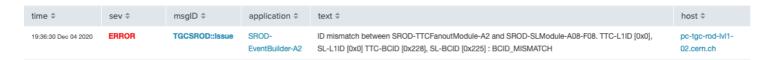

|     | 6.7.1  | Milestone Week における読み出しパスのバリデーション                            | 109 |

|       | 6.7.2 New SL および TTCFOB の BCR delay の調節         |     |

|-------|-------------------------------------------------|-----|

| 第7章   | 結論と今後の展望                                        |     |

| 弗 / 早 | 指冊と今後の成業<br>                                    | 114 |

| 謝辞    |                                                 | 115 |

| 付録 A  | 理論の補足                                           | 117 |

| A.1   | パウリ行列、ゲルマン行列、ガンマ行列                              | 117 |

| A.2   | 素粒子の標準模型の補足・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ | 117 |

|       | A.2.1 電弱統一理論とヒッグス機構                             | 117 |

|       | A.2.2 量子色力学                                     | 121 |

| 付録 B  | ATLAS 検出器の補足                                    | 123 |

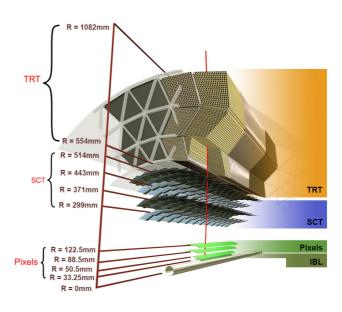

| B.1   | 内部飛跡検出器                                         | 123 |

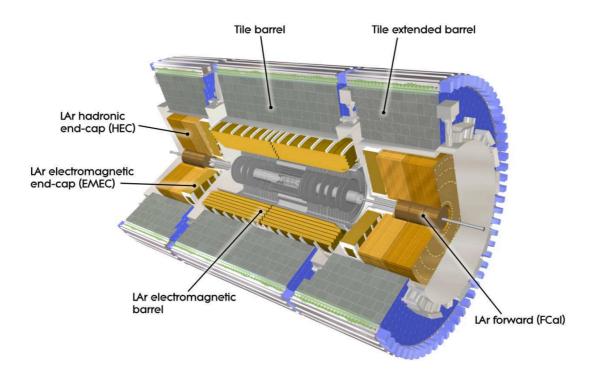

| B.2   | カロリメータ                                          | 124 |

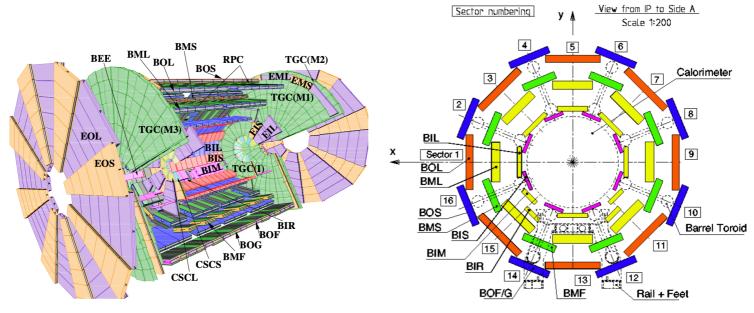

| B.3   | TGC 以外のミューオンスペクトロメータ                            | 127 |

| 付録 C  | OKS データベースの詳細                                   | 131 |

| C.1   | OKS のオブジェクト                                     | 131 |

| C.2   | OKS データベースの制御                                   | 132 |

| C.3   | Level-1 ミューオンエンドキャップトリガーおよび TGC の OKS の詳細       | 133 |

|       | C.3.1 OKS データベースのファイル構造                         | 133 |

|       | C.3.2 New SL クレートを制御するために開発した OKS の詳細           | 134 |

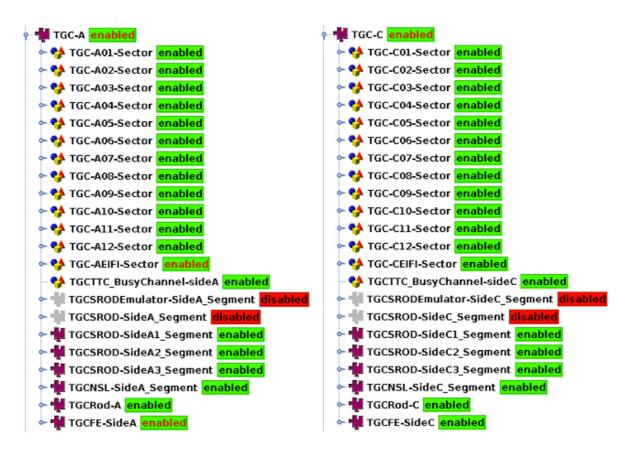

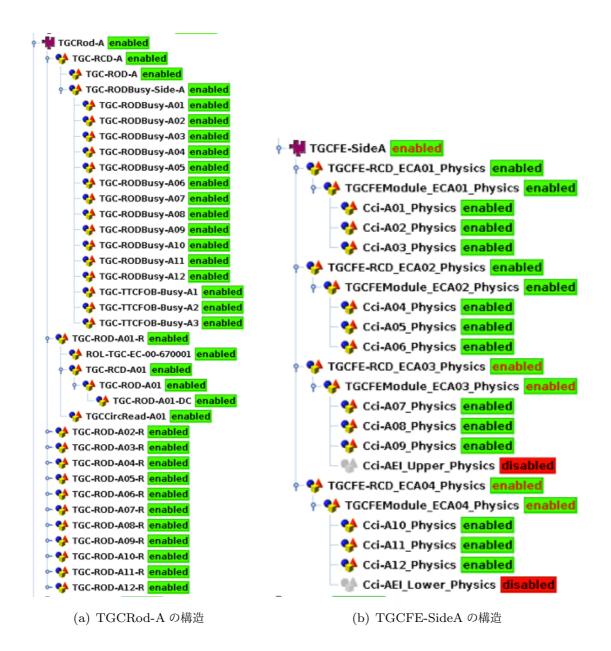

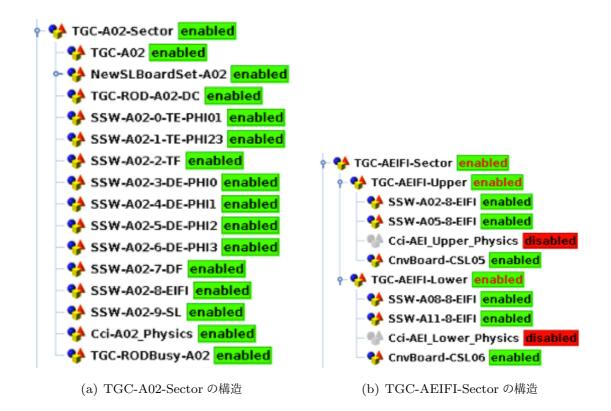

|       | C.3.3 TGC の Segments & Resources の全体的な吟味と再編     | 136 |

| 付録 D  | State Transition やモニタリング機能についての補足               | 141 |

| D.1   | TTC Restart の実装方法                               | 141 |

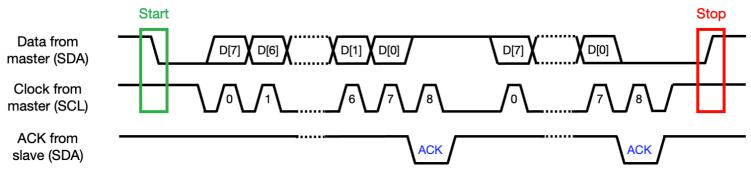

| D.2   | ${ m I}^2{ m C}$ の具体的な通信手順                      | 141 |

| D.3   | TTCrx の I2C_ID の特定方法                            | 142 |

| 付録 E  | 高速読み出しシステムの開発の補足                                | 144 |

| E.1   | トリガーデータ読み出しフォーマットの補足: $New~SL$ の入出力データ $\dots$  | 144 |

|       | E.1.1 New SL の入力データ:各検出器エレクトロニクスから受信するトラック情報    | 144 |

|       | E.1.2 New SL の出力データ:MUCTPI に送信するトリガー判定情報        | 147 |

| E.2   | L1A レートが低い場合に生じる読み出しパスの遅延の原因調査の詳細               | 147 |

| E.3   | L1A レートが低い場合に生じる読み出しパスの遅延時間の短縮方法の検証             | 148 |

| 参考文献  |                                                 | 150 |

# 図目次

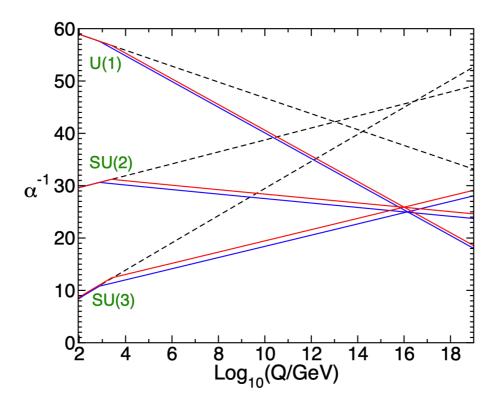

| 2.1  | MSSM におけるゲージ結合定数の統一                                             | 8  |

|------|-----------------------------------------------------------------|----|

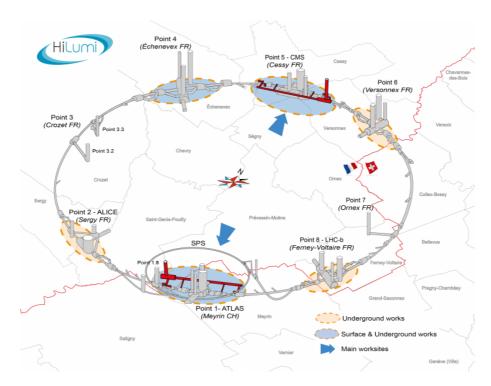

| 3.1  | LHC 加速器の俯瞰図                                                     | 10 |

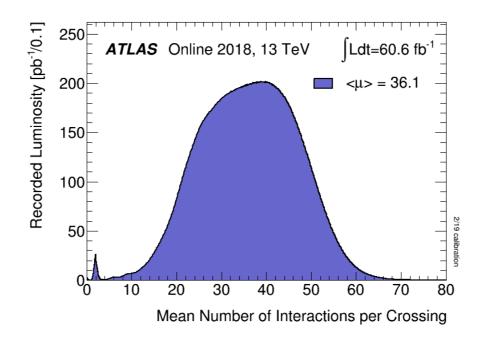

| 3.2  | 2018 年の各バンチ交差における陽子の平均衝突回数の分布                                   | 11 |

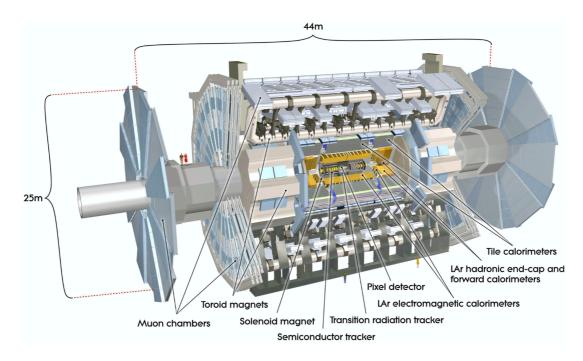

| 3.3  | ATLAS 検出器の全体図                                                   | 12 |

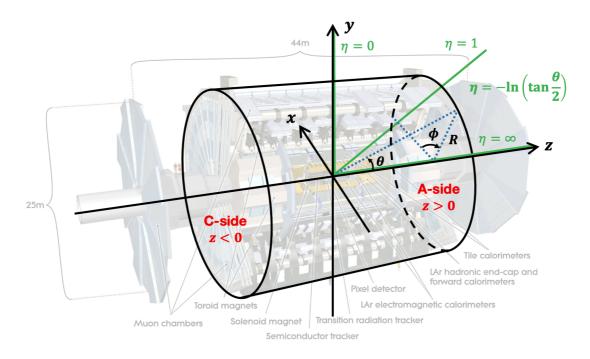

| 3.4  | ATLAS 検出器の座標系                                                   | 13 |

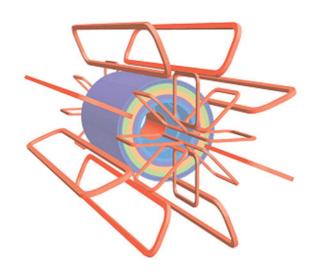

| 3.5  | ATLAS 検出器の超伝導電磁石                                                | 14 |

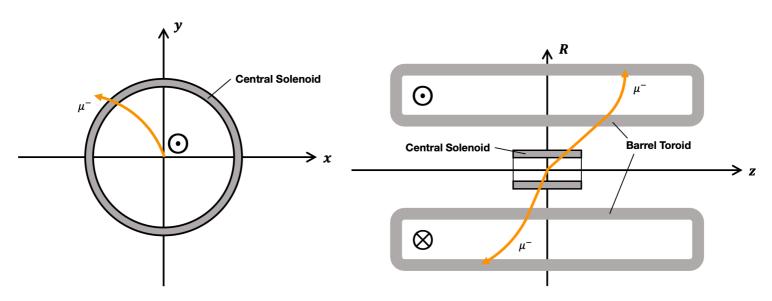

| 3.6  | ATLAS 検出器内における $\mu^-$ の飛跡                                      | 14 |

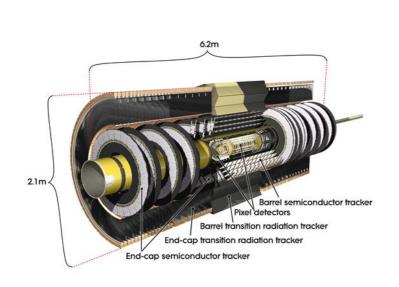

| 3.7  | 内部飛跡検出器の概要                                                      | 15 |

| 3.8  | ATLAS 検出器のカロリメータの断面図                                            | 16 |

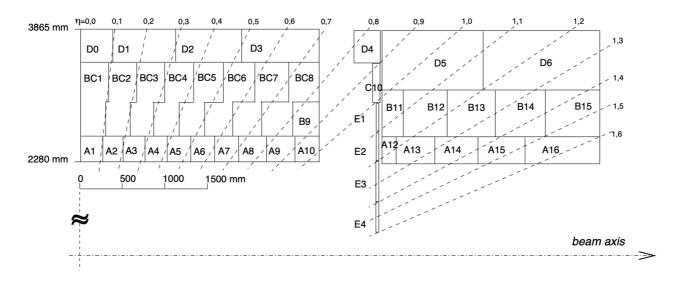

| 3.9  | Tile Calorimeter の層の配置                                          | 16 |

| 3.10 | ミューオンスペクトロメータの各検出器の配置                                           | 17 |

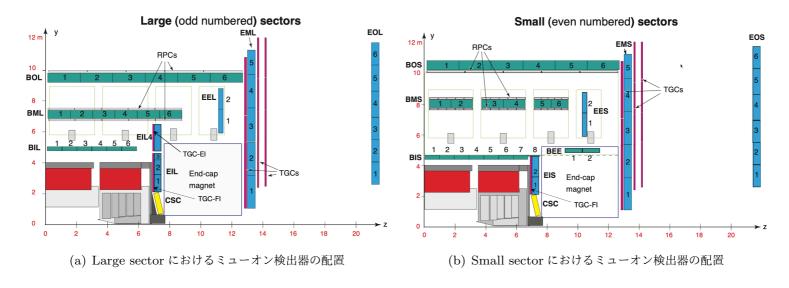

| 3.11 | ミューオンスペクトロメータの large sector と small sector における検出器の配置           | 17 |

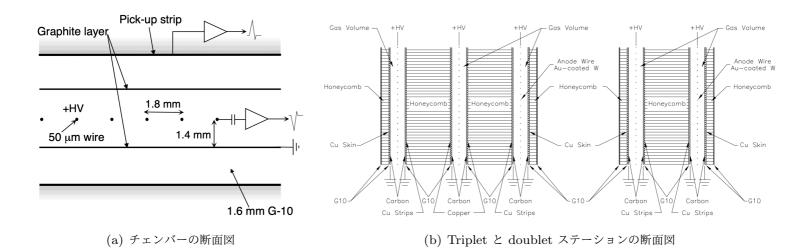

| 3.12 | TGC のチェンバーとステーションの構造                                            | 18 |

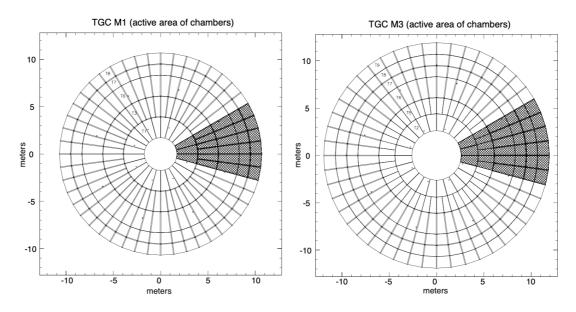

| 3.13 | TGC Big Wheel $\mathcal O$ unit                                 | 18 |

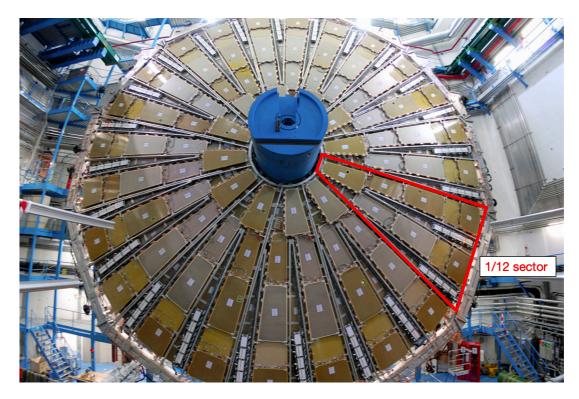

| 3.14 | TGC の全体写真と 1/12 セクター                                            | 19 |

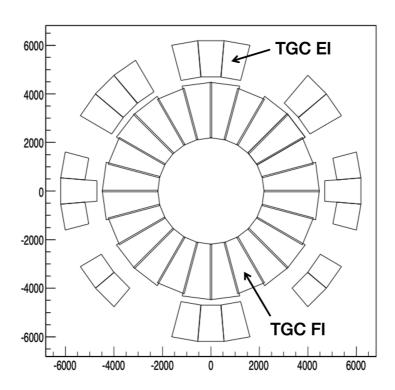

| 3.15 | TGC EI と FI のチェンバーの配置                                           | 19 |

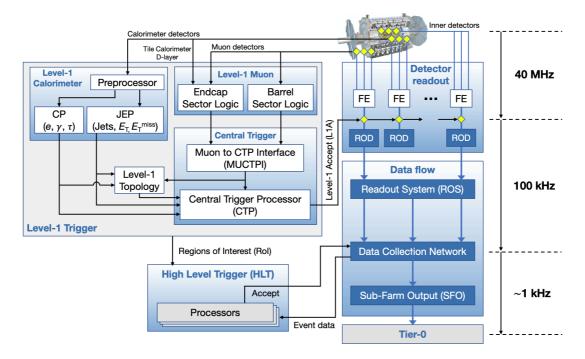

| 3.16 | Run 2 における ATLAS の TDAQ システム                                    | 20 |

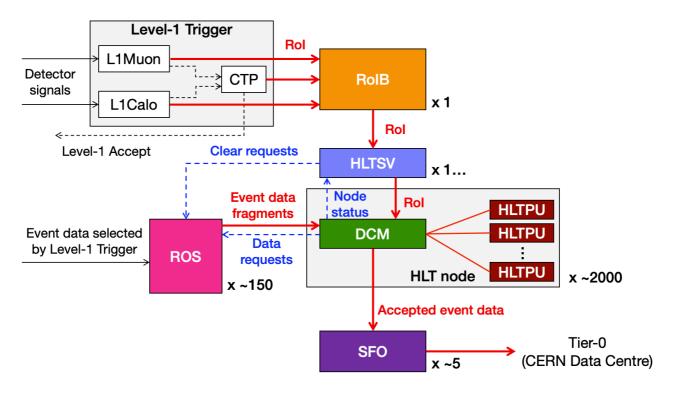

| 3.17 | HLT と後段データフローの概念図                                               | 22 |

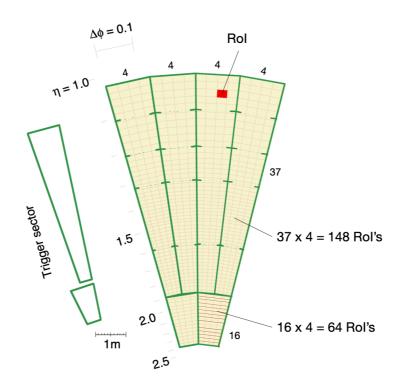

| 4.1  | TGC Big Wheel の $1/12$ セクターにおけるトリガーセクターと RoI                    | 25 |

| 4.2  | TGC Big Wheel のトリガーロジックの概念図                                     | 25 |

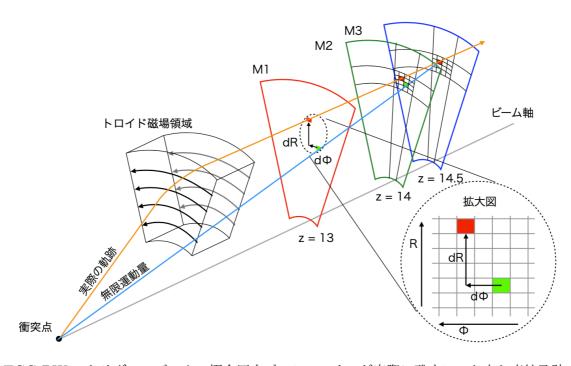

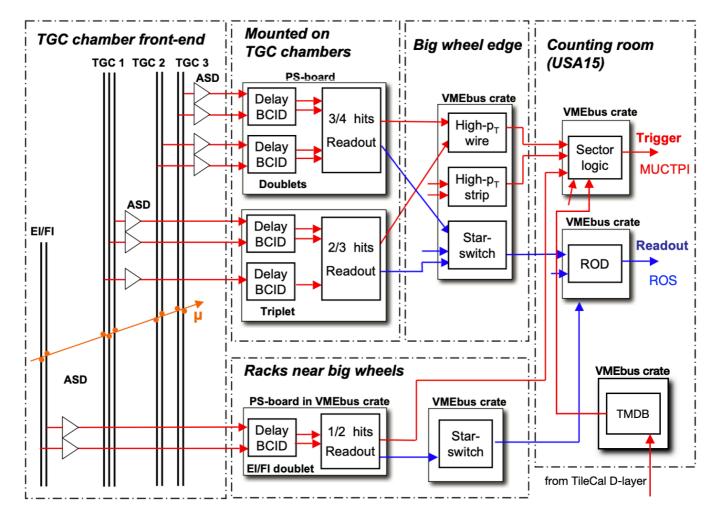

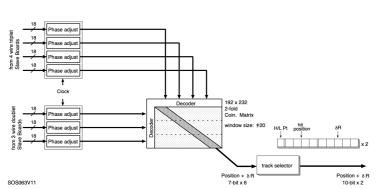

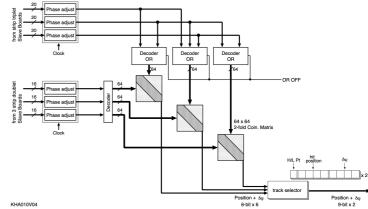

| 4.3  | Run 2 における Level-1 ミューオンエンドキャップトリガーのトリガーロジックの概要 $\dots$         | 26 |

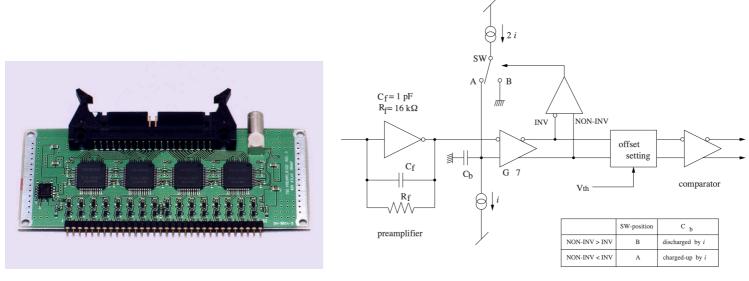

| 4.4  | ASD の概要                                                         | 27 |

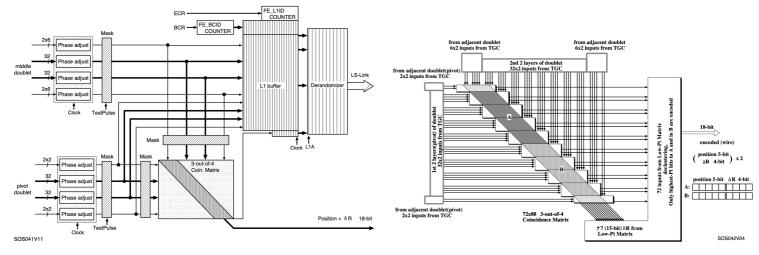

| 4.5  | Doublet ワイヤー用の SLB ASIC の概要                                     | 28 |

| 4.6  | ${ m High}$ - $p_{ m T}$ ボードの概要                                 | 29 |

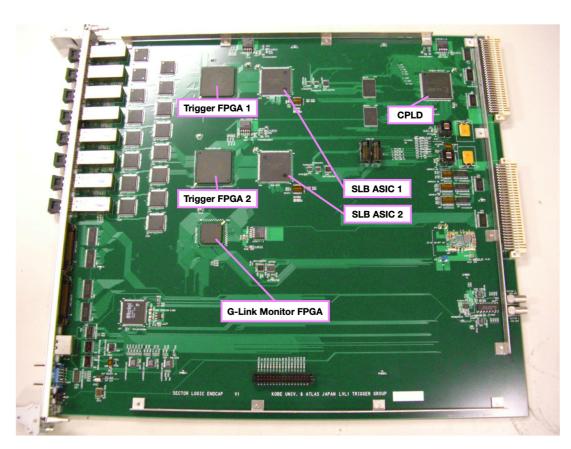

| 4.7  | Run 2 で用いたエンドキャップ用 SL の写真                                       | 29 |

| 4.8  | TGC ROD の写真                                                     | 31 |

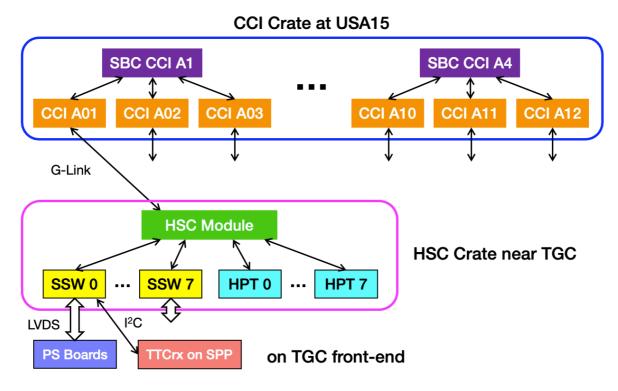

| 4.9  | TGC のフロントエンド回路制御システムの概要                                         | 32 |

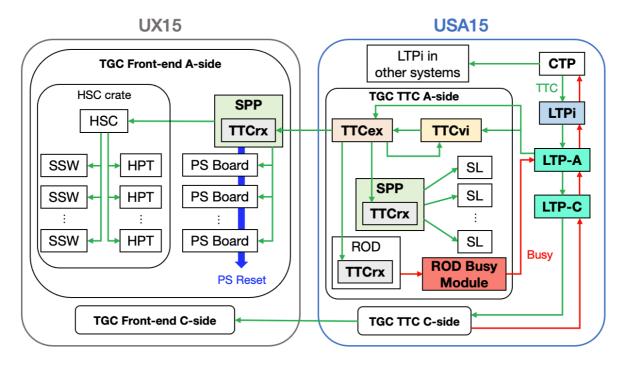

| 4.10 | Level-1 ミューオンエンドキャップトリガーおよび TGC の TTC システムの概要                   | 33 |

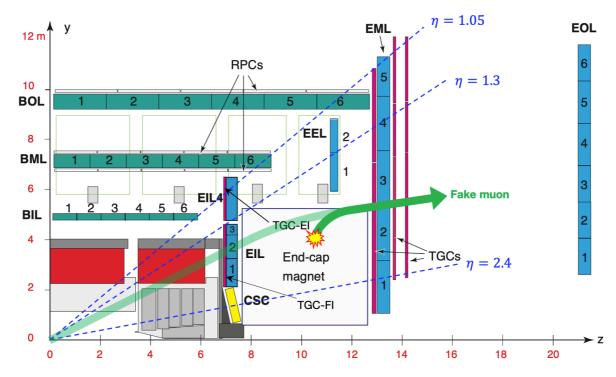

| 4.11 | Level-1 ミューオンエンドキャップトリガーにおけるフェイクトリガーの模式図                        | 35 |

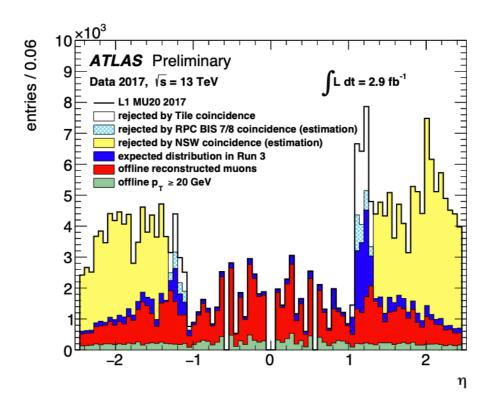

| 4.12 | Run $3$ における Level- $1$ ミューオントリガーを用いて選出したミューオン候補数の $\eta$ 分布の予測 | 36 |

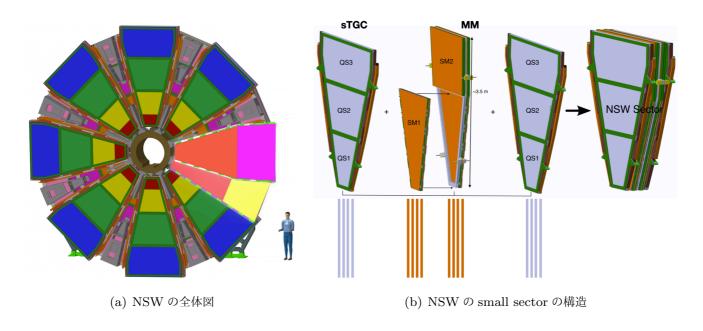

| 4.13 | New Small Wheel の概要                                             | 36 |

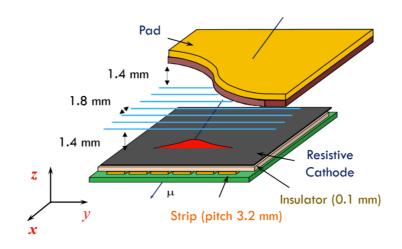

| 4.14 | sTGC 検出器の構造                                                     | 37 |

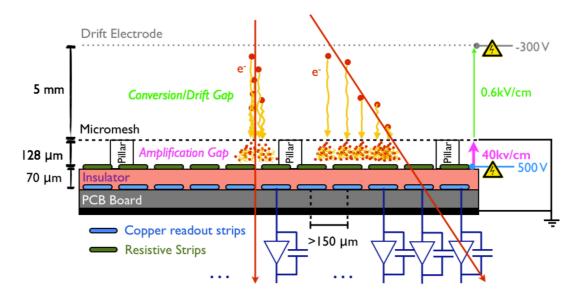

| 4.15 | Micromegas の動作原理の模式図                                            | 38 |

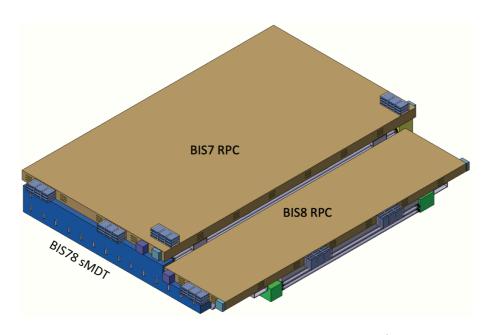

| 4.16 | Run 3 から設置される BIS78 ステーション                                      | 38 |

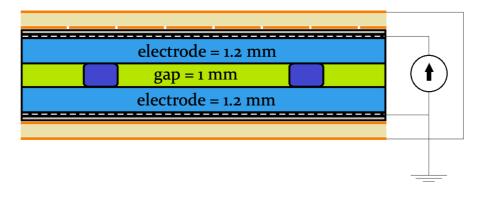

| 4.17 | RPC BIS78 の 1 層の断面図                                                    | 39 |

|------|------------------------------------------------------------------------|----|

| 4.18 | Run $3$ の Level- $1$ ミューオンエンドキャップトリガーシステムの全体像                          | 39 |

| 4.19 | New Sector Logic の主な機能                                                 | 40 |

| 4.20 | New Sector Logic の FPGA ファームウェアの全体像                                    | 41 |

| 4.21 | TGC EI/FI のチェンバーと G-Link Converter の関係                                 | 42 |

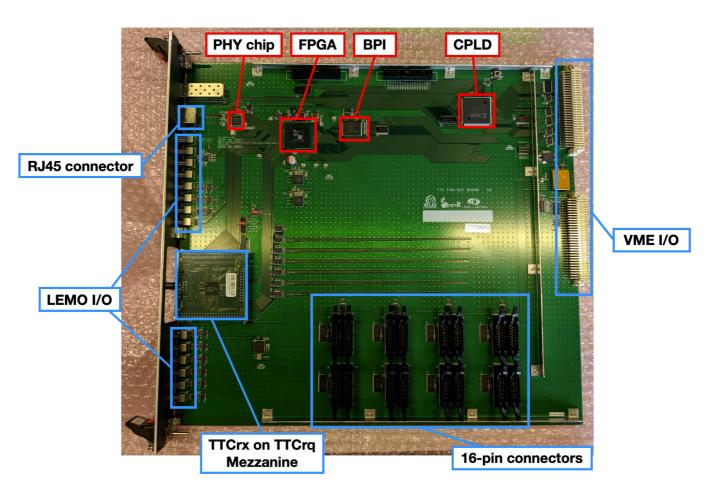

| 4.22 | TTC Fanout Board の主なチップと I/O                                           | 42 |

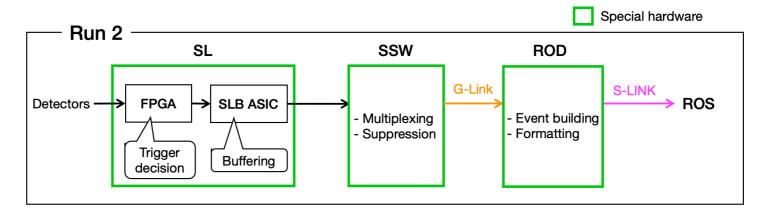

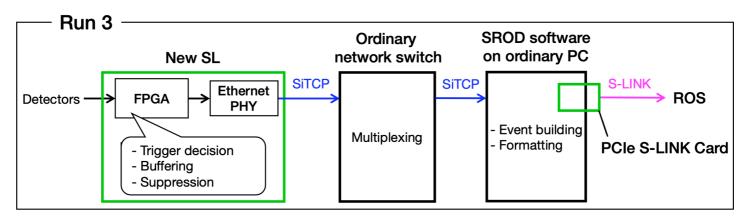

| 4.23 | Level-1 ミューオンエンドキャップトリガーのデータ読み出しシステムの $\operatorname{Run}$ $3$ アップグレード | 44 |

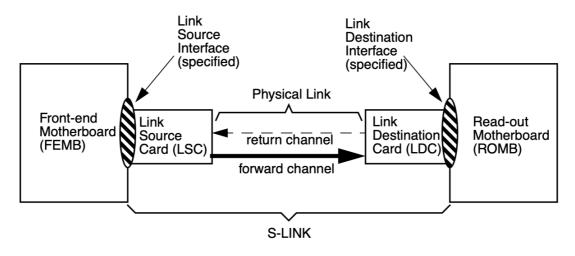

| 4.24 | S-LINK 通信の概念図                                                          | 45 |

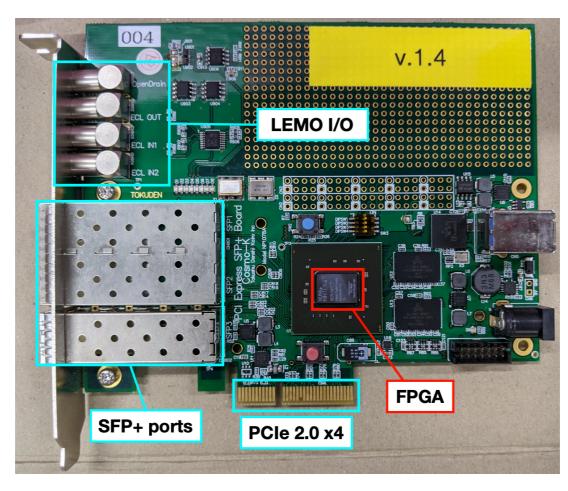

| 4.25 | Run 3 に向けて新たに開発された PCIe S-LINK Card                                    | 46 |

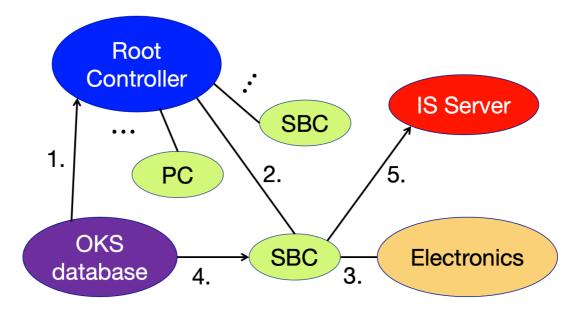

| 5.1  | TDAQ ソフトウェアの動作手順                                                       | 48 |

| 5.2  | OKS の schema ファイルと data ファイルの一例                                        | 49 |

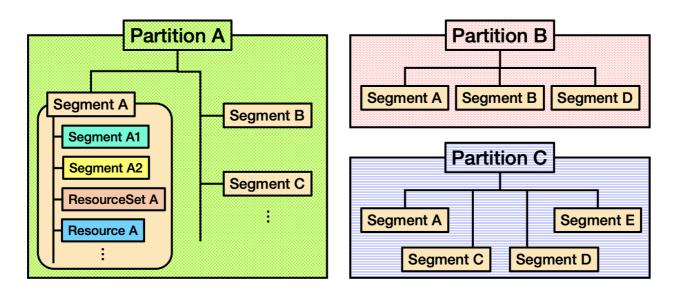

| 5.3  | OKS を用いた検出器システムの階層構造の模式図                                               | 50 |

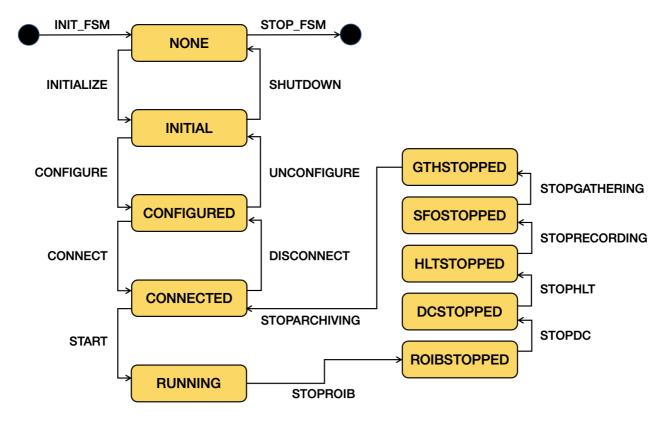

| 5.4  | TDAQ ソフトウェアの Run Control Finite State Machine                          | 51 |

| 5.5  | Information Service $\mathcal O$ GUI                                   | 53 |

| 5.6  | Error Reporting Service のメッセージの一例                                      | 53 |

| 5.7  | TDAQ ソフトウェアの Run Control Panel                                         | 55 |

| 5.8  | Run Control Panel から見た Segments & Resources                            | 56 |

| 5.9  | USA15 における Level-1 ミューオンエンドキャップトリガーの PC と SBC およびモジュールの配置              | 57 |

| 5.10 | USA15 の New SL クレートの写真                                                 | 57 |

| 5.11 | Level-1 ミューオンエンドキャップトリガーおよび TGC のオンラインソフトウェアパッケージの一覧                   | 59 |

| 5.12 | New SL の OKS オブジェクトの定義                                                 | 61 |

| 5.13 | DAQSlice Partition の Segments & Resources と New SL クレートのエレクトロニクスを制御す   |    |

|      | る Segment                                                              | 62 |

| 5.14 | Run 3 の State Transition の全体像                                          | 64 |

| 5.15 | $ m I^2C$ の通信方式の模式図 $ m$                                               | 67 |

| 5.16 | TTC Fanout Board の TTCrx のレジスタの OKS 設定値                                | 68 |

| 5.17 | DAQSlice Partition における PBEAST モニタリングの実装                               | 70 |

| 5.18 | 開発した Grafana の Dashboard                                               | 71 |

| 5.19 | Grafana $\mathcal{O}$ Query                                            | 71 |

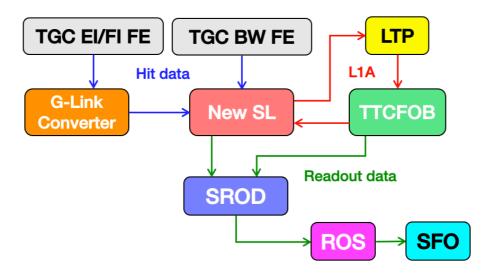

| 6.1  | Run 3 における Level-1 ミューオンエンドキャップトリガーのデータ読み出しシステムの全体像                    | 75 |

| 6.2  | SROD ソフトウェアの構造                                                         | 76 |

| 6.3  | OKS における SROD ソフトウェアのアプリケーションの定義                                       | 79 |

| 6.4  | SROD Segment の構造                                                       | 80 |

| 6.5  | SROD アプリケーションの動作モードの定義                                                 | 81 |

| 6.6  | EventBuilder の性能改善のために変更した処理                                           | 83 |

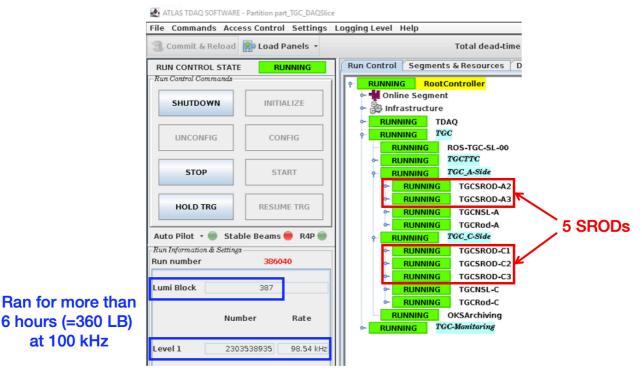

| 6.7  | トリガーデータ読み出しパスの $100~\mathrm{kHz}$ における長期安定性試験 $\dots$                  | 84 |

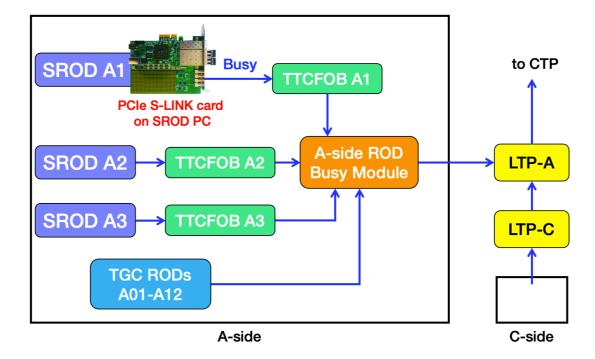

| 6.8  | SROD に関係する busy 線の配線                                                   | 85 |

| 6.9  | SROD に関係する busy 線の配線の確認試験                                              | 86 |

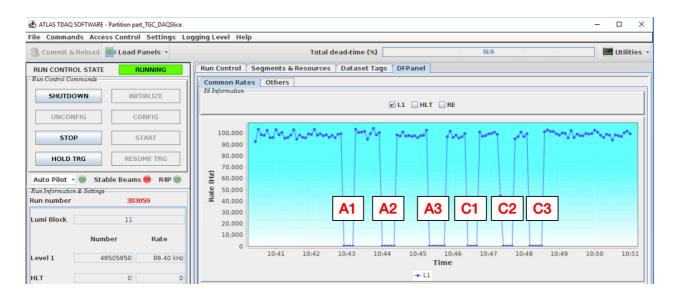

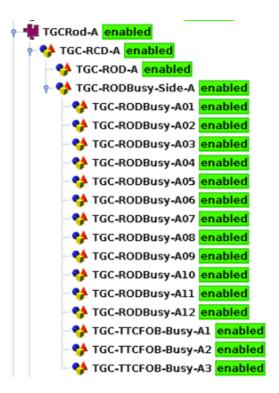

| 6.10 | Segments & Resources における ROD Busy Module の busy 信号入力の定義               | 87 |

| 6.11 | SROD ソフトウェアの busy 信号の出力処理の動作検証試験における Run Control Panel                 | 88 |

| 6.12 | TTC Fanout Board から SROD に送られるデータのフォーマット                               | 89 |

| 6.13 | New SL から SROD に送られるデータのフォーマット                                         | 90 |

| Pad word の実装方法                                                                                    | 96                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|---------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pad word 処理の動作検証試験の結果                                                                             | 97                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

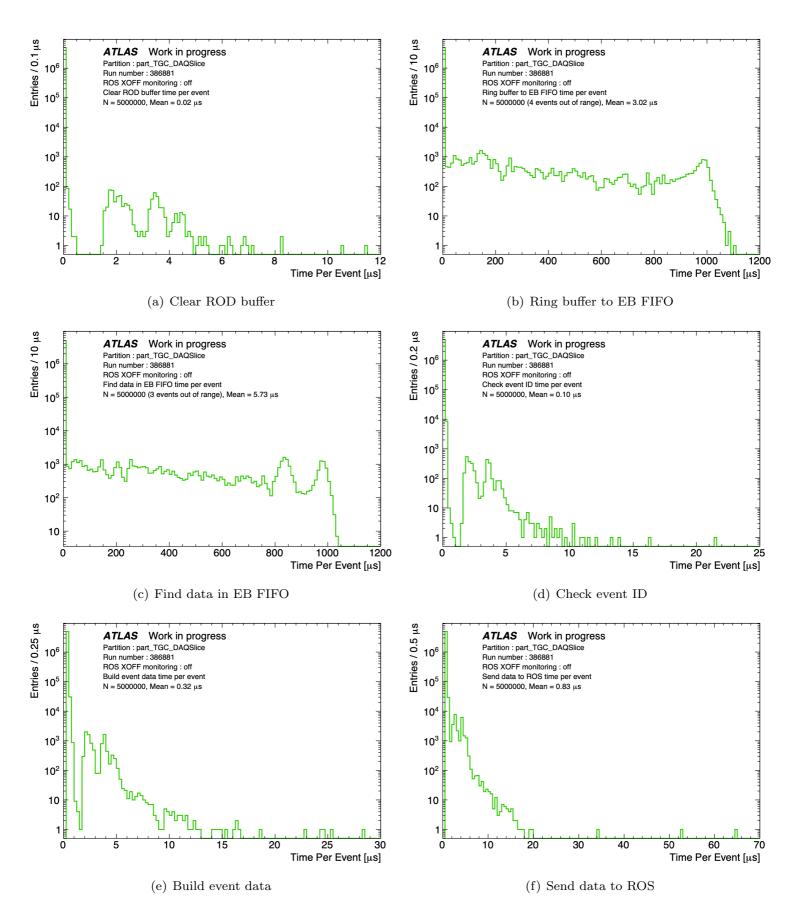

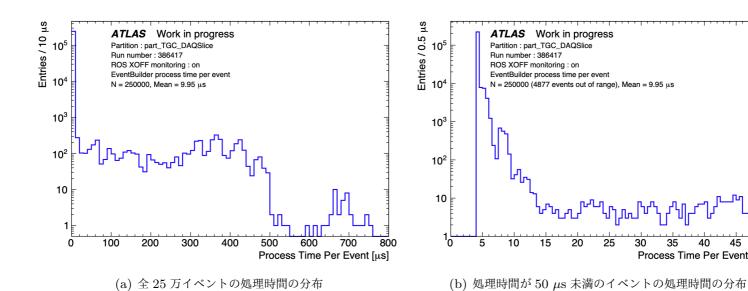

| L1A レート 100 kHz における EventBuilder の全体処理時間の分布 (XOFF なし)                                            | 99                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

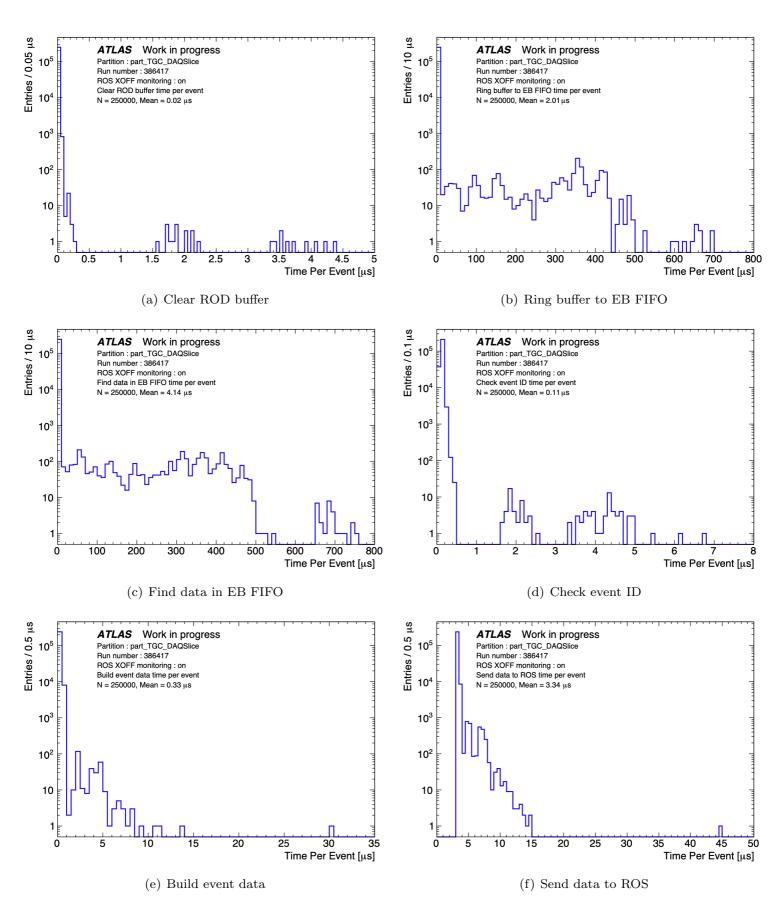

| L1A レート 100 kHz における EventBuilder の各処理の所要時間の分布 (XOFF なし)                                          | 100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

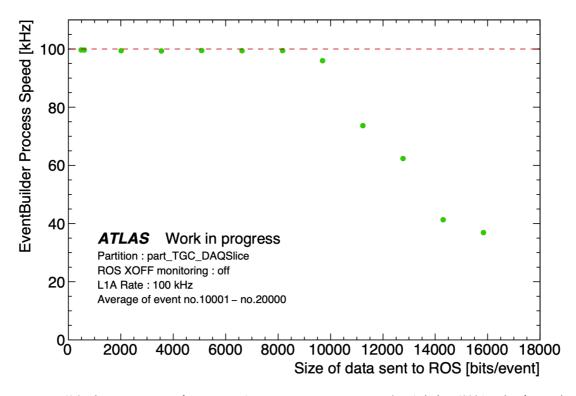

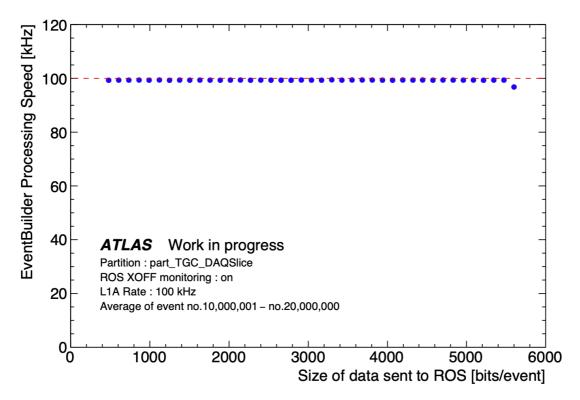

| ROS に送信するイベントデータの大きさと EventBuilder の処理速度の関係 (XOFF なし)                                             | 102                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

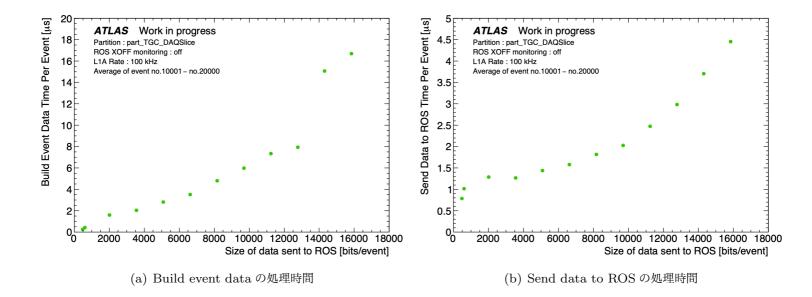

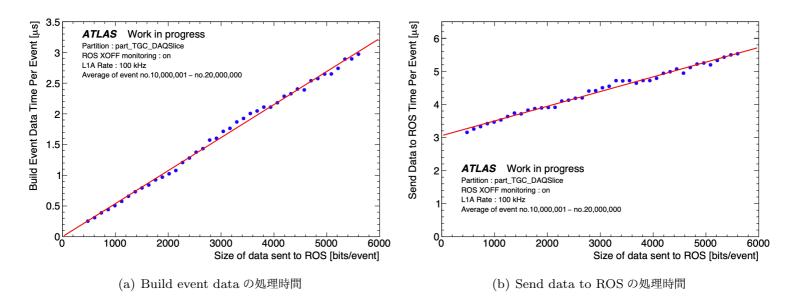

| ${ m ROS}$ に送信するイベントデータの大きさの増加に伴う処理時間の増加 $({ m XOFF}$ なし $)$                                      | 103                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

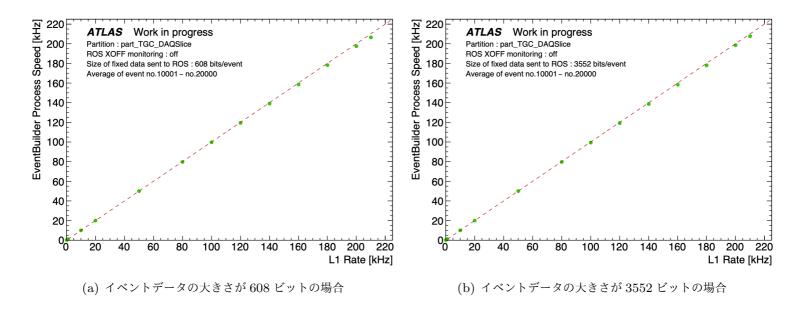

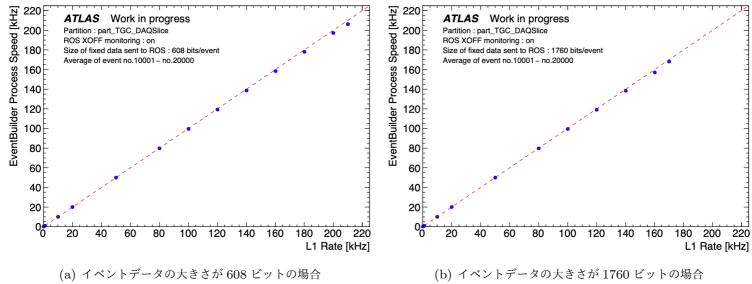

| EventBuilder の処理速度と L1A レートの関係 (XOFF なし)                                                          | 103                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| L1A レート 100 kHz における EventBuilder の全体処理時間の分布 (XOFF あり)                                            | 104                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| L1A レート 100 kHz における EventBuilder の各処理の所要時間の分布 (XOFF あり)                                          | 105                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| ROS に送信するイベントデータの大きさと EventBuilder の処理速度の関係 (XOFF あり)                                             | 107                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| ${ m ROS}$ に送信するイベントデータの大きさの増加に伴う処理時間の増加 $({ m XOFF}$ あり $)$                                      | 107                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| EventBuilder の処理速度と L1A レートの関係 (XOFF あり)                                                          | 109                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

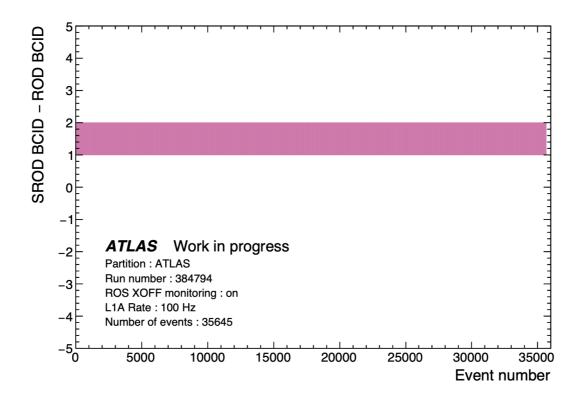

| SROD と TGC ROD の読み出しデータの BCID の差分                                                                 | 110                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

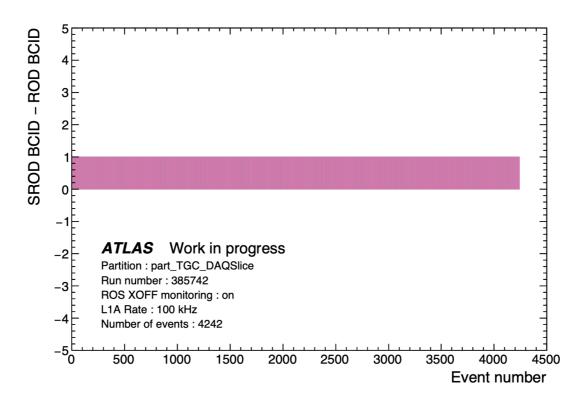

| BCR Delay 調節後の SROD と TGC ROD の読み出しデータの BCID の差分                                                  | 111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| TGC のテストパルスを用いた検証試験のセットアップの模式図。                                                                   | 112                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| TGC のテストパルスを用いた検証試験において SFO に記録されたトリガーデータ                                                         | 112                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

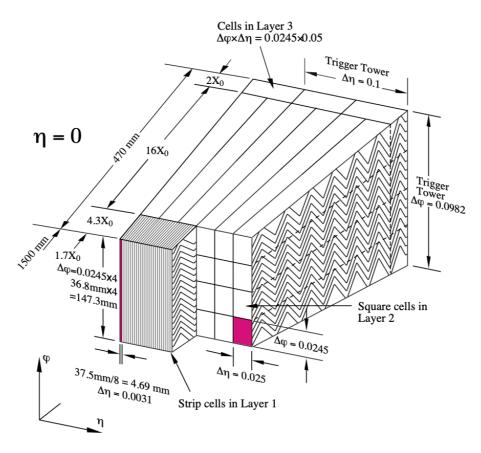

| バレル電磁カロリメータの構造                                                                                    | 125                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

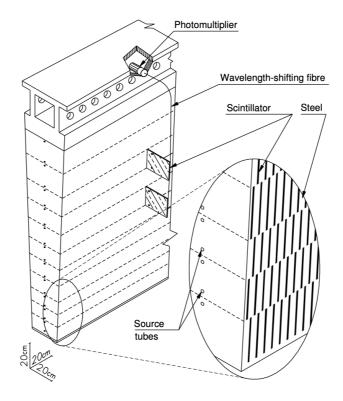

| Tile Calorimeter のモジュールの構造                                                                        | 126                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

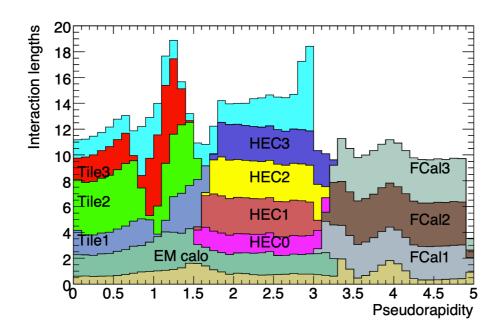

| ハドロンカロリメータ層の interaction length                                                                   | 127                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

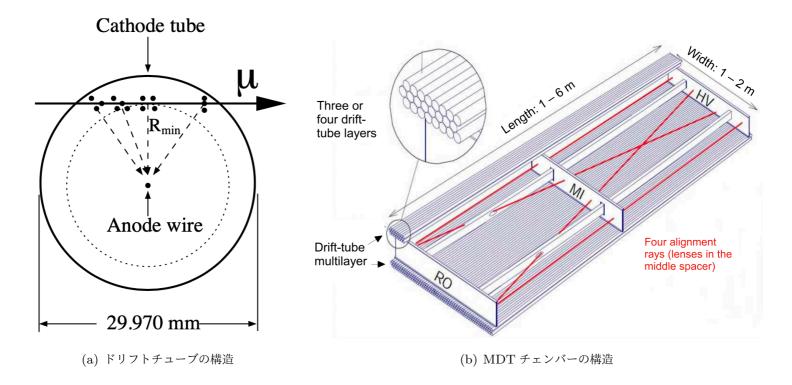

| MDT のチューブとチェンバーの構造                                                                                | 128                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

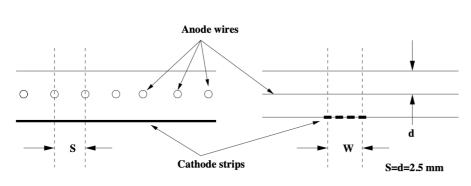

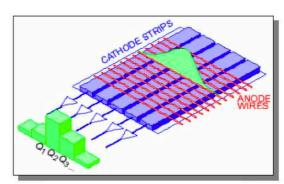

| CSC のアノードワイヤーとカソードストリップ                                                                           | 129                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

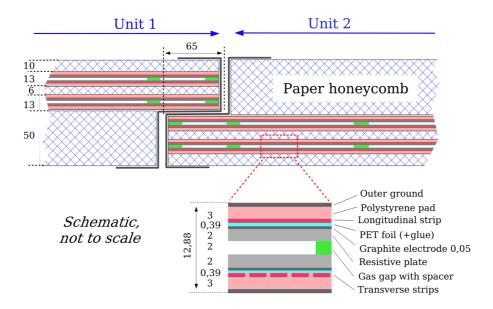

| RPC のチェンバーの断面図                                                                                    | 130                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| OKS データベースのファイル構造                                                                                 | 133                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| DAQSlice Partition の Segments & Resources の全体像                                                    | 136                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| TGC-A および TGC-C Segment の構造                                                                       | 137                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| A-side の ROD クレートと CCI クレートを制御するための Segment の構造                                                   | 138                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| TGC Sector の ResourceSet の構造                                                                      | 139                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| TGCTTC Segment の構造                                                                                | 140                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| New SL のオンラインソフトウェアでの TTC Restart の実装                                                             | 142                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| I <sup>2</sup> C の通信手順                                                                            | 142                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| New SL が受信する TGC BW のトラックデータのフォーマット                                                               | 145                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| エンドキャップ New SL が受信する TGC EI/FI のトラックデータのフォーマット                                                    | 145                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| エンドキャップおよびフォワード $\operatorname{New} \operatorname{SL}$ が受信する $\operatorname{NSW}$ のトラックデータのフォーマット | 146                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| エンドキャップ New SL が受信する RPC BIS78 のトラックデータのフォーマット                                                    | 146                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

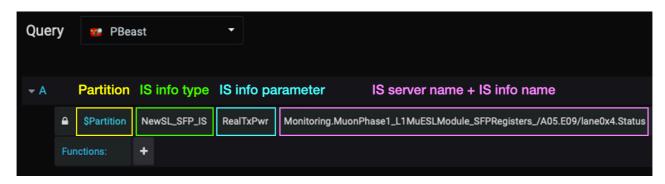

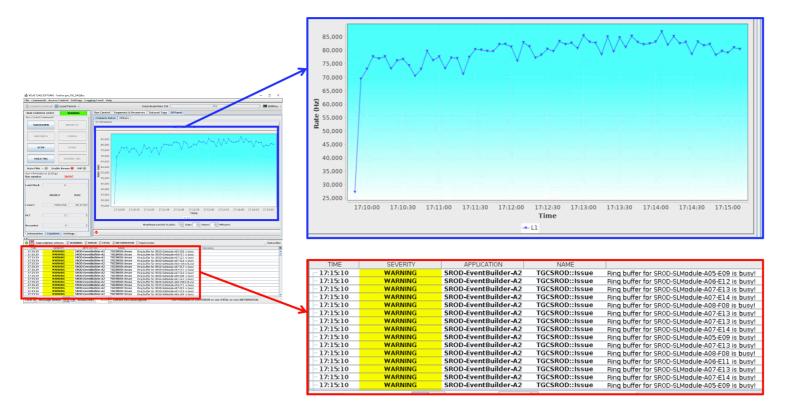

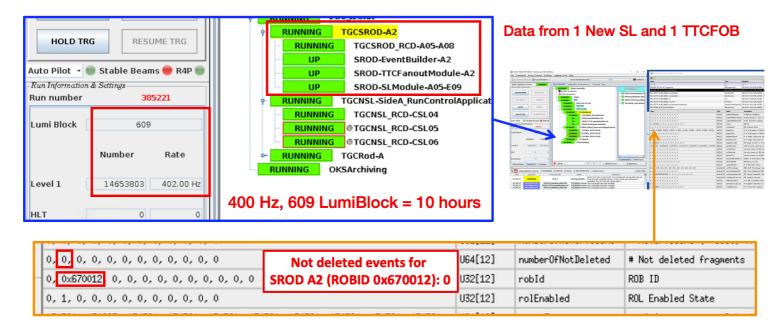

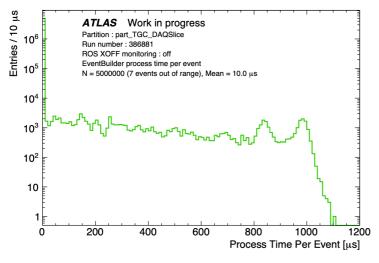

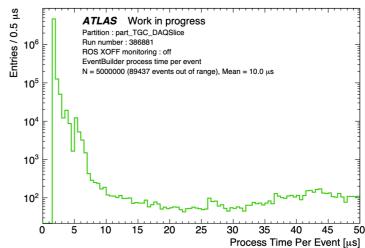

| エンドキャップ New SL が受信する Tile Calorimeter のトラックデータのフォーマット                                             | 146                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |