### 修士学位論文

# LHC-ATLAS 実験 RUN3 のレベル 1 ミューオントリガーに おける読み出しモジュールの開発および評価

東京大学大学院理学系研究科物理学専攻 素粒子物理国際研究センター 坂本研究室 渡邊直樹

2016年2月3日

#### 要約

本研究はスイスの欧州原子核研究機構 CERN で行われている LHC-ATLAS 実験で使われるミューオン検出器のデータ読み出し部分を開発し、その性能を評価したものである。新たに開発されたプロトタイプの読み出しは、高速シリアル通信 GTX と TCP 通信の SiTCP を搭載し、読み出し回路は Field Proframmable Gate Arrays (FPGA) を用いてデザインする。新たに開発したプロトタイプが問題なく動作し、特に GTX 通信は  $1.6\sim10.24$  Gbps でエラー率< $1.0\times10^{-12}$  で機能し、FPGA および SiTCP も要求通りに機能することを確かめる。

#### Key words

CERN, LHC, ATLAS, Thin Gap Chamber, New Small Wheel, Sector Logic, GTX, SiTCP, Xilinx

## 目次

| 1.   | 序章                      | 4  |

|------|-------------------------|----|

| 2.   | LHC 概要                  | 6  |

| 2.1. | LHC で行われている 4 つの実験      | 10 |

| 2.2. | ヒッグス粒子発見におけるミューオン検出の意義  | 13 |

| 3.   | ATLAS 検出器               | 16 |

| 3.1. | ATLAS 座標系               | 16 |

| 3.2. | 内部飛跡検出器                 | 17 |

| 3.3. | カロリメータ                  | 18 |

| 3.4. | ミューオンスペクトロメータ           | 19 |

| 3.5. | マグネット                   | 23 |

| 3.6. | トリガーとデータ収集              | 23 |

| 4.   | TGC                     | 27 |

| 4.1. | TGC の動作原理               | 27 |

| 4.2. | TGC の分類                 | 28 |

| 4.3. | TGC の配置                 | 29 |

| 4.4. | TGC のセクター               | 30 |

| 4.5. | トリガー方法                  | 32 |

| 4.6. | トリガーエレクトロニクス            | 35 |

| 5.   | アップグレード                 | 44 |

| 5.1. | フェイクミューオン               | 44 |

| 5.2. | LHC アップグレード計画           | 49 |

| 5.3. | ATLAS アップグレード計画         | 51 |

| 5.4. | New Small Wheel 概要      | 52 |

| 6.   | 新 Sector Logic 設計       | 55 |

| 6.1. | 9                       |    |

| 6.2. | Sector Logic ボード        | 57 |

| 6.3. | Sector Logic への入力       | 57 |

| 6.4. | コインシデンス                 | 58 |

| 6.5. | 読み出し                    | 59 |

| 7.   | 現行 Sector Logic の変更点    |    |

| 7.1. | New Small Wheel からの追加入力 | 60 |

| 7.2. | 新 Sector Logic 読み出し方式   | 61 |

| 7.3. | 新 Sector Logic プロトタイプ   | 67 |

| 8.   | 新 Sector Logic 評価       | 75 |

| 8.1. | 新 Sector Logic - IO ポート試験             | 75 |

|------|---------------------------------------|----|

| 8.2. | 新 Sector Logic - GTX から SiTCP までの貫徹試験 | 89 |

| 9.   | まとめ                                   | 94 |

| 10.  | 引用文献                                  | 95 |

### 1. 序章

スイスのジュネーブに欧州原子核機能 (CERN) [1] と呼ばれる素粒子物理の実験施設がある. CERN では大型ハドロン衝突型加速器 (LHC) [2] を用いた陽子-陽子衝突実験を行っている. LHC で行われる実験の中の一つに ATLAS 実験 [3]と呼ばれるものがある. ATLAS 実験は未知の物理現象の開拓, 超対称性理論の検証やヒッグス粒子の詳細探索を目的としている.

LHC で使われる実験装置は段階的にアップグレードする計画がある. LHC 始業後から 現在までの実験で浮き彫りになった問題点の解決や, 実験により消耗した器具の交換など がアップグレードの主たる理由であり, 重心系エネルギーやルミノシティも向上していく 予定である. 本研究は ATLAS 実験で使われるミューオン検出器のアップグレードに向けた開発焦点をあてている.

LHC 実験で生成される実験データは莫大で全てを処理することが困難なので、物理研究として興味深いデータのみ選び出す必要がある。この作業をトリガーと呼ぶ。そして、ミューオン検出器を構成するものの中に Sector Logic と呼ばれるハードウェアがある。Sector Logic はミューオンの横運動量を算出し、このトリガー処理を行う。2019 年頃、LHC は実験を休止し (Long Shutdown 2)、二度目のアップグレード作業が行われる予定である。その際に Sector Logic もアップグレードする予定である。

本論文は、ATLAS 実験で用いられる Sector Logic に新たに採用される新技術について行われた検証を報告する. 現在用いられているミューオン検出器は問題を抱えており、高運動量ミューオンではない粒子をそれだと誤認してトリガーを発行してしまう. アップグレードに伴い重心系エネルギーやルミノシティが上がると、トリガーがより過度に発行される. そこで、そのようなフェイクのミューオンを削減するために New Small Wheel (NSW)と呼ばれる検出器を新たに導入する予定である. New Small Wheel からの信号は Sector Logic で受ける. 本研究では新たな Sector Logic のプロトタイプを作成し、新 Sector Logic に入ったデータが期待通りに読み出せるか検証する. この新 Sector Logic は、現行の Sector Logic と次の 3 点で異なる. 1. 新 Sector Logic が Xilinx 社の高速シリアル通信 GTX [4]を備えることで NSW と通信できるようにしたこと. 2. データ処理を全て Field Programmable Gate Arrays (FPGA)に書き込まれたプログラムによって行われるよう変更したこと. 3. Sector Logic から読み出されたデータを PC で確認するために SiTCP [5]と呼ばれる Transmission Control Protocol (TCP) 通信を採用したこと.

本論文の構成は、まず本章に続く第2章でLHC について、第3章でATLAS 検出器について、第4章でミューオンを検出する円盤型の検出器 Thin Gap Chamber (TGC) について解説する。第5章では新 Sector Logic に要求される性能について説明し、第6章で新 Sector Logic プロトタイプの開発について述べる。そして、第7章では新 Sector Logic の開発につ

いて述べ, 第8章で検証結果を報告する. 第9章で本論文をまとめる.

## 2.LHC 概要

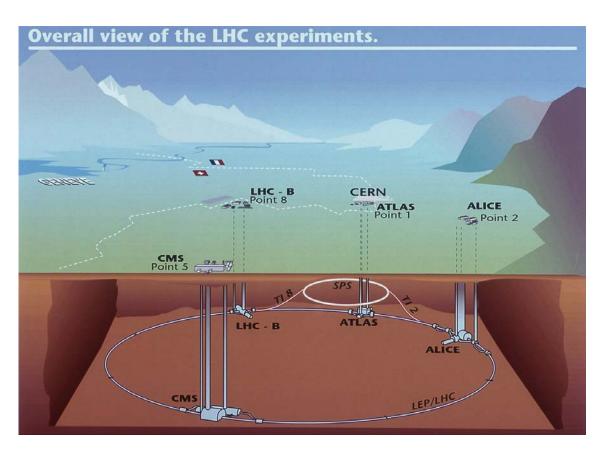

LHC (Large Hadron Collider) は高エネルギー実験を目的として欧州原子核研究機構 (CERN, organization Européenne pour la Recherche Nucléaire) によってフランスとスイスを跨いで地下 100m に設置された円形の大型ハドロン衝突型加速器のことである. この全周はしばしば山手線の全周 34.5km に比較される. Figure 1 に概略図を示す.

Figure 1: LHC 概略図 [6]

1989 年から 2000 年に使われていた CERN が建設した前身の LEP (Large Electron-Positron collider) は陽電子-電子衝突型シンクロトロンで重心系エネルギーは 100GeV であった. LEP のトンネルを再利用して開発された LHC は陽子-陽子衝突型加速器で,重心系エネルギーは 14TeV を想定している. 2008 年の稼働時の LHC は重心系エネルギー900GeV だったが,段階 的に上げていき,2010,2011 年に 7TeV,2012 年に 8TeV,そして 2013 年 2 月から 2015 年 4 月 の約 2 年間の改良工事を経た後では 8TeV から 13TeV へとエネルギーを上げて運転を再開

した. 他のパラメータについては Table 1 の通りである.

| リング周長     | 26.7 km  | 偏向磁場      | 8.33 T                                  |

|-----------|----------|-----------|-----------------------------------------|

| ビームエネルギー  | 7 TeV    | 瞬間ルミノシティ  | $10^{34}  \text{cm}^{-2} \text{s}^{-1}$ |

| バンチ間隔     | 24.95 ns | バンチあたり陽子数 | $1.15 \times 10^{11}$                   |

| バンチ ID 総数 | 3564     | 使用バンチ数    | 2808                                    |

Table 1: LHC デザインパラメータ ([7],[8])

なぜ LHC がこのように巨大なリングを持つに至ったのか. それは, 粒子をより加速するためである. 荷電粒子の軌道が曲がると, 荷電粒子はシンクロトロン放射光と呼ばれる光を放出し, エネルギーを消耗する. 例えば, 一個の電子による円形軌道放射の場合, その瞬間的な全放射パワーP(全周波数, 全立体角で積分)は

$$P = \frac{2}{3} \frac{e^2 c}{4 \pi \varepsilon_0} \frac{\beta^4 \gamma^4}{\rho^2}$$

と表される. ただし、e: 素電荷;c: 光速; $\epsilon$ 0: 真空の誘電率; $\rho$ : 曲率半径; $\beta$ : 光速で規格化した速度; $\gamma$ : 静止エネルギーで規格化した電子のエネルギー. このとき、電子エネルギーの4乗に比例し、半径の2乗に反比例する. LHC は半径を大きくすることで放射光を減らすことを試みた. そもそも、円形ではなく直線加速させて放射光の発生をなくそうという考えもある. 実際、国際線形加速器 International Linear Collider の建設計画が日本の北上山地を候補として進められている.

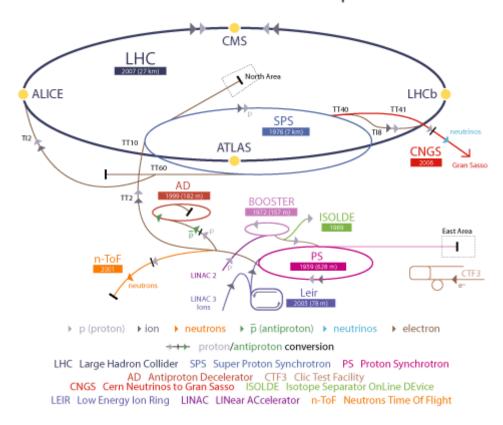

LHC でどのように陽子が加速されるのか説明する. LHC に陽子ビームが入る前に、陽子ビームは既に段階的に加速されている. 陽子イオン源から出た陽子イオンは線形加速器である Linac2 で加速された後、PS Booster と呼ばれるシンクロトロンで 1.4 GeV で加速され、その後順に PS (Proton Synchrotron)、SPS (Super Proton Synchrotron)を経て 450 GeV までエネルギーを上げたあと、LHC に入射される. これを Figure 2 に示す.

### **CERN Accelerator Complex**

Figure 2: Accelerator Complex [9]

陽子は一個一個を単独に加速するのではなく、 $1.15 \times 10^{11}$  protons/bunch とするバンチを単位として LHC リングをまわる (重心系エネルギー7 TeV のデータ). バンチとバンチの間は 7.5m の間隔があいている (衝突頻度  $25 \text{ns} \times \text{光速} \sim 7.5 \text{m}$ ). 簡単な試算で一周には約 27 km/7.5 m = 約 3600 バンチ入ることがわかるが、実際には陽子のない空のバンチもあり、陽子のある 2808 バンチと空の 756 バンチ (合わせて 3564 バンチ)が存在することになる. さらに、バッチという単位もあり、72 バンチで 1 バッチとなる。下の式では 3564 個あるバンチ中どの 2808 個のバンチに陽子が格納されるのか、バッチ (下式 b)と空 (empty、下式 e) で示す。

$\{[(72b + 8e) * 2 + 30e] + [(72b + 8e) * 3 + 30e] + [(72b + 8e) * 4 + 31e]\} + \{[(72b + 8e) * 3 + 30e] + [(72b + 8e) * 3 + 30e] + [(72b + 8e) * 4 + 31e]\} * 3 + \{80e\} = 3564 [10]$

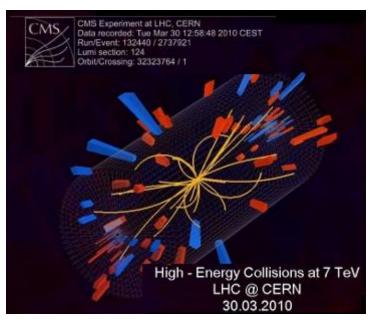

例えば、最初の項は、72 陽子バンチ、8 個の空のバンチが続いたあと、30 個の空のバンチが続くことを示す. これで1つのバッチである. これら陽子が Figure 3 に示すように衝突し、得られた粒子を検出器でとらえ、世界各地にあるコンピュータで解析する.

陽子がどのようにして衝突に減っていくかを見ていく. LHC の陽子-陽子衝突の断面積は 7 TeV で 110 mbarns (mili barns) (1 barn =  $10^{-28}$  m²)である. 一秒間あたりの総反応数は, ルミノシティと断面積の積をとり.

$$10^{34} \times (110 \times 10^{-3} \times 10^{-24}) \sim 10^9$$

collisions/second

だとわかる. 陽子バンチは 2808 バンチあるので, 一秒間あたり, 一バンチあたりの衝突すうは

$$10^9 / 2808 \sim 3.6 \cdot 10^5$$

collisions / bunch and second

である. また, LHC 入射時 $1.15 \times 10^{11}$  protons/bunch であることから, 陽子-陽子衝突を陽子 の崩壊とみなすと, その崩壊確率 (崩壊定数)  $\lambda$  は

$$\lambda = 3.6 \cdot 10^5 / 1.15 \cdot 10^{11} \sim 3 \cdot 10^{-6}$$

collisions / proton and second

この値は、ある陽子が向かいからくる陽子と衝突する一秒あたりの確率を示している. したがって、陽子数について次の微分方程式を得る.

$$\frac{\mathrm{d}N}{\mathrm{d}t} = -\lambda N$$

ゆえに,

$$N(t) = N(0)e^{-\lambda t}$$

陽子の平均寿命  $\tau$  は、N(t)/N(0) = 1/e として

$$\tau = 1/\lambda = 3 \cdot 10^5 \,\mathrm{s} \,(\sim 80 \,\mathrm{h})$$

となる. 以上から, 衝突点の陽子-陽子衝突のみ考えると, 陽子寿命は 80 時間以上あることがわかる. 他にも, 陽子とガスの反応や陽子のクーロン散乱などを考慮すると, 陽子寿命は 10 時間ほどになる [11].

Figure 3: 陽子-陽子衝突の様子

### 2.1. LHC で行われている 4 つの実験

LHC で行われている 4 つの実験を説明する.

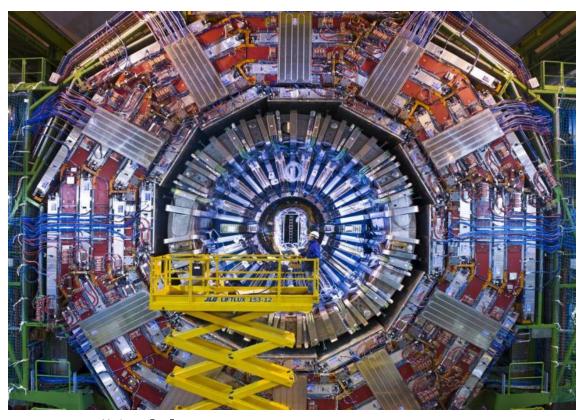

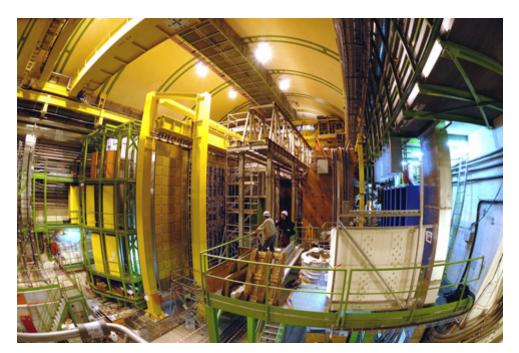

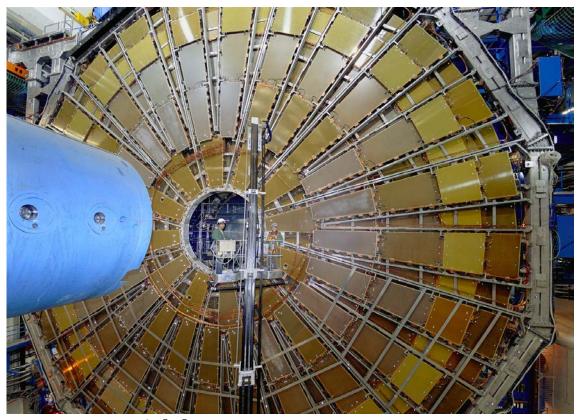

ATLAS (A Troidal LHC ApparatuS)は LHC 実験の中で最も大きな汎用検出器を用いている. Higgs 粒子の詳細探索だけでなく, 超対称性粒子の発見や高エネルギー領域の未知の物理現象の開拓なども目的としている. 大きさは, 長さ 44 m, 直径 25 m, 質量は 7,000 t である. ソレノイド磁石だけでなく, その名に冠している通り, 強大な超伝導トロイド磁石を持つ. 内部飛跡検出器を格納する前の検出器の写真を Figure 4 に示す.

CMS (Compact Muon Solenoid) は ATLAS と LHC リングの反対側に設置された汎用の大型検出器である. ATLAS と互いに成果を競い合っており、ヒッグス粒子の詳細探索、超対称性理論の検証、未知の物理の発見が狙いである。検出器は長さ 31 m, 直径 15 m, 質量は12,500 t であり、円筒形である. ATLAS 検出器より小さいが、質量は CMS の方が大きい. CMS 検出器を Figure 5 に示す.

ALICE (A Large Ion Collider Experiment) は重イオン ( $^{208}$ Pb $^{82+}$ ) 同士を衝突させる. 検出器の大きさは長さ  $26\,m$ , 直径  $16\,m$ , 質量  $10,000\,t$  である. 宇宙初期の状況である Quark Gluon Plasma (QGP) を再現するのが目的である. クォークは単体では取り出せない (クォークの閉じ込め) が, 温度にして  $1012\,K$  以上の高温状態ではクォークとグルーオンからなるガス状態が現れると予想されている. これが QGP である. ALICE 検出器を Figure  $6\,\kappa$ 元す.

LHCb (Large Hadron Collider beauty) では, b クォークの物理に注目し, B メソンにおける CP 対称性の破れを測定し, 物質と反物質の性質の違いを調べることを目的としている. 長

さ 21 m, 高さ 10 m, 幅 13 m, 質量 5600 t の検出器を用いている. LHCb 検出器の写真を Figure 7 に示す.

これら 4 つの実験を Table 2 にまとめた. LHC リングは上空から見て 8 等分に分けて番号が振られており, それぞれ Point1 から Point8 と呼ばれる.

| 実験名        | サイト    | 実験                |  |

|------------|--------|-------------------|--|

| ATLAS      | Point1 | 大型汎用検出器による実験      |  |

| ALICE      | Point2 | 重イオン検出器による QGP 検証 |  |

| CMS Point5 |        | 大型汎用検出器による実験      |  |

| LHCb       | Point8 | Bメソンにおける対称性の破れの検証 |  |

Table 2: LHC で行われている実験

Figure 4: ATLAS 検出器 (中央に立つ人と比較するとその大きさがわかる) [12]

Figure 5: CMS 検出器 [13]

Figure 6: ALICE 検出器 [14]

Figure 7: LHCb 検出器 [15]

## 2.2. ヒッグス粒子発見におけるミューオ

## ン検出の意義

ATLAS 実験と CMS 実験は 2013 年にヒッグス粒子を発見した. それをうけ 2013 年のノーベル物理学賞は英エディンバラ大学名誉教授ピーター・ヒッグス氏とベルギー・ブリュッセル自由大名誉教授フランソワ・アングレール氏に贈られた. 1964 年に彼らが理論を提唱したためだ.

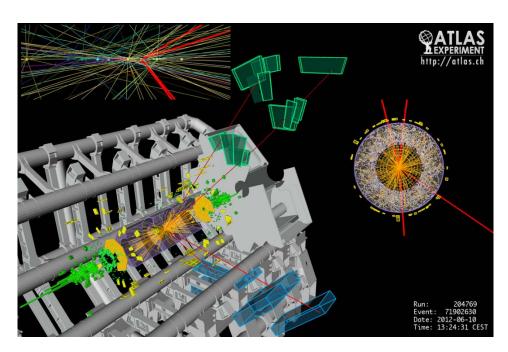

Figure 8: ヒッグス粒子が 2 個の Z ボソンに崩壊し, 最終的にいずれのボソンも 4 個のミューオン (赤線) に崩壊する様子 [16]

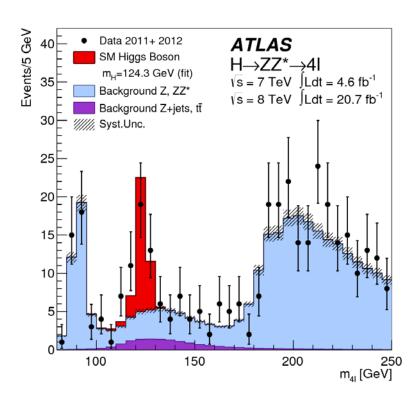

LHC で発見されたヒッグス粒子は、2個の光子に崩壊するもの、4個のレプトンに崩壊するもの、2個のWボソンに崩壊するもの、2個のタウ粒子に崩壊するものが現在のところ確認されている [16]. 即ち、

$H \rightarrow \gamma \gamma$

$H \ \rightarrow \ ZZ^* \rightarrow 41$

$H \rightarrow WW^* \rightarrow 1 \nu 1 \nu + 0/1 \text{ jets}$

$H \, \to \, \tau\tau$

の4モードである。ここで、ZZ\*のイベントがLHCで検出される様子を Figure 8 に示した。Z ボソンはミューオンまたは電子に崩壊するので、それらレプトンの観測はヒッグス粒子の観測において重要でなる。2011-2012 年のLHC-ATLAS 実験の 4 レプトン観測のデータを用いて、ヒッグス粒子が発見されたときのプロットを Figure 9 に示す。本研究ではミューオン検出器のアップグレードについて述べるが、ミューオン観測の意義はこのようにして明白なものである。

Figure 9: ヒッグス粒子が 2 個の Z 粒子に崩壊し、それぞれの Z 粒子がミューオンに崩壊したときのプロット [16]

### 3.ATLAS 検出器

本章では、CERN で行われている 4 つの実験のうちの一つ ATLAS 実験の検出器について、詳しく見ていく.

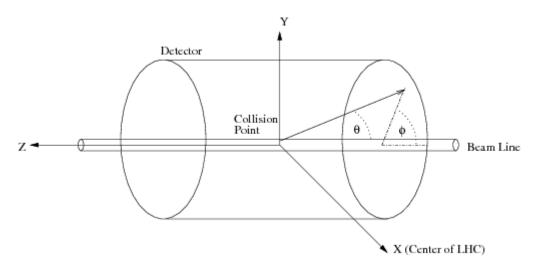

## 3.1. ATLAS 座標系

以降の説明で必要になるので、まずは ATLAS で用いられる座標系について順に 3 つ説明する.

ATLAS では、通常の直交 xyz 座標系に加えて、擬ラピディティ (pseud-rapidity)  $\eta$  を用いた座標系がよく使われる。まず、xyz 座標系は、LHC リング中心向きを x、鉛直上向きに y軸、ビーム方向を z 軸としている。 z 軸の正負は、ジュネーブ側 (A side) を z>0、ジュラ側 (A side) を A となるように決めている。次に、A を用いた座標系で、A 方向を方位角方向、ビームパイプ方向を A 軸としている。ATLAS 検出器の各パーツの位置関係を表現するのによく使われる。最後に、擬ラピディティ A を用いた座標系だが、A は衝突点からの天頂角 A を用いて次の式で定義される。

$$\eta = -\ln\left(\tan\frac{\theta}{2}\right)$$

擬ラピディティはエネルギーE, 運動量 P の粒子のラピディティ  $y=\frac{1}{2}\ln\frac{E+P\cos\theta}{E-P\cos\theta}$  の 高エネルギー極限と一致し,  $\eta$  および  $\theta$  で表された生成粒子の分布は一様になることから, 粒子のヒット位置を示すときによく使用される.

#### Figure 10: ATLAS 座標系 [17]

また、 $1.05<|\eta|<1.92$ をエンドキャップ、 $1.92<|\eta|<2.70$ をフォワード呼んでいる.

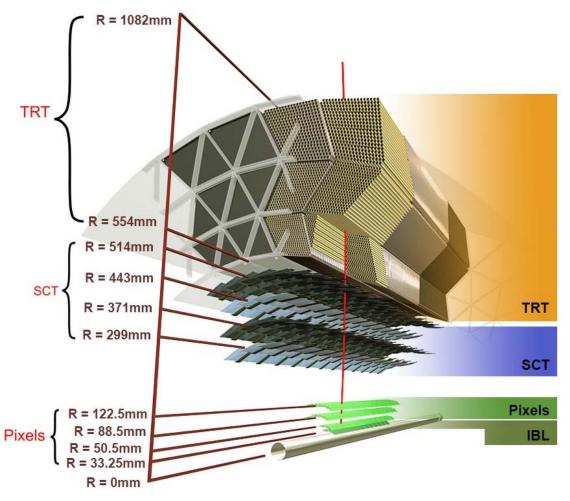

### 3.2. 内部飛跡検出器

内部飛跡検出器 (Inner Detector, ID) は ATLAS 検出器の最内部に設置されている検出器で, 飛跡の再構成を行う. ATLAS の内部飛跡検出器は内層のシリコン飛跡検出器と外層の遷移放射飛跡検出器で構成される. Figure 11 にバレル部の内部飛跡検出器の概要を示す.

内部飛跡検出器の内層には、分解能に優れるシリコン飛跡検出器を配置している.これには、ピクセル飛跡検出器とシリコンストリップ飛跡検出器がある.

ピクセル飛跡検出器 (Pixel) は、シリコンピクセルを用いた高分解能の位置検出器であり、衝突点に最も近い位置に設置されている。 バレル部は三層からなる。第一相を特に B-layer と呼び、2 次バーテックス (B など寿命の比較的長い粒子が崩壊した点) の同定に役立つ。 位置分解能は r- $\phi$ 方向で  $10\,\mu$  m、z 方向で  $115\,\mu$  m である。

シリコンストリップ飛跡検出器 (Semi Conductor Tracker, SCT) は, Pixel 同様に分解能が優れた位置検出器である. ソレノイド磁場によりローレンツ力を受けて曲げられた荷電粒子の飛跡をとらえることで横運動量  $(p_T)$  の測定を可能にする. 位置分解能は r-  $\phi$  方向が 17  $\mu$  m, z 方向が 580  $\mu$  m である.

遷移放射飛跡検出器 (Transition Radiation Tracker, TRT) は、 $|\eta|$  < 2.0の領域で、遷移放射 (荷電粒子が誘電粒子の異なる 2 つの物質の境界で出す放射)を用いて、SCT の外部領域のトラッキングを行う。内部飛跡検出器すべてをシリコンで作るのはコストがかかるので遷移放射検出器が採用されている。ストローチューブ検出器と、遷移放射物質のポリプロピレンファイバーが互いに重なりあった構造をしており、ポリプロピレンからの X 線をストローチューブが捉える。

Figure 11: 内部飛跡検出器 (バレル部) [18]

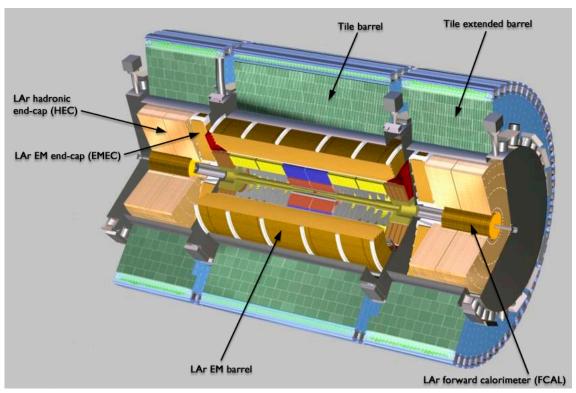

## 3.3. カロリメータ

カロリメータは内部飛跡検出器の外側にあり、粒子のエネルギーや放出角度を測定する検出器である. 二種類ある. 陽子や電子を検出する電磁カロリメータと、ジェットを検出するハドロンカロリメータである. ATLAS 検出器には 4 つのカロリメータが使われている (Figure 12). 以下でそれぞれについて見ていく.

Figure 12: カロリメータ [19]

- Lar 電磁カロリメータ (EM)は、液体アルゴン (Liquid Argon, LAr) を用いた電磁カロリメータである。内部飛跡検出器のすぐ外側に配置されている。カバー領域は、 $|\eta| < 1.48$  (バレル部)および  $1.38 < |\eta| < 3.2$  (エンドキャップ部)である。 $|\phi|$  方向の検出効率を上げるため吸収体アコーディオン状に折り畳まれている。

- バレル部カロリメータ (Tile) は、 $|\eta|$  < 1.7 のバレル部をカバーするハドロンカロリメータで、厚さ 3mm の鉄と厚さ 5mm のタイル上のシンチレータを交互に重ねあわせた構造となっている.

- エンドキャップ部 Lar ハドロンカロリメータ (Hadronic End-cap Calorimeter, HEC) は、 $1.5 < |\eta| < 3.2$  のエンドキャップ部をカバーするハドロンカロリメータである.銅の吸収体と Lar が用いられている

- フォワード部 LAr カロリメータ (Forward Calorimeter, Fcal) は,  $3.1 < |\eta| < 4.9$  のフォワード領域をカバーするカロリメータである. FCal はビーム軸方向に三層のカロリメータから構成される. 第一層 (FCal1) は銅の吸収体と LAr, の電磁カロリメータが採用され, 第二層 (FCal2) および第三層 (FCal3) はタングステンの吸収体と Lar のハドロンカロリメータが採用されている.

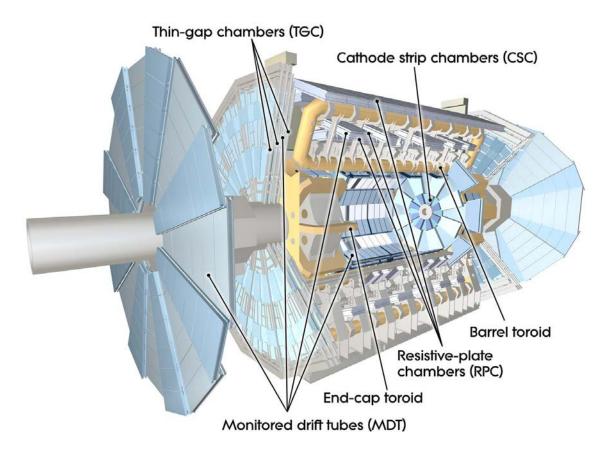

### 3.4. ミューオンスペクトロメータ

ミューオンスペクトロメータは ATLAS 検出器の最外部に配置されている一連の検出器

群のことである. Figure 13 にミューオンスペクトロメータの模式図を示す. 具体的には, Precision Chamber と Trigger Chamber から成る. Precision Chamber は磁場と垂直な r-z 方向の位置を  $50\mu$  m 程度の精度で測定することが求められる. 一方, Trigger Chamber は 25ns 以内の応答,  $p_T$  の測定によるトリガー, 数  $mm\sim1$ cm 精度の第二座標 ( $\phi$ ) の測定が求められる. 以下に, それぞれの Chamber の内訳を見る.

Figure 13: ミューオンスペクトロメータ [20]

#### **Precision Chamber**

高精度位置測定のために Monitored Drift Tube (MDT) を用いる. ただし, フォワード領域2.1 <  $|\eta|$  < 2.7は高カウントレートに耐えられないため, Cathod Strip Chamber (CSC) を用いる.

- MDT: バレル部, エンドキャップ部のうち $|\eta|$  < 2.7 の領域で, ミューオンの位置を精度  $100\,\mu$  m 以下で測定する. 分解能は  $50\,\mu$  m, カウントレートは < 150 Hz/cm² である. カソード径 30mm, アノード径  $50\,\mu$  m であるドリフトチューブで構成されている. スペーサーフレームの両側に, ドリフトチューブ  $3\sim4$  本を層状に並べたものが一つのチェンバーになる.

- CSC: ワイヤエンドキャップ MDT は 3 層あるが, そのうち最も衝突点に近い層 (Inner Station, 後述) では  $|\eta| > 2.0$  の領域でカウントレートが上限の 150  $Hz/cm^2$

を超える. そのため、 $2.0 < |\eta| < 2.7$  部分には MDT の代わりに CSC が使われている. CSC は、カウントレート上限  $1 \text{kHz/cm}^2$ 、ワイヤ間隔 2.54 mm、ストリップ読み出し間隔 5.08 mm の MWPC (Multi-Wire Proportional Chamber) であり、位置分解能は  $60 \, \mu \, \text{m}$  である. MWPC は比例計数管の一種で、ここではカソードとアノードワイヤを垂直なストリップ状にすることで二次元読み出しを可能にしている.

#### **Trigger Chamber**

ミューオントリガーはバレル部を Resistive Plate Chambe (RPC), エンドキャップ部を Thin Gap Chamber (TGC) でカバーする. TGC については 4. TGC (P.27) にて詳述した.

RPC: 高抵抗版を電極として用いるガス検出器である. ATLAS では互いに直行するストリップを用いて, z- φ 二次元情報を取得できる. バレル部のトリガーに用いる.

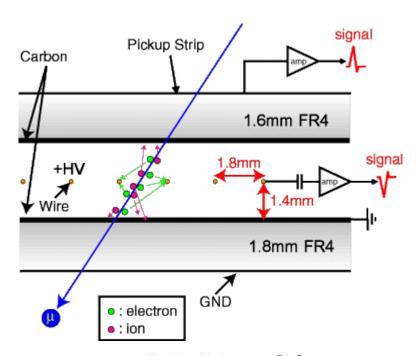

TGC:  $1 < |\eta| < 2.4$  のイベントトリガーを主な目的としている. R 方向はアノードワイヤから,  $\varphi$  方向はカソードストリップから情報を受け取ることで, R- $\phi$  方向の読み出しを実現している. 陽子-陽子衝突の間隔 25ns よりも早く読み出される必要があるが, ワイヤ間隔 1.8mm よりワイヤ・ストリップ間隔 1.4mm の方を短くするといった工夫によって可能となっている.

ミューオンスペクトロメータの各検出器の性能は Table 3 を参照されたい.

| 検出器 | 検出領域 ( η )           | 表面積 (m²) | チャンネル数 (10 <sup>4</sup> ) | 分解能       |

|-----|----------------------|----------|---------------------------|-----------|

| MDT | $ \eta $ < 2.7       | 5500     | 37                        | $80\mu$ m |

| CSC | $2.0 <  \eta  < 2.7$ | 27       | 6.7                       | $60\mu$ m |

| RPC | $ \eta  < 1.1$       | 3650     | 35.5                      | ~1mm      |

| TGC | $1.0 <  \eta  < 2.4$ | 2900     | 44                        | ~1cm      |

Table 3: ミューオンスペクトロメータの性能 [21]

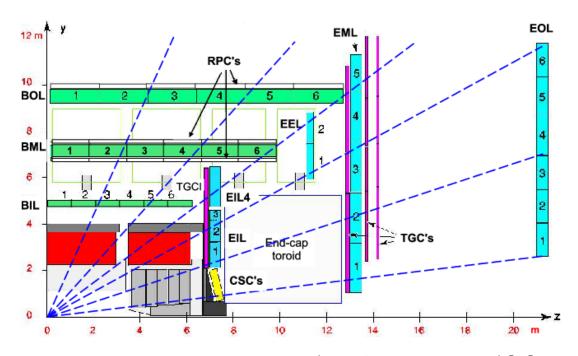

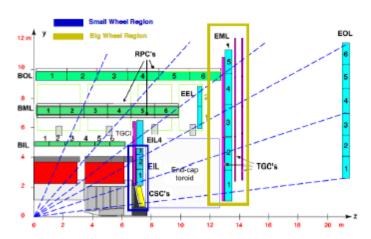

#### 配置

ミューオンスペクトロメータの配置を見ていく. 配置場所によって, いくつかのチェンバーからなるステーションという単位をとっている. バレル部には 3 つのシリンダー状のステーション (Inner, Middle, Outer), エンドキャップ部では 4 つディスク上のステーション (I, M, O, Extra) がある. これらは, バレルを表す B や, エンドキャップを表す E を付して, たとえば BI のように, 呼ばれる. また, EM ステーションを Big Wheel (BW), EI ステーションを Small Wheel (SW) と呼ぶことがある. Table 4 にてステーションごとに検出領域, トラッキング, トリガー, 第二座標測定についてまとめている.

| ステーション | 検出領域                 | トラッキング | トリガー | 第二座標測定 |

|--------|----------------------|--------|------|--------|

| BI     | $ \eta  < 1.0$       | MDT    |      |        |

| BM     | $ \eta  < 1.0$       | MDT    | RPC  | RPC    |

| ВО     | $ \eta  < 1.0$       | MDT    | RPC  | RPC    |

| EI     | $1.0 <  \eta  < 2.0$ | MDT    |      | TGC    |

|        | $2.0 <  \eta  < 2.7$ | CSC    |      | CSC    |

| EM     | $1.0 <  \eta  < 2.4$ | MDT    | TGC  | TGC    |

|        | $2.4 <  \eta  < 2.7$ | MDT    |      | TGC    |

| EO     | $1.4 <  \eta  < 2.7$ | MDT    |      |        |

| EE     | $1.0 <  \eta  < 1.4$ | MDT    |      |        |

Table 4: ミューオンスペクトロメータの各ステーション構成 [21]

なお、各ステーションは $\varphi$ 方向に 16 分割されている。これは8 回対称のトロイド磁石に合わせているためだ。8 つはバレルとロイド磁石の間に位置し Large sector と呼ばれ、残りの8 つはバレルとロイドの直近に位置し Small sector と呼ばれる。Large sector と Small sector では $|\eta|$  の値が若干異なるが Table 4 に載せたのは Large sector のものである。 Figure 14 にラージセクターの図を載せている。

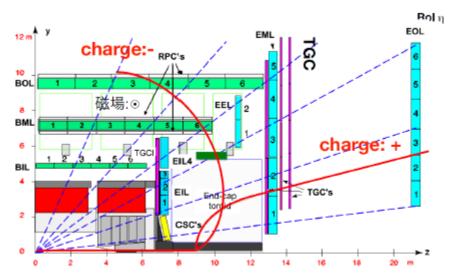

Figure 14: ミューオンスペクトロメータの断面図(z>0,上半分のラージセクター) [22]

### 3.5. マグネット

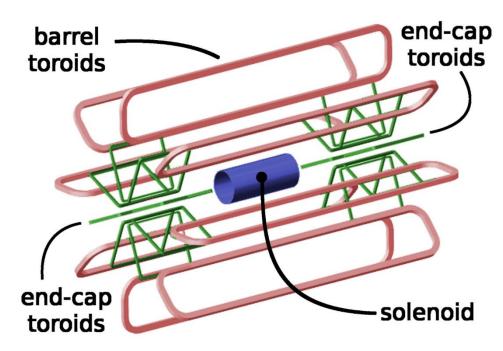

ATLAS 検出器には二種類のマグネットが備え付けられている. 超伝導ソレノイド磁石と ATLAS の名前にも冠されている超伝導トロイド磁石だ. Figure 15 にその二種類を示す.

Figure 15: ATLAS Magnet [23]

超伝導ソレノイド磁石は、ID の外側にあり、z方向約 2T の磁場を発生させる荷電粒子は $\phi$ 方向に曲げられ、ID で  $p_T$  が観測される.

バレル部超伝導トロイド磁石は、カロリメータの外側に設置されている. 長さは 25m であり、8 つの超伝導コイルにより  $\phi$  方向に約 0.5T の磁場を発生する. 荷電粒子は $\eta$  方向に曲げられ、RPC で  $p_{\rm T}$  が観測される.

エンドキャップ部超伝導トロイド磁石は、最も内側のエンドキャップミューオン検出器の外側に設置される。長さは 5m であり、各コイルはバレル部のものと 22.5 度ずつずれて配置されている。 $\phi$  方向に約 1T の磁場を発生させ、荷電粒子を曲げ、TGC で  $p_T$  を観測する。

## 3.6. トリガーとデータ収集

LHC の陽子バンチ同士は 40.079 MHz の頻度で衝突する. 計算すると,24.95 ns ごとに衝突が起きていることになる. 一度の衝突で, 平均して数十個の陽子同士の衝突イベントが

発生する. バンチのペアの衝突ごとに数 MB のデータ量が保存されるため, 毎秒数 10~数 100TB の情報量が生まれる. この莫大なデータ量を全て記憶装置に保存するのは困難であるし, ほとんどのデータは QCD (Quantum Chromodynamics) によって引き起こされており重要ではない. たとえば, 14TeV では Higgs 粒子は 10 億回に 1 回程度しか生成されない. そのため, 膨大なバックグランドを排除して興味深いデータのみを効率的に選び出す技術が要求される. この選別をトリガーと呼ぶ. 本節では, トリガーシステムと, データ収集システム (Data Acquisition, DAQ) について説明していく. ちなみに, トリガーとデータ収集システムは合わせて TDAQ (Trigger and DAQ) とも呼ばれる.

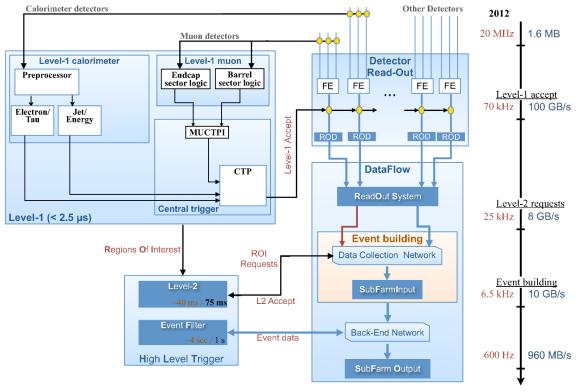

ATLAS では  $40\,\mathrm{MHz}$  のデータを最終的に  $200\,\mathrm{Hz}$  まで落とす。トリガーは三段階用意され,トリガーごとに異なる研究チームが開発を担当している。  $3\,\mathrm{QK}$ のトリガーは,川上から順にレベル  $1\,\mathrm{トリガー}$ ,レベル  $2\,\mathrm{トリガー}$ ,イベントフィルターと呼ばれる。レベル  $1\,\mathrm{トリガー}$  では, $2.5\,\mu\,\mathrm{s}$  という厳しいレイテンシ条件からハードウェアによって処理される。レベル  $2\,\mathrm{トリガー}$ 及びイベントフィルターはソフトウェアによって処理される。この違いから,レベル  $2\,\mathrm{トリガー}$ とイベントフィルターはまとめて High Level Trigger (HLT) と呼ばれることがある。

Figure 16: Trigger and Data Acquisition [24]

#### レベル1トリガー

レベル 1 トリガーはミューオンの  $p_T$  情報,電子,光子,ジェットなどの情報を用いてトリガーをかけ、レートを 75-100 kHz に落とす。 $p_T$  情報は TGC, RPG から提供され、エネルギー情報は電磁カロリメータ、ハドロンカロリメータから精度を荒いものが提供される。これら検出器と、情報を総合してトリガー判定を下す Muon Trigger to CTP Interface (MuCTPI) や Central Trigger Processor (CTP)、及びトリガーを分配する Timing Trigger and Control distribution system (TTC) で L1 トリガーシステムは構成される。CTP までの経路によって、ミューオン検出器の情報を用いてレベル 1 ミューオントリガーと、カロリメータの情報を用いたレベル 1 カロリメータ (L1 Calo) の 2 つが存在する。

ミューオン検出器では、衝突点から飛来したミューオントラックの  $p_T$  情報を測定する. TGC, RPC にはあらかじめ閾値が設定されており、 $p_T$  を 6 段階に振り分ける. ある閾値を超えた  $p_T$  を検出すると、そのミューオンのトラック情報が MuCTPI に送られる. そこで各々の  $p_T$  閾値で検出されたトラック数によって、レベル 1 判定が下される.

カロリメータは、 $\tau$ レプトンの崩壊によって発生したハドロン、電子、光子、ジェットなどの情報から得られた横方向エネルギー ( $E_T$ ) と、イベントの横方向消失エネルギー ( $E_T^{miss}$ ) を測定する.  $E_T$ に対しては、それぞれのイベントに対して 4-8 段階の閾値が決められており、 $E_T^{miss}$ に対しては 8 段階の閾値が決められている。この予め決められた閾値を超えたイベントのトリガー情報は CTP に送られる。レベル 1 カロリメータのレベル 1 判定は、各閾値で検出されたイベント数にもとづき判定される。

衝突から L1 トリガー判定を出すまで、つまり L1A 信号を出すまでには固定時間の 2.5  $\mu$ s かかる約束になっている。そのため、データは  $2.5\,\mu$ s の間は保持していないといけない。 L1 Buffer というメモリでリングバッファを構築し、そこでトリガーの発行の有無を待つ。 このメモリは少なくとも  $2.5\,\mu$ s/25ns = 100 段必要である。実際には、L1A が発行されてから、 L1 Buffer で処理するまでに L1A が回線を通過するだけの有限時間がかかるので、100 段では足りない。

CTP は現象に合わせて MU (muon), EM (electromagnetic)や J (jet) といったトリガーメニューを用意している. いずれかの基準を満たすと Level 1 Accept (L1A) 信号を発行する. L1 Buffer にあるデータは, TTC から L1A を受信すると次の処理に進むが, L1A を受け取らなかった場合は L1 Buffer を出ると同時に捨てられる.

データは、デランダマイザでトリガー発行のばらつきを抑えられ、Read Out Drive (ROD) に送られる. ROD までを各検出器システムが担当しており、ROD はデータを ATLAS 共通のフォーマットに変換し、Read Out System (ROS) へと送る. この ROS というものは、複数の Read Out Buffer (ROB) で構成されており、L2 の処理の間データを保持する. この流れとは別に、Region of Interest (RoI) 情報が L2 に渡される. RoI は L1 トリガーで得られた粒子の存在領域を  $\eta$  と  $\phi$ で表したものであり、L2 で使用される.

#### レベル 2 トリガー

レベル2トリガーでは、イベントレートを数3.5 kHz程度に落とす。カロリメータ、MDT からの情報と内部飛跡検出器からの完全な位置情報、レベル 1 の情報を使って計算された Region of Interest (RoI) と呼ばれる領域のみの情報を用いてトリガー判定を行う。レベル 2 では 1 イベントに対し約数 10 ms のレイテンシ制約がある。

#### イベントフィルター

イベントフィルターでは、RoI に限定せず全てのデータを用いてトリガー判断を下す. トリガー判断は複数の EF Sub Farm から構成された EF Farm によって並列処理される. EF Sub Farm は SFI からデータを受け取り、最大 4s かけてトリガーを発行する. イベントレートは 200~Hz まで落とされる. レイテンシ制約は 1 イベントあたり 1s である.

### 4. TGC

レベル1ミューオントリガーはWやZの崩壊により得られる高 $p_T$ を同定するために重要な役割を果たしている。本章では、トリガーのエンドキャップ部分をカバーする TGC の概要、TGC が発行するトリガーの説明、トリガーの回路、トリガーの読み出し機構について詳述する。

### 4.1. TGC の動作原理

TGC は Multi Wire Proportional Chamber (MWPC) の一種であり,直行するアノードワイヤとカソードストリップによって二次元読み出しを行う.ワイヤがR方向,ストリップが $\varphi$ 方向の情報を得る.ワイヤには直径 $50\mu$ mの金メッキタングステンワイヤーが採用され,3.1 kV の電圧が印加されている.ストリップには銅版が使用されている.3.4 ミューオンスペクトロメータ (P.19) で述べた通り,ワイヤ間の間隔は 1.8 mm であるが,ワイヤとストリップ間の間隔は 1.5 mm と短く,バンチ衝突周期の 25 ns 以内の読み出しを可能にしている.Figure 17 に TGC の内部構造を示してある.

Figure 17: TGC 断面図と荷電粒子検出の原理 [25]

TGC 内部には電離ガス CO2 とクエンチャーn-pentane が 55:45 で混合されたガスが充填 されている. ガス中を荷電粒子が通過することで陽イオンと電子が電離する. この電離し た一時電子はチェンバー内の強電場によって電気力線に沿って移動する. そして最近傍のワイヤに近づくと強電場により急激に加速され,電子雪崩を起こす. ワイヤはこの電子雪崩を信号として取り出し,またストリップ側も同時に誘起している電荷を読み出す. 電離の際に生じる紫外線を n-pentane が吸収することで,必要以上の電子雪崩が発生することを抑制している.

### 4.2. TGC の分類

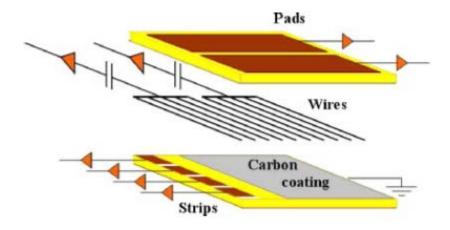

TGC には 2 層の Doublet と 3 層の Triplet の 2 種類がある. Figure 18 に Doublet と Triplet の構造を示す.

Doublet は2つのガスキャップをハニカム構造で支える.2つのワイヤ層と2つのストリップ層から情報を読みだす.

Triplet は 3 つのガスキャップをハニカム構造で支えており, 3 つのワイヤ層と 3 つのうち真ん中を除く 2 層のストリップ層から情報を読みだす.

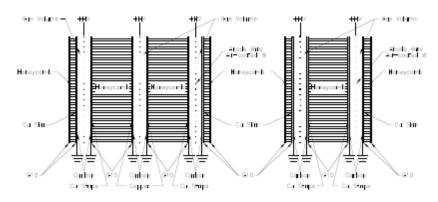

Figure 18: TGC のダブレットとトリプレット [26]

また、一枚のチェンバーは大きさによって T1~T9 にわけられる. T1 と T2 は中心角  $\phi$  方向に  $2\pi/24$  の広がりを持ち、これは T3~T9 それぞれの中心角の 2 倍に当たる. トリプレットの T1、T3、T6、T7 および T8 チェンバーをこの順に動径方向 R の小さい方向から並べて一一ただし T1 は 1 枚、ほかは 2 枚一一、それを  $\phi$  方向に一周させると TGC1 (M1) が得られる. 一枚の TGC1 には T1 が 24 枚、そのほかのチェンバーを 48 枚使われる. 同様にして、T2、T5、T6、T7、T8 および T9 で作ったものが TGC2 (M2)、ダブレットの T2、T5、T6、T7、T8 および T9 で作ったのが TGC3 (M3) である. M1、M2 および M3 は MDT と並んで BW (EM) の主要構成要素である(Figure 19).

Figure 19: Big Wheel の写真 [27]

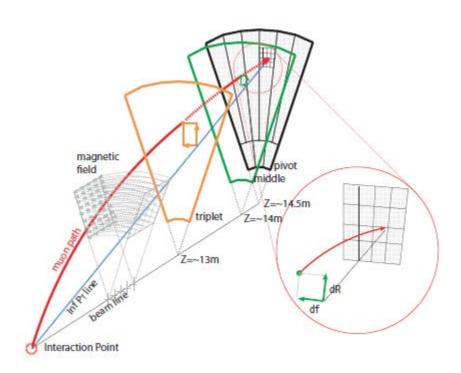

## 4.3. TGC の配置

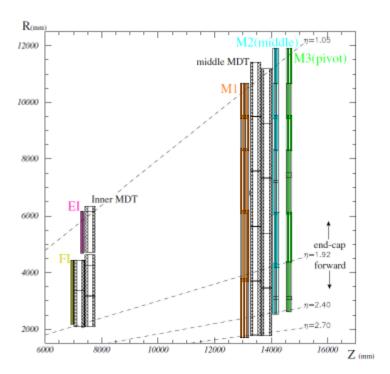

Figure 20 に TGC の配置を示す. BW は 3 つの TGC から成る. BW の衝突点に近い方から, M1 (|z| ~ 13 m), M2 (|z| ~ 14 m)および M3 (|z| ~ 14.5 m) が設置されている. 衝突点から見て, ワイヤ層が 7 層, ストリップ層は 6 層ある. M1 と M2 の 1m ほどの間隙には MDT が設置されている.

Figure 20: TGC の配置図 [28]. BW は 3 つのステーションから, EI/FI は 1 つのステーションから構成される.  $1.05 < \eta < 1.92$  の領域をエンドキャップ,  $\eta < 1.92$  の領域をフォワードと呼ぶ.

T1 と T2 はフォワード部をカバーしている. トリガーや DAQ はエンドキャップとフォワードで分けて処理される. なお, フォワードのうち 2.40  $< |\eta| < 2.70$  の領域は M1 しかカバーしていないので, トリガー情報は生成されず, 位置測定のみが行われる.

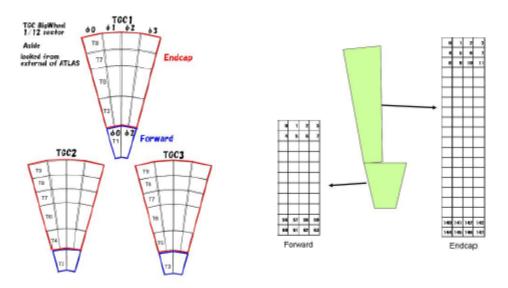

### 4.4. TGC のセクター

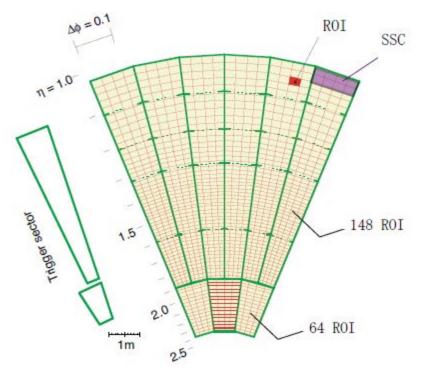

TGC の組み立てやデータ処理はセクターという単位にわけて行われる (Figure 21). さらにセクターの内部では、フォワード部はチェンバー一枚、エンドキャップ部はR方向に連続した 4 枚 (M1) もしくは 5 枚 (M2, M3) の集合をトリガーセクターと呼ぶ. 1 セクターあたりフォワードのトリガーセクター2 つ ( $\phi$ 0,  $\phi$ 2)、エンドキャップのトリガーセクター4つ ( $\phi$ 0- $\phi$ 3) が含まれる.

さらに、小さいサブセクターにわけられ、1 つのサブセクターはワイヤ、ストリップともに 8 チャンネルで構成される。その数は、フォワードでは 16 (R) × 4( $\phi$ ) = 64 サブセクター、エンドキャップでは 37 (R) ×4 ( $\phi$ ) = 148 サブセクターだけある。サブセクターはトリガーをかける単位であり、その一つ一つが TGC の RoI に相当する(Figure 22).

Figure 21: TGC のセクターおよびサブセクター [29] [30]

Figure 22: TGC のトリガー単位模式図 [26]. 赤色部分がトリガー単位の RoI である. A-side, C-side それぞれ 72 セクターに分かれる. さらにエンドキャップは 148 RoI, フォワードは 72 RoI に分かれる. RoI 8 つをまとめて SSC と呼ぶ.

## 4.5. トリガー方法

TGC を用いたトリガーは、トロイド磁場によって曲げられたミューオンの飛跡を測定するものである。その具体的な測定方法を述べた

#### p の算出

まず、 $p_T$  の算出は次のように行われる。陽子-陽子衝突が起こると、W や Z の崩壊にともなってミューオンが生成される。そのミューオンはトロイド磁場によって飛跡を曲げられながら順に BW 内の M1、M2 および M3 にヒットする。M1 のヒット点と M3 のヒット点を結んだ直線は、ミューオンが無限運動量を持ったと仮定したときの飛跡である。この仮定された飛跡と、実際の飛跡を比較することで  $p_T$  は推定される。Figure 23 に概念図を載せた。

Figure 23: TGC-BW によるミューオンの $p_T$ の観測 [31]

トリガーで見つけたいのは  $p_T$  の大きいミューオンの情報だが,  $p_T$  が大きいほど磁場で曲げられにくいので, 飛跡は直線に近づく. なお, 磁場は $\phi$ 方向であるから軌跡は $\phi$ 方向にはずれないはずだが, 実際には磁場は非一様であり, 軌跡は $\phi$ 方向にもずれる.

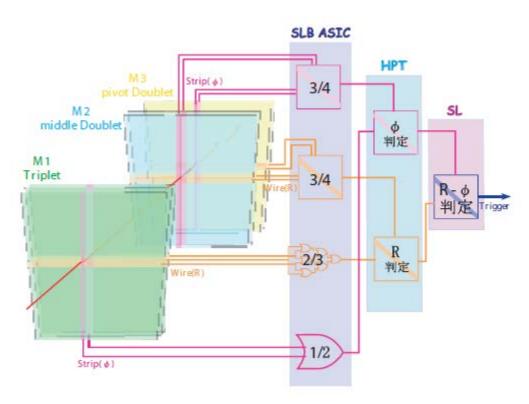

#### 段階的なコインシデンス

さらに詳細を見ていく. コインシデンスとは, 別々に測定されたデータを統合することである. TGC のトリガーでは SLB ASIC が Low- $p_{\rm T}$  コインシデンス, HpT ボードが High- $p_{\rm T}$  コインシデンスを行うことで二段階のコインシデンス処理を行い, バックグラウンドを抑え,  $p_{\rm T}$  の計算に必要な量を揃えていく. そして, Sector Logic がそれらの情報を用いて  $p_{\rm T}$  を算出する. Figure 24 にコインシデンスの様子を示す. SLB ASIC, HpT ボード, Setor Logic といった各エレクトロニクスは 4.6 トリガーエレクトロニクス(P.35)で後述する.

Figure 24: 段階的なコインシデンスをとり最終的に $p_T$ を決定する [31]

#### Low- $p_{\rm T}$ コインシデンス

SLB ASIC によって Low- $p_T$  コインシデンスと呼ばれる処理が行われる. ここでは,ワイヤとストリップ独立に Slave Board ASIC (SLB ASIC) によってコインシデンス処理を行う. 具体的には,M2,M3 ダブレット・ワイヤ,トリプレット・ワイヤの 4 層で 3/4 コインシデンス処理を,ダブレット・ストリップ,トリプレット・ストリップの 4 層を用いて 3/4 コインシデンス処理を行う. また,同様にして M1 の三層のチェンバーを用いて,トリプレット・ワイヤの 2/3 コインシデンス処理を,2 層のストリップチェンバーを用いてトリプレット・ワイヤの 1/2 コインシデンス処理が行われる. ここで,n/m コインシデンスとは,m 層のチェンバー中n 層以上のヒットがあればコインシデンス判定を行うという意味である. この 2 つのダブレットの距離は短く,高い $p_T$ が測れないことから  $Low-p_T$ と呼ばれる.

#### High- $p_{\mathrm{T}}$ コインシデンス

HpT ボード High- $p_T$  コインシデンスと呼ばれる処理が行われる。ここでは、2つの Low- $p_T$  コインシデンス判定の結果を用いて High- $p_T$  (HpT) ボードを用いて行うコインシデンス処理である。ワイヤー信号について、M2 および M3 のデータで行われた 3/4 コインシデンスの結果と、M1 のデータで行われた 2/3 コインシデンスの結果を用いてコインシデンス処理を行う。ストリップ信号について、M2 および M3 のデータで行われた 3/4 コインシデンスの結果と、M1 のデータで行われた 1/2 コインシデンスの結果を用いてコインシデンス処理を行う。これで得られるデータは、M1 と M3 の間の  $\Delta$  の度合いであり、ダブレットとトリプレットは離れているため、高い $p_T$ を計測できる。そのため、High- $p_T$ と呼ばれる。

#### **Sector Logic**

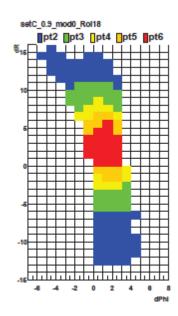

最後のコインシデンスは、ワイヤとストリップの間で、Sector Logic ボードを用いて行われる. Coincidence Window と呼ばれる特殊なマトリックスを用いて最終的な  $p_{\rm T}$  情報が生成される.

Figure 25 は Coincidence Window の一例である. 横軸は  $d \phi$ , 縦軸は dR である. dR の大きさによって $p_T$ の領域が移動していくのがわかる. |dR|が小さいほど $p_T$ は大きい. 各チェンバーの占める  $\eta$  の範囲はずれているので, たとえ無限運動量でも dR=0 にはならない.

RoI の数だけ Coincidence Window が作られる. 磁場の 8 回対称性から全体のうち 1/8 のみ考えれば良い. Figure 22 を見ると RoI の数を計算でき, エンドキャップとフォワード部分を合わせて  $6\times148+3\times64=1,080$  個である. よって, Coincidence Window の数は 1080 個である. Coincidence Window はモンテカルロシミュレーションを用いてトリガー効率を落とさないように最適な分布が適宜採択される.

Table 5: L1 トリガーメニューと  $p_T$  の関係 [32]

| L1 menu | pt1~pt6 | Condition                             |

|---------|---------|---------------------------------------|

| L1_MU0  | pt1     | $p_{\mathrm{T}} < 6$ Gev              |

| L1_MU6  | pt2     | $p_{\mathrm{T}} > 6$ Gev              |

| L1_MU10 | pt3     | 現在使用されていない                            |

| L1_MU11 | pt4     | $p_{\mathrm{T}} > 11 \; \mathrm{Gev}$ |

| L1_MU15 | pt5     | $p_{\mathrm{T}} > 15 \; \mathrm{Gev}$ |

| L1_MU20 | pt6     | $p_{\mathrm{T}} > 20 \; \mathrm{Gev}$ |

Figure 25: Coincidence Window [30]の例. 横軸が  $d\phi$ , 縦軸が dR である.

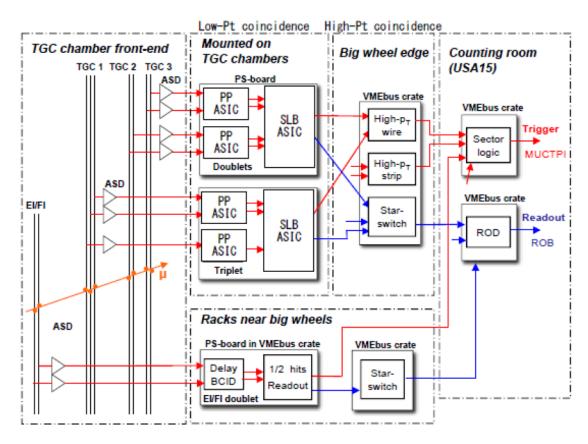

## 4.6. トリガーエレクトロニクス

TGC のエレクトロニクスはトリガー系とリードアウト系に分かれる. 前者はレベル 1 ミューオントリガー判定の処理を行うもので, 前章で触れた. 後者は, TGC 各層のミューオンヒット情報の読み出しを行う. エレクトロニクスの全体像は Figure 26 に示す.

#### トリガー系統 TGC エレクトロニクス

トリガー系統の処理フローは次のように実行される

- 1 TGC のアナログ信号が Amplifier Shaper Discriminator (ASD) ボードに送信される.

- 2 ASD ボードは受信した信号を増幅, 整形, デジタル化した後, LVDS 規格で Pacth Panel (PP) ASIC へ送信する

- 3 PP ASIC は受け取った信号を LHC のクロックに同期し, SLB ASIC へ送る.

- 4 SLB ASIC は PPASIC から信号を受け取ると, Low- $p_{\rm T}$  コインシデンス処理をし, 結果を HPT  $\sim$ 送る.

- 5 HPT は SLB ASIC から信号を受け取ると, High- $p_{\rm T}$  コインシデンス処理を行い, その結果を Sector Logic へ送る.

- 6 Sector Logic は HPT から信号を受け取ると, ワイヤとストリップをコインシデンス処理 し,  $p_{\rm T}$  判定, ROI の決定を行う. その情報を MuCTPI (Muon-to-CTP Interface) に送信し, 最終的なトリガー判定が行われる.

ちなみに、PPASIC と SLB ASIC は共通の PS ボード上に設置される.

Figure 26: TGC エレクトロニクスの全体像 [26]. 赤線はトリガー系統, 青線はリードアウト系統の信号処理を著す.

### リードアウト系 TGC エレクトロニクス

リードアウト系データ処理では、TGC の各層のヒット情報と TGC コインシデンス情報を読みだす。リードアウトは次のような流れで行われる。

- 1 TGC のアナログ信号が ASD ボードへ送られる.

- 2 ASD ボードは受信した信号を増幅,整形,デジタル化した後,LVDS 規格で PP ASIC へ 送信する.

- 3 PP ASIC は受け取った信号を LHC クロックに同期し, SLB ASIC へ送る. ここまでの動作はトリガー系と共通である

- 4 SLB ASIC は受信したデータを L1 Buffer に溜める. L1A 信号を受け取ったデータを L1 Buffer から読み出し, デランダマイザと呼ばれるバッファを介して Star Switch (SSW)へ送信する.

- 5 SSW は 8 つの SLB ASIC からデータを受信し, そのデータを圧縮した後, Read Out Drive (ROD)へ送る.

- 6 ROD は 10 個の SSW からの情報を受信し, フォーマットを変換して ROB へ送る.

さらにリードアウト系では、Sector Logic で行われたコインシデンス結果を Sector Logic 内の SLB ASIC に送る. その後のデータフローは上記のリードアウト 4 番以降に従う.

以下に各エレクトロニクスの説明をした.

### ASD ボード

Amplifier Shaper Discriminator (ASD) ASIC は、TGC のアナログ信号を増幅、整形し、LVDS のデジタル信号を出力する. 増幅は二段階にわけて行われ、第一段回目では 0.8V/pC のプリアンプ、第二段階目には増幅率が 7 のオペアンプが用いられる. ASD ボードは TGC の側面に取り付けられ、1 枚の ASD ボードには 4 つの ASD ASIC が設置され、16 チャンネル持っている.

Figure 27: ASD ボード [31]. 一枚あたり 4 つの ASD ASIC が取り付けられている. アナログ 信号を増幅, 整形し, LVDS 規格のデジタル信号を出力する.

#### **PPASIC**

Patch panel (PP) ASIC は ASD ASIC から受け取った LVDS 信号のタイミング調整や TTC クロックとの同期を行う. 一枚の PP ASIC は 32 チャンネルあり, ASD ボード枚からの信号を処理できる.

TGC では、粒子が検出器まで到達するのにかかる時間 TOF (Time Of Flight) 差や、ケーブル長による違いのため、各チャンネルが受信する信号の受信時刻は揃っていない. PPT ASIC 以降の回路でコインシデンス処理を行うために、PPASIC はタイミングを揃える.

また、PPASIC は信号を TTC から配られる TTC クロックと同期する. これにより、同一のバンチ衝突で得られたデータのエッジは同じ TTC クロックに揃うことになる.

#### **SLB ASIC**

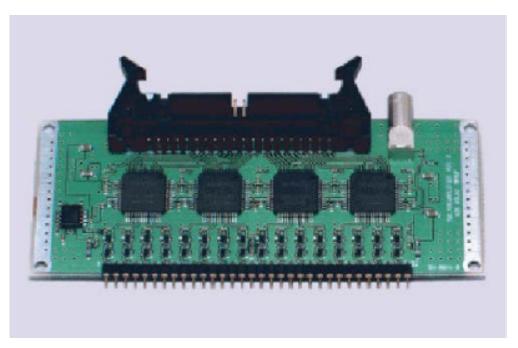

SLB ASIC は多機能であり、トリガー部分とリードアウト部分に分かれる. Figure 28 に模式図を示す.

Figure 28: SLB ASIC 内の信号処理. PP ASIC から受けた信号は SLB ASIC 内部でトリガーと

### リードアウトに分けられ、別々に処理される.

トリガー系データ処理: SLB ASIC は信号のコインシデンス処理を行う. これは 4.54.5 トリガー方法に書いた通りである. M1 からの信号のコインシデンス, M2 と M3 からの信号のコインシデンスはシリアル化され, Cat6 ケーブルにて HPT へ送信される. 一つの ASIC は 4種類のマトリックスを実装しており、レジスタで切り替えることができる.

リードアウト系処理: SLB ASIC は L1 Buffer とデランダマイザを持っている. PPASIC から受けたデータを L1 Buffer に蓄え、L1A を受けたデータを読みだせる. L1 Buffer は 212bit×128words のシフトレジスタであり、最大 128×40.079MHz= $3.2\mu$ s の間データを保持できる. L1 Buffer へ入る 212bit は、データ 160bit、トリガーデータ 40bit、Bunch Counter ID (BCID、いくつ目のバンチか) 12bit より構成される. TTC が発行した L1A を受け取ると、その前後含めて 3 バンチ分、すなわち 212bit×3 = 626bit が L1 Buffer から読み出される. そして、4bit の Level 1 ID (L1ID、いくつ目の L1A 信号か)を各信号に付与するので、データ長は 216bit×3 = 648bit となり、これがデランダマイザに入る。デランダマイザでタイミングを調整した後、3 バンチ分の信号はシリアル変換されて 4bit の LVDS 信号となり、SSW へ入力される. BCID と L1ID は TTC の Bunch Count Reset (BCR)、Event Count Reset (ECT) によって SLB 内でカウントされ、データを同定する役割を果たす.

### HpT ボード

HpT ボードはダブレットとトリプレットのコインシデンスをとるモジュールである. これは HpT SSW Crate (HSC) にある. 1 セクターあたり 1 つの HSC クレートが対応する. 合計で 24 クレートが用意されている. クレートは BW の外縁部に取り付けられており, 放射線のダメージを承けるので, HpT SSW Controller board という特殊なモジュールを VME マスターに使っている. これは G-Link によって地下 100 m に掘られたトンネル USA15 (Undergournd Service Area 15) にある Control Configuration Interface board から操作できる.

HpT ボードにはエンドキャップ・ワイヤ, エンドキャップ・ストリップ, フォワードの 三種類がある. HpT ASIC は一枚でワイヤとストリップどちらでも使え, 外付けのスイッチ で使用を選べる. コインシデンスマトリックスにより, 最大 6 トラックが High- $p_T$ の候補としてあげられ, このうち $p_T$ の高い 2 つがセレクタで選ばれる. 1 トラック以下しか選ばれなかった場合, ダブレットの SLB ASIC で生成された Low- $p_T$ を加えて 2 トラックとする.

エンドキャップ・ワイヤ-HpT ボードはトリガーセクター1 つ分のデータを SLB ASIC から受け取り、4 つの HpT ASIC で処理する. 最大 7 トラックのデータが生成され、G-Link によって Sector Logic へ送られる.

エンドキャップ・ストリップ-HpT ボードはトリガーセクター2 つ分を担当し、1 トリガーセクターあたり 2 つのエンドキャップ・ストリップ-HpT ボードが処理する. 最大 4 トラックのデータが G-Link で Sector Logic へ送られる.

Figure 29: HpT ボード [31]. Doublet と Triplet のコインシデンスをとる.

### ミューオントリガー装置 (Sector Logic)

本研究の中心でもある Sector Logic は HPT ボードからワイヤヒット情報,ストリップヒット情報を受け取り、それらのコインシデンスをとり、FPGA でミューオンの  $p_T$  情報を計算し、トリガー発行を行う・FPGA は Coincidence Window を用いて、予め設定された閾値に従い、 $p_T$  を 6 段階の度数に振り分ける。これは FPGA 内の Look Up Table (LUT) 内に RoI ごとに CW が作成されてあり、入力に ( $\Delta R, \Delta \phi$ ) を入れるだけで LUT は  $p_T$  を算出する。FPGA を書き換えることで LUT を書き換えることができるので、閾値の変更は用意である。トリガーが発行されると、Sector Logic は RoI、 $p_T$ や BCID などの情報を 32bit にし MuCTPI ヘパラレル送信する。PS ボード中の SLB ASIC が出すデータには BCID の情報がないので、BCID の値は Sector Logic 内に与えられているものを使用している。Sector Logic ボード上にある SLB ASIC がトリガー情報や HPT ボードからの入力情報を受け取ると、それらは SSW (Star SWitch) を用いて読み出される。

Figure 30: Sector Logic ボード [33]. HpT から得たワイヤヒット情報, ストリップヒット情報のコインシデンスをとり, 最終的な $p_T$ を算出する.

### **Star Switch**

Star Switch (SSW) は、その名の通りスター型のスイッチで、SLB ASIC から読み出されるデータを収集し、圧縮する。この圧縮によってデータ量が減り、効率よく転送できる。全ての SSW ボードは同一の構成であり、放射線耐性をもつ anti-fuse FPGA をデータ受信用に6つ、送信用に1つ、モジュールコントロールに1つ備えている。1つの FPGA あたり最大4つの SLB ASIC からのデータを受信できる。データの受信、圧縮、送信は次のようなステプで行われる。

- 1. SLB ASIC からシリアライズされた LVDS 信号が届く.

- 2. データ・レシーバーSSWrx でデータを anti-fuse FPGA で受け取り, パラレルデータ に変換する.

- 3. データを圧縮する.

- 4. 圧縮されたデータはデータ送信用の anti-fuse FPGA へ届き, G-Link に変換されてから ROD へ送られる.

ここで行うデータの圧縮はゼロ・サプレスと呼ばれており, 8bit ごとに区切られたデータのうち,0が連続する8bit は捨て,1bit でも1を含む8bit のアドレスとその8bit の情報だけ

を残す. これは、1 を含む 8bit が多い場合には圧縮できず、むしろデータ量が増えてしまうが、ATLASのデータは 0 が多いので、効率的にデータ量を落とせる.

SSW にはダブレット・エンドキャップ、ダブレット・フォワード、トリプレット・エンドキャップ、トリプレット・フォワードの4種類ある。ダブレット・エンドキャップはトリガーセクター1つ、他の3種類はトリガーセクター2つ分をカバーする。8枚の SSW が HSC クレートにおさめられている。Sector Logic 用の SSW は2枚のエンドキャップ-Sector Logic、1枚のフォワード-Sector Logic からのデータを処理するので、1枚で1セクターに当たる。SSW は12セクターでまとめられ、USA15の専用クレートに収められている。

Figure 31: SSW [31]. SLB ASIC のリードアウトより送信されるデータを収集し, 圧縮する役割を担う.

### **ROD**

Read Out Driver (ROD) に TGC から読み出されたデータが集められ、後段の ROB のためにフォーマットを整形する. TTC 信号を受け取るために TTCrq つきのメザニンカードが搭載され、TTC からの信号を受信することができる. SSW から 1 セクター分のデータを受け取ると、そのデータを光信号から電気信号に変換し、パラレルデータにし、既定のフォーマットに変換する. そして、S-Link という光信号の規格で Read Out System (ROS)へ送信する. また、エラーが生じた場合は CTP に busy 信号を送信する. ROD の写真は Figure 32 に示す.

Figure 32: ROD の写真 [34]

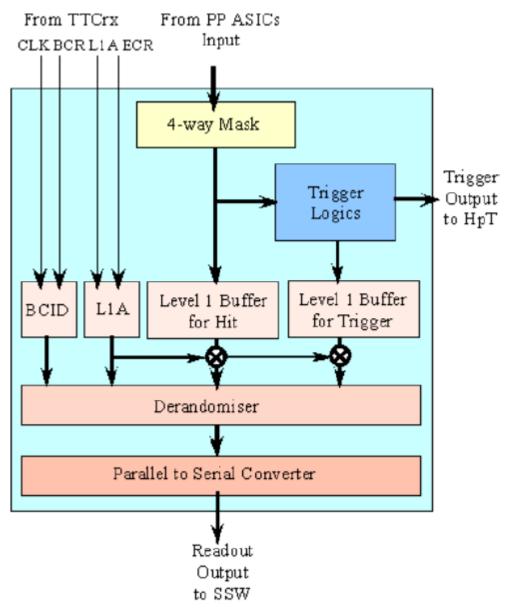

#### TTC

Timing, Trigger and Control distribution (TTC) システムはフロントエンドにある各エレクトロニクスの同期をとる. 具体的には, 各エレクトロニクスに LHC の 40.079MHz クロックや L1A 信号を分配する. TTC は Local Trigger Processor (LTP), TTCvi, TTCvx, ROD busy から構成される. Figure 1Figure 33 に TTC システムの構成を示す.

Figure 33: TTC の構成 [31]

LTP は TTC で扱う信号の全てを TTC システムの外部から受信する. クロックを TTCvx に送信し、他の信号を TTCvi に送信する.

TTCvi はLTP から受信した信号を TTCvx に送信する.

TTCvx は受信したデータを加工した後, オプティカルリンクによってフロントエンドに設置されている TTCrx へ信号を分配する. TTC は vi から TTCvx に送る信号は, A-Channel, B-Channel の二種類がある. 前者は L1A 信号のみうを扱い, 後者はその他の信号を扱う.

ROD busy モジュールは、TTC システム内に属する ROD からの busy 信号を集めた結果を LTP に渡す. LTP は busy 信号を受け取ると、CTP へ busyg 信号を送る.

### 5.アップグレード

### 5.1. フェイクミューオン

### 問題

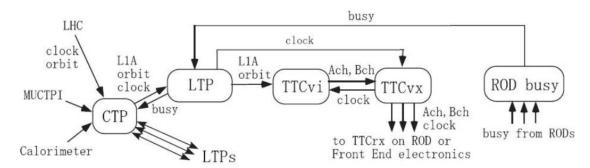

現在のトリガーは大きな問題を抱えている。それは、トリガーが発行されるべきではないタイミングでトリガーが発行されていることだ。Figure 34 に 2012 年の RUN で得られた、ミューオンが飛来したイベント数とトリガー発行数を示す。Figure 34 には 3 つのデータが載っている。一つは L1\_MU11 であり、 $p_{\rm T}>10$  GeV以上だと判断されたミューオンに対するミューオントリガーの数である。二つ目は、RoI matched to reconstructed muon であり、L1\_MU11 のうち、特に衝突点由来( $\Delta R<0.2$ )のミューオン数をオフライン解析で再構成したものである。三つめは、ROI matched to  $p_{\rm T}>10$  GeV であり、これは二つ目のうち、特に $p_{\rm T}>10$  GeV であるものの数を示している。

Figure 34 を見ると、 $1.0 < |\eta| < 2.4$  の範囲でミューオン数の約三倍の数のトリガーが発行されていることがわかる。このトリガーレートとミューオン飛跡レートの差こそ、検出器がミューオンであると誤って判断をくだした粒子、即ちフェイクミューオンの数である。したがって、ミューオンとフェイクミューオンを弁別するシステムが必要である。このフェイクミューオン削減はエンドキャップ部のトリガー改善の課題である。

Figure 34: レベル 1 ミューオントリガー数とオフラインで再構成されたミューオン数の η 分布 [35]. 実際のミューオン飛来数に比べてトリガーが多く発行されている. 2012 年のランの 実験データに基づく.

### 原因

TGC トリガーレートとミューオン飛来レートの差の原因は、主に衝突点由来ではない荷電粒子が原因だと考えられている。荷電粒子が磁場で曲げられ、TGC の BW 三層にヒットする。このヒットが衝突点由来の高 $p_T$ ミューオンだと間違って判断されると、トリガーが発行される。このような荷電粒子には、高エネルギー中性子がビームパイプを叩いて生成される陽子、また陽子ビームがビームパイプ内残留ガスと衝突したり、ビーム同士が弾性衝突して生じる二次粒子(ビームハロー)が考えられる。

Figure 35: フェイクミューオンの模式図. 衝突点以外からの荷電粒子が TGC 三層にヒット レバックグラウンドを残す.

エンドキャップとロイド磁石により約 1T の磁場が $\phi$ 方向にかかる. Figure 35 では衝突 点由来ではない正電荷が磁場によって曲げられ TGC 三層にヒットしている. このようなバックグラウンドのトリガーレートが A-side に多いことから, 正電荷の粒子である陽子がこのバックグラウンドの主な原因になっていると考えられる [36].

### 解決策

LHC アップグレードにともなって重心系エネルギー, ルミノシティは最大 14TeV,  $2\times 10^{34}~{\rm cm}^{-2}{\rm s}^{-1}$  となる. 現状のフェイクミューオンの問題を抱えたままでは, レベル 1 トリガーレートは RUN2 で 34kHz, RUN3 で  $60{\rm kHz}$  まで上昇すると予想されている (Table 6). 他のトリガーとの兼ね合いから, レベル 1 トリガーレートは  $15{\rm kHz}$  までに制限されているので, レベル 1 トリガーレートを抑える対策が必要である. まず考えられる対策に,  $p_T$  閾値を上げ, よりレアなミューオンに対してのみトリガーを発行することが考えられる. しかし, 実際には  $p_T$  を上げてもトリガーレートは十分に下がらず, 高すぎる $p_T$ のみを採取すること自体は物理的に意味をなさない. 仮に $p_T$  閾値を  $20~{\rm GeV}$  から  $40{\rm GeV}$  に上げると, ヒッグス解析に関係のあるレプトンを落とすことに繋がる  $(WH \to l \, \nu \, bb, H \to \tau \, lep \, \tau \, had)$  [37]. こで, この対策はとられず,  $p_T$  の閾値  $20{\rm GeV}$  を維持し, トリガーロジックを改善する方針だ.

|                         | Run-1   | Run-2 | Run-3 |

|-------------------------|---------|-------|-------|

| p <sub>T</sub> 閾値 [GeV] | 15 (20) | 20    | 20    |

| トリガーレート [kHz]           | 9 (6)   | 34    | 60    |

Table 6: Run1 条件下での Run 1, Run 2 および Run 3 のミューオントリガーレート対応表

### 対策

Phase-0 アップグレードを経た Run2 ではそれまで使われなかったインナーステーション(EI/FI)の情報を使い始めた. このため, 衝突点由来ではない荷電粒子のトリガーの削減を行った.

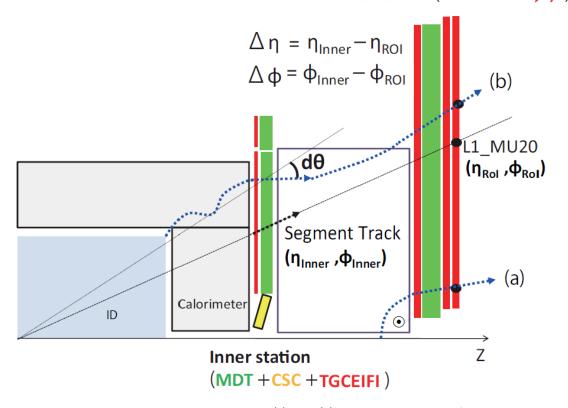

Phase-1 アップグレードを経た Run3 では、新たに New Small Wheel (NSW) を導入する予定である。それまでの情報に加えて、NSW の情報とのコインシデンスをとる。これにより、まず、ビームパイプから発生するフェイクミューオンを完全に取り去ることが期待されている。さらに、ミューオン飛跡の角度と、衝突点と NSW のヒット点を結ぶ角度の差  $d\theta$  を測定し、これによって衝突点由来ではないミューオンを取り除く。これは  $d\theta$  カットと呼ばれる。この $d\theta$  カットだけでなく、NSW のセグメント(精密位置検出器におけるトラック)と TGC-BW の RoI における差( $\Delta\eta$ ,  $\Delta\phi$ )=( $\eta_{RoI}$ - $\eta_{Seg}$ ,  $\phi_{RoI}$ - $\phi_{Seg}$ )のそれぞれの成分が閾値を要求することでフェイクを落とすことも考えられている。これは $\Delta\eta/\phi$  カットと呼ばれている。

### Middle station (MDT+TGC1,2,3)

Figure 36:  $d\theta$  カット,  $\Delta \eta/\phi$  カットをかけて (a) や (b) のフェイクを取り除く.

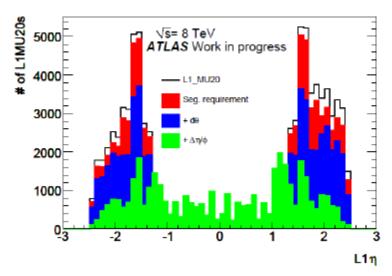

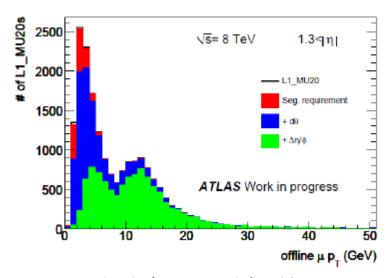

Figure 37 に $d\theta$  カットおよび $\Delta\eta/\phi$  カットをかけた L1\_MU20 の RoI 数 vs  $\eta$  のグラフ, Figure 38 に $d\theta$  カットおよび $\Delta\eta/\phi$  カットをかけた L1\_MU20 の RoI 数 vs  $p_T$  のグラフを載せた. これはシミュレーションではなく RUN1 時のデータを用いて作成された. 黒色の線は L1\_MU20 の全ての  $\eta$  分布を、赤色のヒストグラムはインナーステーションにある MDT の hit でカットをかけたときの  $\eta$  分布を、青色のヒストグラムはさらに $d\theta$  カットをかけた  $\eta$  分布を、そして緑色のヒストグラムはさらに $\Delta\eta/\phi$  カットをかけた  $\eta$  分布を示す. また、Figure 38 中にある 3GeV の山はフェイク信号の、12GeV の山はミューオンのものである.

Figure 37:  $d\theta$  カットおよび  $\Delta\eta/\phi$  カットをかけた L1\_MU20 の RoI vs  $\eta$  [36]

Figure 38:  $d\theta$  カットおよび  $\Delta\eta/\phi$  カットをかけた L1\_MU20 の RoI vs  $p_T$  [36]

また、それぞれのカットに対するリダクションファクターと検出効率を Table 7 に示す.

|                  | 全 L1_MU20 の<br>リダクションファクター |                   | $p_{\mathrm{T}} > 20 \mathrm{GeV}$ Ø |                   |

|------------------|----------------------------|-------------------|--------------------------------------|-------------------|

|                  |                            |                   | ミューオン検出効率                            |                   |

| Cut/Region       | $ \eta  > 1.3$             | 全 L1_MU20         | $ \eta  > 1.3$                       | 全 L1_MU20         |

| Seq. requirement | $0.907 \pm 0.004$          | $0.925 \pm 0.004$ | $0.993 \pm 0.030$                    | $0.997 \pm 0.020$ |

| +dθカット           | $0.660 \pm 0.004$          | $0.724 \pm 0.003$ | $0.979 \pm 0.030$                    | $0.991 \pm 0.020$ |

| +Δη/φカット         | $0.226 \pm 0.002$          | $0.327 \pm 0.002$ | $0.926 \pm 0.029$                    | $0.967 \pm 0.020$ |

Table 7: NSW における各カットのリダクションと検出効率 [36]

Figure 37 を見ると、 $d\theta$ カットと $\Delta\eta/\phi$ カットをかけることで、 $L1\_MU20$  の RoI 数を 37% 削減することができる. Table 7: NSW における各カットのリダクションと検出効率したがって、Table 7 を見ると  $L1\_MU20$  のリダクションが 23%だとわかる. Figure 38 の結果をあわせても、十分な検出効率を保ったままリダクションをかけられることがわかる.  $d\theta$ カットおよび $\Delta\eta/\phi$ カットは有効な対策だとわかる.

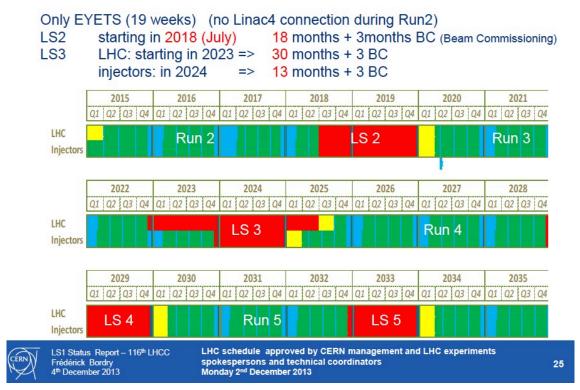

## 5.2. LHC アップグレード計画

### LHC schedule beyond LS1

Figure 39: LS1 以降の LHC アップグレード計画 [39]

以下にLS1からLS3までの具体的内容をまとめた.

Long Shutdown 1 (2013-2014) では、エネルギーを 8TeV から 13, 14TeV に向上し、そのため加速管同士の結合を強くし、消耗した磁石を交換し、さらに放射線対策のためにエレクトロニクスを移動した.

Long Shutdown 2 (2018-2019) では、ルミノシティを Run1 の  $0.77 \times 10^{34}$ cm<sup>-2</sup>s<sup>-1</sup> から約二倍の  $2\sim 3\times 10^{34}$ cm<sup>-2</sup>s<sup>-1</sup> に引き上げる予定である. LIU (LHC Infectors Upgrade) が予定され、Linac2 を Linac4 へ移行し、さらに日本が大きく寄与している J-PARC の金属磁性合金を用いた高周波加速空洞を使用して PS Booster のエネルギーを増加することが計画されている.

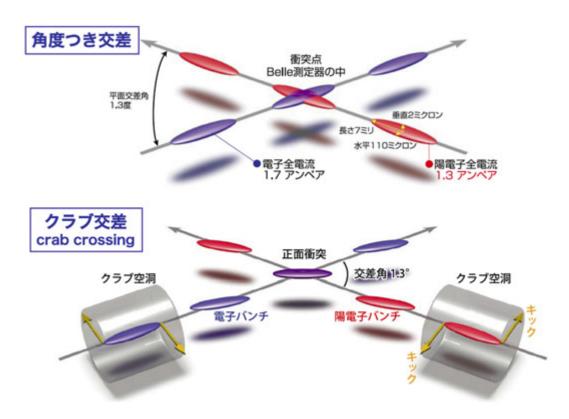

Long Shutdown 3 (2023-2025) では、ルミノシティを最終的な  $5 \times 10^{34} \text{cm}^2 \text{s}^{-1}$  に引き上げる予定である. 超伝導クラブ空洞 [40]の導入や Interaction Region (IR) の磁石の強化が検討されている. クラブ空洞というのは、ビームのバンチを回転させる事でルミノシティを向上させる技術である. 日本の筑波にある高エネルギー加速器研究機構 (KEK) が所有する KEKB で 2007 年に導入されると、設計値のほぼ 2 倍のルミノシティを実現し、その効果が確かめられた [41].

Figure 40: クラブ衝突の概念図 [41]

## 5.3. ATLAS アップグレード計画

LHC のアップグレード計画に伴って、ATLAS 検出器もアップグレードする. 目的は放射線によって劣化した加速器の部品の交換や、高ルミノシティ対応の測定器の導入などである. 例えば、前者についてシリコントラッカーや Inner Triplet Magnet は積分ルミノシティ100fb<sup>-1</sup> で放射線損傷により劣化する. また、後者について、高ルミノシティ化ーーすなわちー回あたりの衝突回数が増えることによって一一衝突あたりに得られる実験データが増える. これには、エレクトロニクスを改良して対処する必要がある. エレクトロニクスの改良は、三回の LS に合わせて部分的に行われる. LHC の LS1、2 および 3 中に行われるアップグレードは ATLAS ではそれぞれ Phase-0 アップグレード、Phase-1 アップグレードおよび Phase-2 アップグレードとも呼ばれる.

本論文は ATLAS 検出器に使われるミューオン検出器について焦点をあてている. 現在のミューオン検出器は,目標の高い横運動量をもつミューオン以外をそれだと誤認する. そのため, Phase-1 アップグレードで新たに New Small Wheel というハードウェアを導入するのは 5.1 フェイクミューオン(P.44)で確認した通りである.

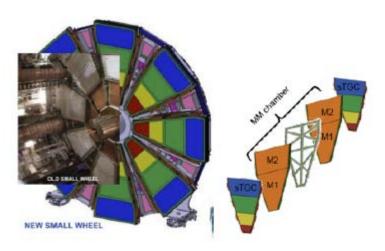

### 5.4. New Small Wheel 概要

Figure 41: 現在の Big Wheel (黄色い四角で囲まれた領域)と Small Wheel (青い四角で囲まれた領域) [37].

2018/19 年の Long Shutdown 時に Small Wheel (Figure 41 の青い四角の枠線で取り囲まれた領域)と交換され取り付けられる予定の New Small Wheel は 8 層で構成され、それぞれの層は Micromegas および small-strip Thin Gap Chambers (sTGC) で構成される. いずれも, 総面積 2500 m²以上の表面にわたってトリガーとトラッキングを行う.

### New Small Wheel の解像度

New Small Wheel は軌跡が衝突点由来のものか明確に判断するために,空間分解能 100  $\mu$  m, 角度分解能 1 mrad という高解像度で設計される. 現在の ATLAS Big Wheel は Figure 36 のフェイク (a) や (b) も含めて受け取っているが, New Small Wheel はフェイク (a) や (b) を落とし, さらに現在のトリガーレートを維持することを可能にする. これは, 現在設置されている Small Wheel ではできないことだ.

### New Small Wheel のレイアウト

New Small Wheel は現在のミューオン・スペクトロメータと同様, 16 個のセクター (8 枚のスモール・セクター, 8 枚のラージ・セクター) で構成される. Figure 42 左図に現在の Small Wheel の写真と New Small Wheel の CG 図を重ねて示す. 16 個あるセクターのそれぞれは二層のマルチレイヤー (内部にさらにレイヤーを含む) で構成され, それぞれのマルチレイヤーは small-strip Thin Gap Chambers (sTGC) および MicroMegas (MM)で構成される. Figure 42 右図の示す通り, New Small Wheel はサンドウィッチ型の構造で, sTGC – MM – MM – sTGC となっている. これは, 二枚の sTGC 間の距離を最大にし, 軌跡の角度分解能を上

げるためである.

Figure 42: 現在の Small Wheel の写真と New Small Wheel のデザイン図を重ねた(左図). New Small Wheel の sTGC – MM – MM – sTGC というレイヤー構造を示した(右図) [37].

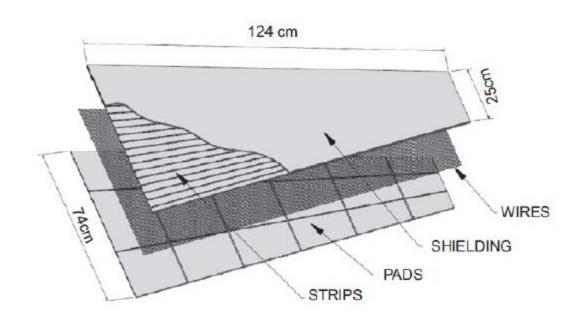

### sTGC 技術

Figure 43 に sTGC の基本的な構造を示す. 金メッキされた  $50\,\mu$  m のタングステンのワイヤを 1.8mm 間隔で並べ 2.9kV の電圧をかけ, そのワイヤから 1.4 mm 離れたところからカソードの板でサンドイッチのように挟む.

Figure 43: sTGC の構造 [37]

カソードはグラファイトエポキシでできており、その表面には  $100\,\mu\,\mathrm{m}$  の厚さの G-10 (表面の抵抗は  $100\mathrm{k}\Omega/\Box$ )が塗られている。そのコーティングの裏面にはワイヤと垂直な方

向にストリップが 3.2mm 間隔で配置される. ストリップはパッドとシールドで挟まれている. この構造は Figure 44 に示す. ピッチ間隔が 3.2mm というのは, ATLAS TGC のピッチよりもかなり狭いので、"small TGC"と名付けられた.

Figure 44: sTGC のレイヤー構造 [42]

### Micromegas

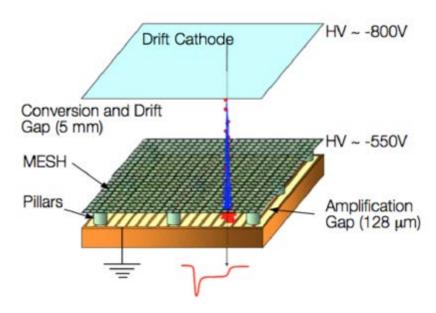

NSW に使われる Micromegas (MM) の基本的な構造は Figure 45 に示す. Micromegas というのは micro mesh gaseousstructure の略である.

カソードに-800V の大きい負電圧をかけ、メッシュには-550V の負電圧をかける. カソードとメッシュの間隔は 5mm のドリフト・ギャップであり、このギャップには数百 V/cm のドリフト電場がメッシュからカソードの方向に発生する. また、アノードストリップ (Figure 45 の最下層) はプリアンプを介して接地されている. メッシュとストリップ間は 128  $\mu$  m あいており、メッシュとストリップ間の電場は 40-50 kV/cm [37]の増幅電場が発生する. この高電場領域が増幅域である. 荷電粒子が MM を通過すると、ドリフト・ギャップ中のガスと衝突して電子を放出する. これは種電子と呼ばれる. 種電子は他のガスに衝突し、さらに二次的な種電子を放出する. これらの電子はドリフト電場によってメッシュ方向へ運ばれると、増幅領域で電子雪崩によって増幅される. 0.425mm 間隔のアノードストリップに落ちた電荷はプリアンプによって電圧信号に変換され、それらを読みだすことで、粒子の位置情報を知ることができる. 増幅域にはメッシュを支えるピラー (pillar、支柱) があるが、これらは MM の不感領域となる. 荷電粒子の入射角度が大きいと、一つのストリップあたりが検出する電荷が減るため、増幅電場を大きくしたくなるが、大きすぎると放電が生じ

る. New Small Wheel の MM は放電を防止するためにストリップを抵抗層で覆っている [43].

Figure 45: Micromegas の構造 [37]

sTGC と MM から出るデータは 2.5M あり, これらは精度や速度の要求から ASIC を使った独自のフロントエンドを構築されている.

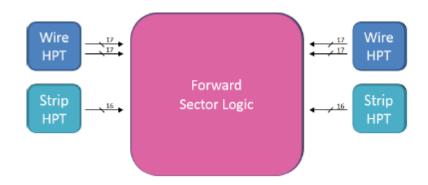

## 6.新 Sector Logic 設計

前章で示した通り、Phase-1 アップグレード中に新検出器 NSW を導入し、RUN3 の検出で用いる予定である。これにより $p_T$ =25GeV を維持しつつ6割もトリガーレートを削減する。 NSW で取得したデータと BW で取得したデータのコインシデンスは、Sector Logic 内部の R- $\phi$ コインシデンス後に行う。したがって、RUN3 以降の Sector Logic は既存の HpT からの入力ポートに加えて、NSW からの入力ポートも備えている必要がある。

また、Sector Logic のリードアウト部分も改良する必要がある。現状では PS ボード内の SLB ASIC をリードアウトに流用している。このため、SLB ASIC の読み出しのために SSW という SLB ASIC 専用の読み出しハードウェアを使用し、ROD へ送信している。 Sector Logic のアップグレードでは、SLB ASIC と SSW の転用を廃止し、専用の読み出しラインを確立する予定である。

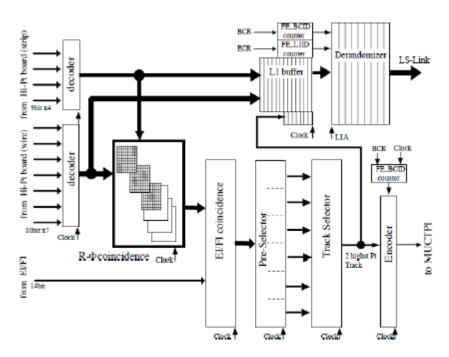

## 6.1. 現行の Sector Logic 概要

Sector Logic はトリガー系の最終段階を担当している。その役割は主に次の二つがある。 TGC のワイヤーヒット情報とストリップヒット情報からミューオントラックの  $p_T$  を 算出し、各トラックの RoI を決定する

Sector Logic が受け取ったデータを、L1A を受け取った瞬間のバンチ、およびその前後の 1 バンチずつ、合計 3 バンチを選び、L1ID、BCID や SLID を付加して SSW に送信する役割を果たす。L1A 信号は、発行されると、次の 2 クロックで次の L1A が発行されることはない仕様である。

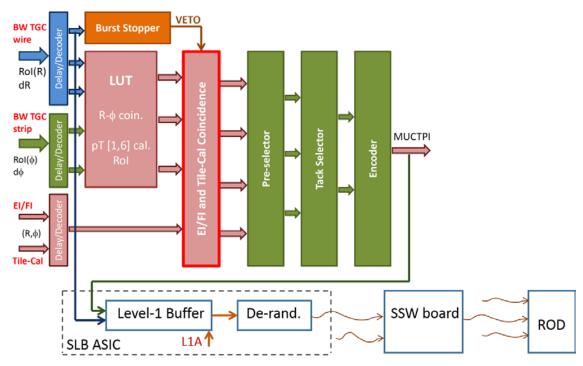

Figure 46 に Sector Logic のブロック図を示す.

Figure 46: Sector Logic のブロック図 [31]. 現行の Sector Logic はコインシデンス部分に FPGA で, 読み出し部分は SLB ASIC で実装されている.

Sector Logic が受け取るワイヤーヒット情報とストリップヒット情報は、まず右上のレベル 1 バッファーに送られ、そして中央左の  $R-\phi$ コインシデンス部分に送られている。前者は読み出し系、後者はトリガー系のデータの流れである。前者のレベル 1 バッファー、その後のデランダマイザは PS ボードにまとめられた SLB ASIC を転用して実装し、通常のTGC ヒットデータと同様の処理を行っている。後者の  $R-\phi$ コインシデンス部分以降は Sector Logic に搭載された FPGA で処理している。

## 6.2. Sector Logic ボード

Sector Logic ボードにはエンドキャップ用, フォワード用の二種類がある. 一枚で 2トリガーセクターをカバーする. Sector Logic は USA15 という部屋に設置されている. この部屋は検出器から 100m ほど離れた位置にある. 放射線のダメージを受けにくくするためだ. ATLAS では 144トリガーセクターを処理するために 72 枚の Sector Logic ボードが使用されている.

# 6.3. Sector Logic への入力

Sector Logic には主に二つの入力経路がある.一つは HpT ボードから送られる BW High-Pt コインシデンス情報,もう一つは PS ボードから送られる EL/FI 情報である.それぞれ G-Link という通信プロトコルで,光ケーブルを用いて転送される.このプロトコルは 1 クロックで 16bit (オプションで 17bit) を転送する.HPT ボードと PS ボードはともに TTC クロック (40.079MHz) に同期して信号を転送している.したがって,各ボードから転送される信号の スループットは 16bit (17bit) × 40 MHz = 640 Mbps (680 Mbps) となる.

### TGC-BW からエンドキャップ Sector Logic への信号

エンドキャップ部分では、1トリガーセクターあたり 6本の光ファイバーをで HpT ボードからのデータを受け取る。6本中 4 本は Wire の信号に用いられ、クロックごとにそれぞれ 17bit、17bit、17bit、16bit の信号を転送する。これは合計 67bit となる。6 本中 2 本は 8Strip の信号に用いられ、クロックごとにそれぞれ 17bit、17bit の信号を転送する。これは合計 17bit、17bit の信号を転送する。これは合計 17bit となる。170 を 170 と 170 を 170 と 170

### TGC-BW からフォワード Sector Logic への信号

EI/FI からの情報はエンドキャップ部分にのみ入力される. 一枚の Sector Logic ボードは 4 本の光ファイバーで 64bit の EI/FI 情報を受け取るが、この情報は 2 つのトリガーセクターで使われるので、受け取った情報は Sector Logic ボード内で 2 つにわけられ、それぞれ FPGA に入力される.

Figure 47: トリガーセクター2 つから Sector Logic エンドキャップへの信号線 [38]

Figure 48: トリガーセクター2 つから Sector Logic フォワードへの信号線 [38]

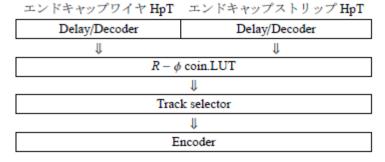

## 6.4. コインシデンス

現行の Sector Logic はコインシデンス部, ディレイ, デコーダー, R- $\phi$  コインシデンス, エンコーダからなる. その流れを Figure 49 に示す.

ディレイ回路は信号の入力時間を遅らせることができ、最大 15.5CLK, ディレイ間隔 0.5CLK の遅延をつくる.

デコーダーは受信した信号からミューオンのヒット位置,  $\Delta R$ ,  $\Delta \phi$  の値を抽出する.

$R-\phi$  コインシデンスはデコーダーで得た $\Delta R$ ,  $\Delta \phi$ 情報から LUT を参照して SSC ごとに $p_T$ を算出する.

Track Selector は SSC から受けた情報のうち最大で 2 トラックを PreSelector と FinalSelector という二段階処理で選び出す.

エンコーダはレベル 1 トリガーを MuCTPI に送信し、また HpT ボードからの入力情報やトリガー情報を SLB ASIC に送る. MuCTPI に送る情報は最大 2 トラックの $p_T$ や RoI 情報、バンチ識別などで 32bit となっている.

Figure 49: 現行の Sector Logic への入力から出力まで [38]

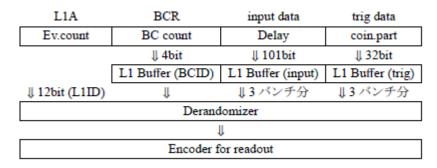

### 6.5. 読み出し

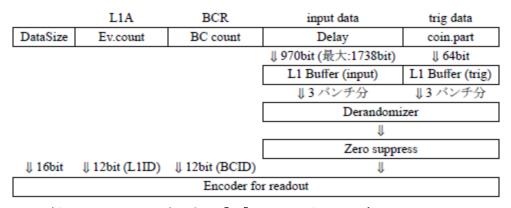

SLB ASIC を用いた現行 Sector Logic の読み出し部分を Figure 50 に示す.

読み込むデータは入力データ 101bit, コインシデンスデータ 32bit, そして BCID (バンチカウンタ ID) 4bit である. これらは直ちに L1 バッファーに格納される. Sector Logic が L1A 信号を受け取ると, L1 バッファーから前後含めた 3 バンチのデータを受け取り, レベル 1 イベントカウンタから 12bit の L1ID を付加し, ROD に渡す.

Sector Logic ボード一つあたり、2トリガーセクターからのデータを受け取るが、そのため SLB ASIC を 2 つ用いている.

Figure 50: 現行 Sector Logic の読み出し [38]

## 7. 現行 Sector Logic の変更点

本章では、Sector Logic の変更点および RUN3 以降で用いる新 Sector Logic への要求を確認したのち、実際に開発されたプロトタイプについて見ていく.

新 Sector Logic には次の2つの要求がある.

- フェイクミューオンを削減する NSW からの追加入力で入力が 1536bit になる.

- SLB ASIC の流用を廃止し、新 Sector Logic 独自の読み出しラインをつくる.

これらについて、7.1New Small Wheel からの追加入力、および 7.27.2 新 Sector Logic 読み出し方式に解説した、7.3 新 Sector Logic プロトタイプには、開発した新 Sector Logic のプロトタイプについて、用いられた技術とともに記述した.

## 7.1. New Small Wheel からの追加入力

### New Small Wheel 追加入力のフォーマット

新 Sector Logic には HpT からはこれまでと同様にトリガーセクター2 つから計 202bit の入力があるが、新 Sector Logic には、さらに NSW からの入力がある.  $d\theta$  については分解能 1mrad で、15mrad 程度のカットをかけると、5bit のデータになる. また、R は 8bit、 $\phi$  は 6bit で十分であり、New Small Wheel ヒット情報の 4bit、予備 1bit の合計 24bit/track のデータが入力される. 1fiber あたり 4track のデータを転送する計画である. また、fiber の数は 12 本使う予定である. 1fiber には 4track の他に、コンマ信号や ID なども付加するので、合計 128bit (Figure 51) の入力になっている. コンマ信号は 8b10b エンコーディングで使われるコンマ信号のことである. これら 128bit は LHC クロックに同期して入力されるよう設計されている.

| Words (16-bit) | first byte |                      | second byte |  |

|----------------|------------|----------------------|-------------|--|

| Word-0         | comma      |                      | comma       |  |

| Word-1         | track-0    |                      |             |  |

| Word-2         |            |                      |             |  |

| Word-3         | track-1    |                      |             |  |

| Word-4         | track-2    |                      |             |  |

| Word-5         |            |                      |             |  |

| Word-6         | track-3    |                      |             |  |

| Word-7         | ID (4-bit) | 4-bit) BCID (12-bit) |             |  |

Figure 51: NSW 追加入力 128bit のフォーマット [44]

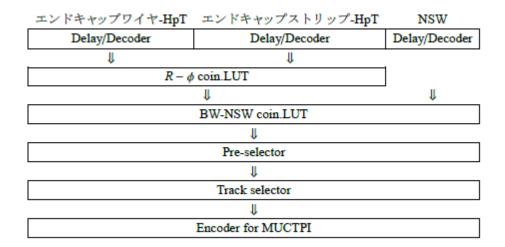

### コインシデンス

新 Sector Logic のコインシデンスを Figure 52 に示す. 新たに NSW と BW のコインシデンスをとっている.

Figure 52: 新 Sector Logic のコインシデンス [38]. 新たに NSW と BW のコインシデンスが 追加されている.

## 7.2. 新 Sector Logic 読み出し方式

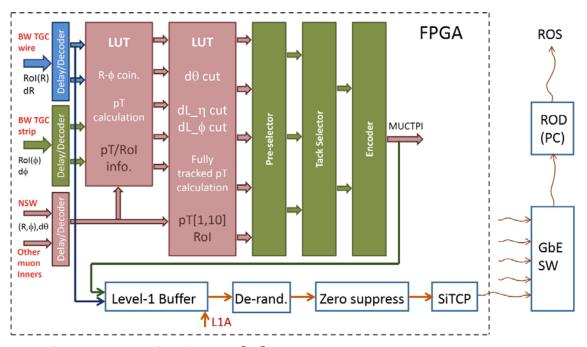

現行 Sector Logic の読み出し方式 (Figure 53) と新 Sector Logic 読み出し方式 (Figure 54) を比較して説明する.

Figure 53 および Figure 54 の点線枠内が Sector Logic である. 現行の Sector Logic に比べ, 新 Sector Logic の果たす機能が大幅に拡張していることが見てとれる.

Figure 53: 現行の Sector Logic 読み出し方式 [44]

Figure 54: 新 Sector Logic 読み出し方式 [44]

現行では SLB ASIC の中に L1 バッファー, デランドマイザがある. これらロジックを 搭載した Sector Logic 複数台を SSW でまとめ, ROD にデータを渡している. 現行の ROD も

ハードウェアモジュールである. 新 Sector Logic では SLB ASIC を廃止し、コインシデンスロジック同様に読み出しロジックも FPGA に設計される. 現行の SSW はゼロサプレスやフォーマット整形を行っているが、新 Sector Logic では SSW も廃止し、これら機能も FPGAに搭載される.

新 Sector Logic からの読み出しには TCP を用いる. 現行の SSW の代わりに Gigabit Ethernet Switch (GbE Switch) を使用する. これは今後のアップグレードを容易にする. この新 Sector Logic 複数台を GbE Switch でまとめ, 新 ROD ヘデータを渡す. 現在 SSW の後段にあたる ROD はカスタム設計されたハードウェアを用いているが, Sector Logic の読み出しを TCP にすることにより, ROD を一般的なノート PC に代えて信号を受信できるようになる.

また、新ROD からは、新 Sector Logic  $\sim$ 次のような要請がある. 即ち、データを $\sim$ のような要請がある. のも、データを $\sim$ のような要請がある. のも、でした。 でした。 でした。 でいる。

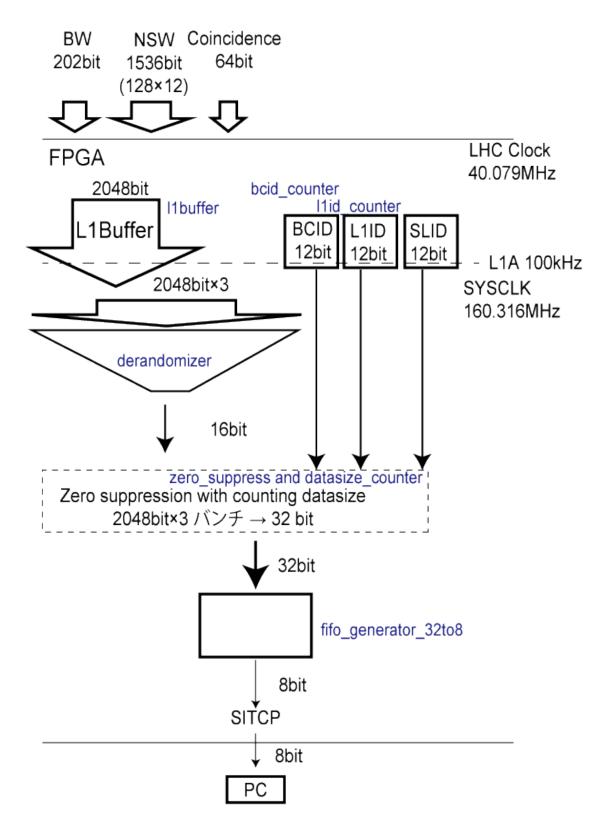

以上をふまえ,新 Sector Logic に要求されるロジックを一つ一つ見ていく. 新 Sector Logic には次の機能が要求される.

- BCID カウンタ機能

- L1ID カウンタ機能

- ゼロサプレス機能

- データサイズカウント機能

- ゼロサプレス機能

- ID 情報をゼロサプレス後に付加させる機能

これら機能は、新 Sector Logic に搭載された FPGA によって処理される. まず、FPGA 内部のデータの流れの全体を見て、その後に機能の一つ一つを見ていく.

まず、Figure 55 を見ていただきたい。BW、NSW からのデータおよびコインシデンスが FPGA に入る。これらは整形され 2048bit になり、L1 Buffer に格納される。128 Clock 後、L1A 信号が発行されると、前のバンチと次のバンチを含む 3 バンチ分がデランダマイザに格納される。L1A が発行されなかった場合の 2048bit は捨てられる。また、L1A が発行されたときの BCID、L1ID および SLID の値はゼロサプレス内部の FIFO に格納され、読み出しじに使われるまで待機する。デランダマイザは多段 FIFO で構成されており、16bit を出力する。出力された 16bit はゼロサプレスに入り、3 バンチ分のデータサイズをカウントし終えると、フォーマットを整えて BCID、L1ID、SLID とともに 32bit×データサイズの分だけ出力される。そして、FIFO によって 8bit にされ、SiTCP を通して PC へと出力される。

Figure 55: 新 Sector Logic のデータフロー. 青文字は FPGA に書き込んだ Verilog HDL コードのモジュール名である.

### BCID カウンタ

FPGA 内部で順次処理することで,陽子バンチを数える 12bit のカウンタであ.陽子バンチは TTC クロック 40.079 MHz で衝突するので,このカウンタも 40.079 MHz でカウントすることになる. 周長 27kmの LHC にはバンチが 7.5m間隔で並ぶ.LHC リング一周 3564 バンチあるが,その全てに陽子があるわけではない. そのうちの 2808 バンチのみ陽子が入る.したがって,12bit あれば 4096 個まで数えられるので,リング中のバンチと BCID は一対一対応する.

### L1ID カウンタ

FPGA 内部で順次処理することで, L1A 信号が発行されるたびにカウントする 12bit のカウンタである. 後段の Read Out Driver では L1ID を 24bit で数えているので, その下位 12bit と Sector Logic の L1ID 12bit を比較して対応をとる.

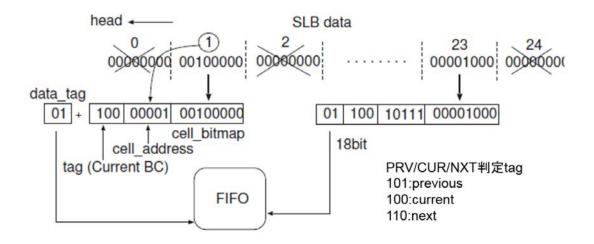

### ゼロサプレス

入力信号の増加にともない、ゼロサプレスも改良が必要である.

現行のゼロサプレスは,入力信号 202bit を 8bit ごとに区切る(この区切られた単位をセルと呼ぶ). 区切られた 8bit が先頭から何番目であるかは,アドレス 5bit で指定する.このロジックは $2^5 \times 8 = 256$ bit までしか扱えず,新 Sector Logic の入力,即ちバンチあたり  $12 \times 128 + 202 + 64 = 1802$  bit のデータを処理できない.

Figure 56: 現行ゼロサプレス [38]

そこで、新たなゼロサプレスが考えられた. バンチタグ(3 バンチのいずれであるか)4bit、セルアドレス 8bit、セルデータ 16bit である. これなら、セルは $2^8 = 256$ 個指定できる. この数は1 バンチあたりのセル 2048/16 = 128 より多い. Table 8 にそのフォーマットを示す.

| 31       | 28 | 24  | 16          | 0         |

|----------|----|-----|-------------|-----------|

| 1111 tag |    | tag | Cel address | Cell data |

Table 8: 新ゼロサプレスのフォーマット

先行研究によれば、このゼロサプレスを ATLAS の過去のデータに試したところ、0.05% 以下に圧縮されたので、このゼロサプレスは有効であると判断した [38]. ただし、tag の値や フォーマットはデータ可読性のため若干変更した. 具体的には、Tag は

0001: Previous

0011: Current

0111: Next

を意味し,16bit のデータがどの 3 バンチのデータであるかを示す. 新ゼロサプレスの圧縮率は,RUN1 のデータを用いて 0.3%以下 [38]であったことから,その効果がわかる.

#### データサイズカウント

データサイズカウントは、新 ROD の要求による。新 ROD はデータを受けると、ただちにデータサイズ分だけのメモリを確保する必要がある。そこで、ゼロサプレス後のデータ量がいくらあるのか知るために、3 バンチ分の入力があると、16bit ごとに 1 を含むかカウントする。新 Sector Logic の入力は 202 bit + 128 bit/fiber  $\times$  12fiber = 1738 bit、スループットは1738 bit  $\times$  40 MHz = 69.52 Gbps であり、現行の Sector Logic の 8 Gbps に比べて 9 倍である。しかし、L1 Buffer の入力の際に FIFO の都合上、2048bit になるようパディングしている。なので、データサイズの最大値は、

### 3 バンチ×2048bit/バンチ÷16bit = 384

により、384 だとわかる. しかし、これは非現実的な想定であり、実際のデータはほぼ 0 が並ぶ. なので、データサイズはとても小さい値になる.

### 新 ROD 向け新 Sector Logic 読み出しデータフォーマット

これは先行研究 [38]との変更点はない. 新 ROD 向けに, ヘッダのあとデータサイズが付されている. 新 ROD はこのデータサイズを承けてメモリを確保する.

| 16bit                             |              | 16bit            |            |  |

|-----------------------------------|--------------|------------------|------------|--|

| ヘッダ 0x0B0D 16bit                  |              | Datasize 16bit   |            |  |

| 0x000                             | 0x0000 16bit |                  | L1ID 12bit |  |

| 0x0 4bit                          | BCID 12bit   | 0x0 4bit         | SLID 12bit |  |

| ゼロサプレスされた 3 バンチ分のデータフォーマット        |              |                  |            |  |

| 0xF, tag, cell address, cell data |              |                  |            |  |

| 0x0000 16bit                      |              | フッタ 0x0E0D 16bit |            |  |

Table 9: 新 Sector Logic 読み出しフォーマット

最後に, 読み出しの流れを Figure 57 に示す.

Figure 57: 新 Sector Logic の読み出し [38]. ゼロサプレスやデータカウントロジックが追加されている.

# 7.3. 新 Sector Logic プロトタイプ

本研究では実際に新 Sector Logic のプロトタイプを CADENCE OrCAD を用いてデザインし、読み出し評価を行った. これまでは、汎用モジュールを使ったテストしか行っていなかったので、新 Sector Logic のプロトタイプを作成するのは初の試みであった.

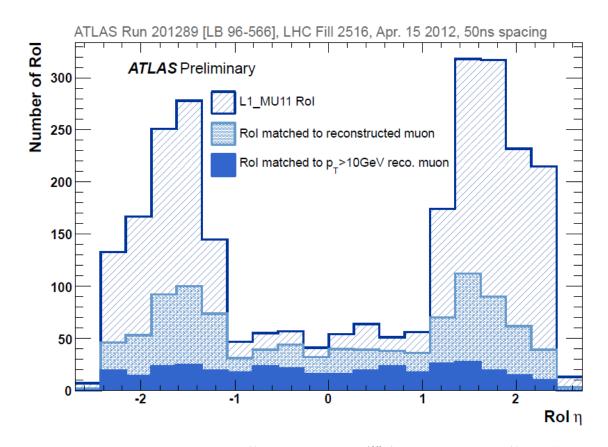

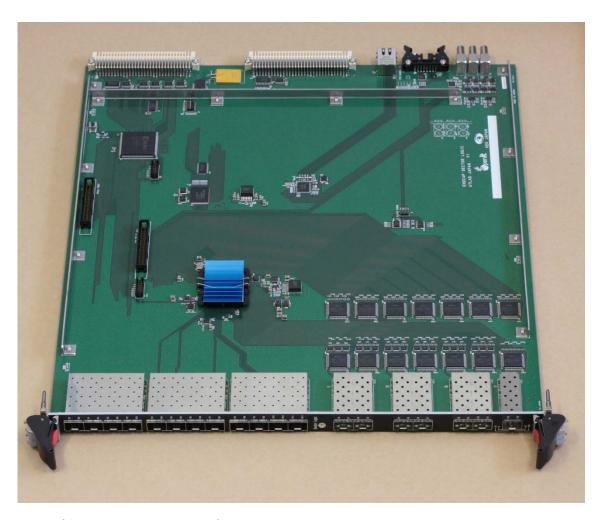

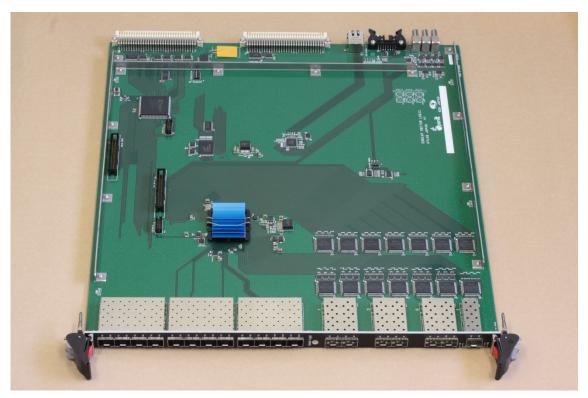

試作機は二つ作製された. Figure 58 と Figure 59 にそれぞれの写真を示す. いずれも仕様は同一であるが, 万が一の不具合や, スイスおよび日本での開発を考慮して二つ作製された. 本章には新 Sector Logic に使われた技術について述べた.

Figure 58: 新 Sector Logic 一つ目. 左下が GTX ポート, 右下が G-Link ポートである. イーサネットのポートは写真の右上にある.

Figure 59: 新 Sector Logic 二つ目. 左下が GTX ポート, 右下が G-Link ポートである. イーサネットのポートは写真の右上にある.

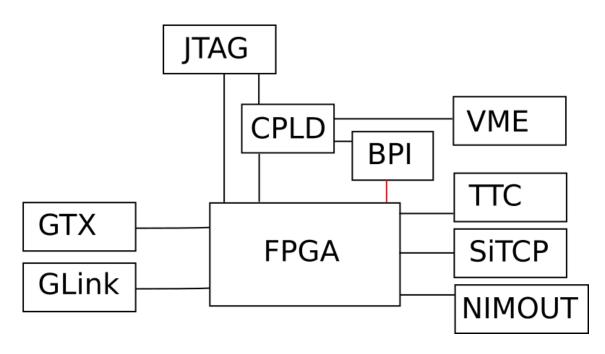

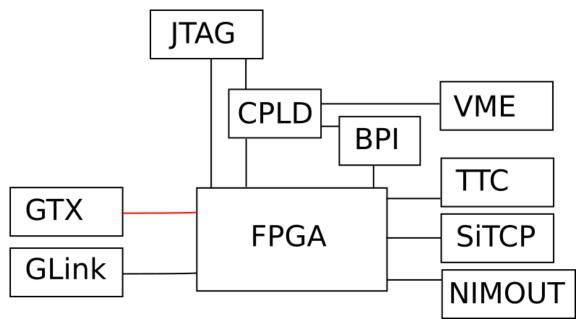

#### **FPGA**

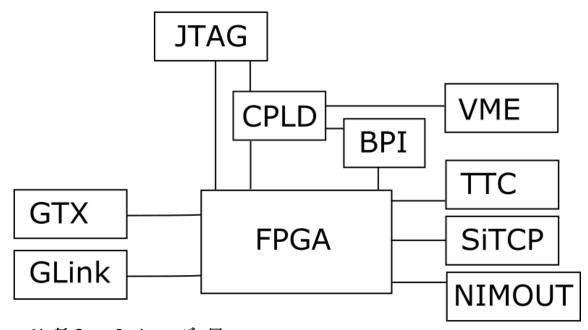

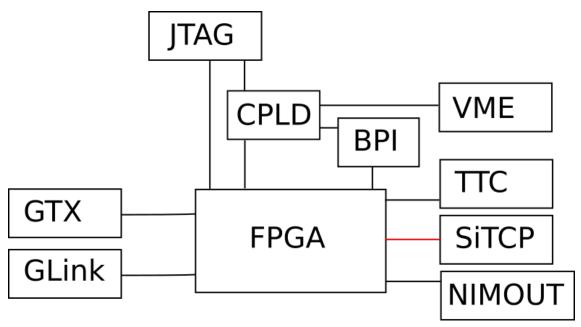

新 Sector Logic には米 Xilinx 社の FPGA (Field Programmable Gate Arrays ) から Kintex-7シリーズ XC7K325T-2FFG900 が採用された. これは, 新 Sector Logic の FPGA に求められるピン数が約 500 であること, GTX Transceiver を最大 16 レーン搭載できることから採用が決まった.

### **CPLD**

CPLD (Complex Programmable Logic Device) は不揮発性のメモリを用いたプログラマブルロジックである. Xilinx 社の CoolRunner-II XC2C256-7PQ208C を用いた. これは VME 制御および FPGA のコンフィギュレーションを行う.

### Ethernet PHY

LAN ケーブルで Gigabit Ethernet を通すため, 新 Sector Logic には MICROCHIP 社のLAN8810-AKZE(LAN8810i-AKZE)を載せている.

### クロック

新 Sector Logic には FPGA 駆動用の 40.079MHz と GTX の reference clock である 160.316MHz が載せてある. FPGA 駆動用のクロックはジャンパーピンで三種類のクロックソースを選ぶことができるように設計されており、一つ目は水晶 (MXO3-7050C-40.079MHz(SPECIAL)) によるクロック、二つ目は外部から任意周波数のクロックを NIM で供給され、三つ目は TTC から供給されるクロックである. 実際の運用では三つ目の TTC からのクロックを用いることになる.

### G-Link

G-Link は HPT ボードからの入力を受ける通信プロトコルである. これは現行の Sector Logic でも採用されている規格である(周辺の一部の IC チップは廃盤だったため新しいものに取り替えた).

#### **GTX Transceiver**

GTX Transceiver は米 Xilinx 社が開発した高速シリアル通信のプロトコルである. これは NSW からの信号を受けるプロトコルであり, 新 Sector Logic で採用された Kintex-7 では最大 12.5Gbps の通信が可能である [4].

GTX は IBM 社が開発した高速シリアル転送方式である 8b10b エンコーディングを用いて信号をシリアル化している. これは,転送するべき信号を 8bit 単位で区切り,それぞれ規定の表を参照して 10bit に変換するものである. 一見すると,まるでデータ量を 1.25 倍に増やすだけで何も利点がないと思われるかもしれない. しかし,高周波における転送では,しばらく電圧が Low だった後の電圧が上がり切らないことや,逆にしばらく電圧が High だった後の電圧が下がりきらないことが起こりうる. たとえば,転送するべきデータが 1111 1110 1111 のように連続する High の中に Low が一箇所だけ混ざっている場合だ. 8bit は 256 通りしかないが,10bit は 1024 通りあり,どのような 8bit の信号も Low または High が 4 クロック以下になるように変換することができる.また,これによりデータとクロックを同じ配線で送受信することが可能となる.したがって,帯域の 20%をロスするだけの意味はある.

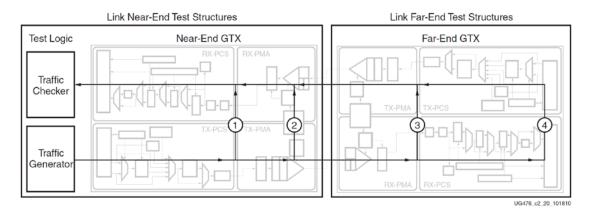

GTX Transceivers にはループバック機能があり、インターフェースから送信した信号を 直ちに RX で受け取ることができる. 今回のループバック試験ではこのループバック機能を 用いた. ループバックの経路には、Figure 60 に示すように 4 通りの経路がある.

Figure 60: GTX のトポロジー [4]. TX から RX へのループバックは四カ所の折り返し地点を選ぶことができる.

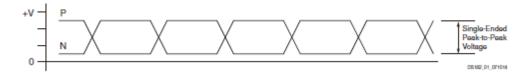

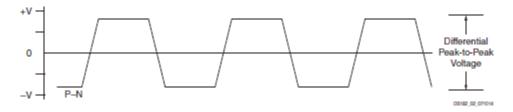

Kintex-7 Series FPGA では、出力の peak-to-peak 差動電圧 (Differential peak-to-peak output volrage) は最低 1000 mV (最大スイング) 以上、入力の差動 peak-to-peak 電圧 (Differential peak-to-peak input voltage (external AC coupled)) は最低 150 mV、最大 1250 mV (> 6.6Gbps) または 2000 mV (< 6.6Gbps)が推奨される [45].ここで言う peak-to-peak の電圧とは、入出力の差動信号 P と N の差から得られる信号のことである. Figure 61 の P と N の差をとったものが Figure 62 の信号であり、今最低値と最大値を規定したものである。

新 Sector Logic は、160 MHz のクロックを用い、6.4 Gbps の GTX を 12 本使い、76.8 Gbps の通信をするよう設計されている.

Figure 61: Single-Ended Peak to Peak Voltage [45]

Figure 62: Differential Peak-to-Peak Voltage [45]

### **SiTCP**

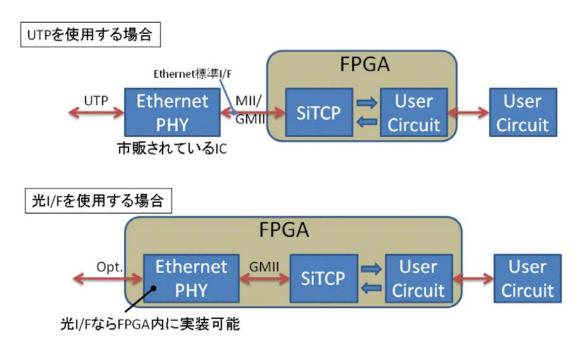

SiTCP は FPGA 上にネットワーク処理回路を実装し、FPGA をイーサネットに接続させ

る技術である. 新 Sector Logic の読み出しに採用された. これにより, 従来ハードウェアだった ROD を廃止し, 一般的なパソコンで新 Sector Logic から出た信号を受信できるようになった. ハードウェアの並列処理のおかげで, イーサネットの上限値で転送を行うことも可能である. 更なる利点として, SiTCP の実装に必要なチップは, Ethernet PHY チップおよび MAC アドレス用に EEPROM のみである. また, Ethernet 通信インターフェースに標準 MII/GMII を採用しているので, さまざまな PHY デバイスとの接続が可能である.

Figure 63: SiTCP の実装例 [46]

# TTCrq コネクタ

TTC から LHC クロック, トリガー信号や L1A 信号を受け取るため, TTCrq を用いている. これが TTC から来た信号をデシリアライズする. 実物を Figure 64 に示す.

Figure 64: TTCrq コネクタ

### NIM

高エネルギー実験でよく仕様される NIM (Nuclear Instruments Modules) 信号の送受信が可能である. 新 Sector Logic には 4 本の NIM コネクタを搭載している. また, 外部クロックの入力にも NIM を用いている.

# JTAG ピン

Xilinx 社の FPGA と CPLD にプログラムを書き込むための JTAG ピンヘッダである. このピンとパソコンの USB ポートを Xilinx 社製プラットフォームケーブル (ダウンロードケーブル, JTAG ケーブルとも呼ばれる) を用いて接続し、プログラムを書き込む. Figure 58 および Figure 59 の中央左 (青い放熱板の左) である.

Figure 65: Xilinx 社のプラットフォームケーブル [47]

# 8.新 Sector Logic 評価

# 8.1. 新 Sector Logic - IO ポート試験

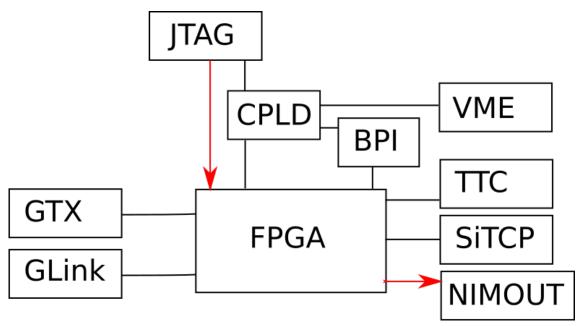

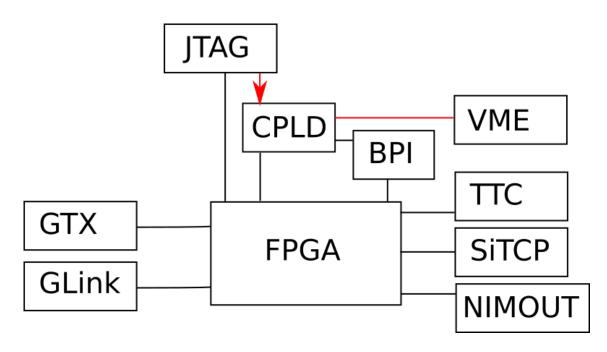

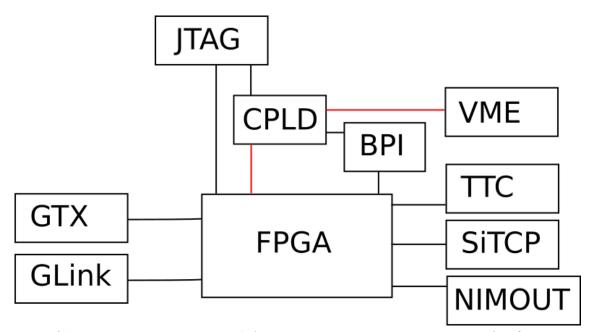

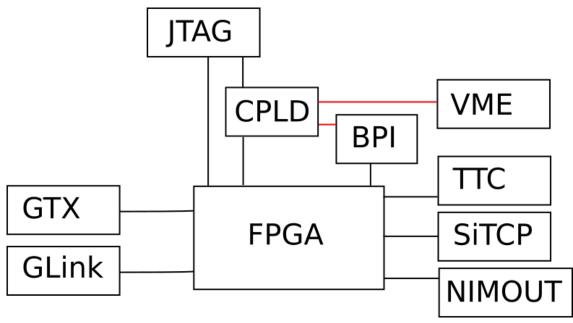

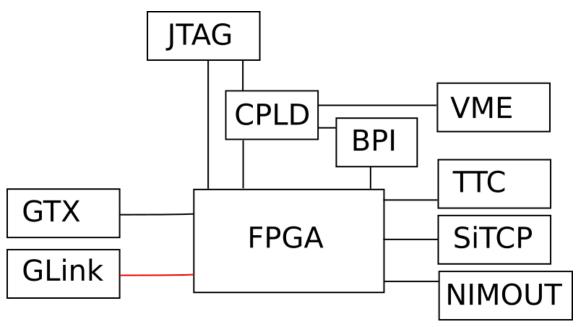

何よりもまず、納入された新 Sector Logic の各 IO が正しく動作するか確認する必要がある. 例えば、ハンダ付けに不良がないか、回路設計がそもそも間違っていないかといった問題がないか調べる. 検証の結果、二枚ある新 Sector Logic のうち、一枚の GTX クロックに問題があることがわかった. 本章では項目ごとにテストを説明した. Figure 66 に新 Sector Logic の概要図を示す.

Figure 66: 新 Sector Logic のモデル図.

# **FPGA Configuration**

検証目的: FPGA へ書き込みができるか

検証方法: JTAG ケーブルを用いて FPGA にテストデザインを書き込んだ. テストデザインは入力クロックを 2 倍, 4 倍に分周した信号を NIM OUT から出力するものだった. NIM の出力はオシロスコープで確認した.

検証結果: FPGA への書き込みに成功した.

Figure 67: 新 Sector Logic の IO ポート試験. JTAG から FPGA で書き込み, NIM でデータを読みだすこと、すなわち図の赤い配線が正常に動作することを確認した.

# **CPLD** Configuration

検証目的: CPLD に書き込みできるか.

検証方法: Single Board Computer(SBC) から VME 通信により CPLD にテストデザインを書き込み, CPLD 上のレジスタにアクセスした. レジスタの値を自由に読み書きできるか検証した.

検証結果: CPLD への書き込みに成功した.

Figure 68: 新 Sector Logic の IO ポート試験. JTAG で CPLD にプログラムし, CPLD が VME で通信できること, すなわち赤い配線で示した通信が正常に動作することが確認された.

# FPGA への VME 通信

検証目的: FPGA 上のレジスタヘ VME でによる読み書きができるか.

検証方法: FPGA 上のレジスタへ SBC から VME 通信による読み書きを行った.

検証結果: FPGA 上のレジスタに VME 通信による読み書きを成功した. Figure 69 の赤線が確認される配線である.

Figure 69: 新 Sector Logic の IO ポート試験. VME を用いて FPGA のレジスタに読み書きできることを確認する. 図の赤線が確認する配線である.

### BPI への VME 通信

検証目的: BPI 上のアドレスに VME を用いて書き込めるか.

検証方法: BPI上のアドレスを VME を用いて指定し, そのアドレスに VME で UNLOCK, ERASE, WRITE, READ できるか試した.

検証結果 BPI への VME で通信に成功する. Figure 70 の赤線が確認される配線である.

Figure 70: 新 Sector Logic の IO ポート試験. VME を用いて BPI へ読み書きできることを確認する. 図の赤い配線が検証対象である.

# BPI から FPGA への書き込み

検証目的: FPGA リセット時に BPI から FPGA へ書き込みできるか

検証方法: FPGA から BPI ヘテストデザインを書き込み, FPGA をリセットした. FPGA 起動時に BPI から書き込めるか検証した.

検証結果: BPI から FPGA への書き込みに成功した. Figure 71 の赤い配線は本実験で正常に動作すると確認された配線である.

Figure 71: 新 Sector Logic の IO ポート試験. BPI を使って FPGA に書き込むことに成功した. これは図の赤い配線が正しく動作したことを示す.

#### **GTX**

検証目的: 高速シリアル通信 GTX を使った通信ができるか. 特に, 新 Sector Logic は 6.4Gbps の GTX 通信を使う予定なので, そのスループットで不具合がないか.

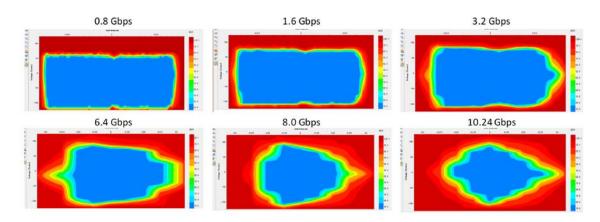

検証方法: 光ケーブルを使ったループバック試験を行い, エラー比を測定する. Xilinx の IBERT [48]を用いる. スループットは 0.8 Gbps, 1.6 Gbps, 3.2 Gbps, 6.4 Gbps, 8.0 Gbps, 10.24 Gbps の 6 通りで試す. まず, GTX の送信ポート, 受信ポートに同一のデータ表を用意し, データを送信ポートから表にしたがって送信する. ループバックさせて受信ポートで受信したデータと受信側のデータ表を照らしあわせ, データ転送が正しく行われたかを調べる.正しく行われたなかったサンプル数を全サンプル数で割り, エラー率を求めた. また, データを受信している間にアイパターンも作成する. アイパターンの計算方法は後述した.

検証結果: 新 Sector Logic 2 は全くうまくいかなかった. 原因を調査すると, GTX の Reference Clock 160.316 MHz を生成する IC Chip に不具合があることが判明した 新 Sector Logic 1 では 0.8Gbps の場合のみエラーが認められた. Bit Error Rate は Table 10 にまとめた. 0.8Gbps の第 3 レーンおよび第 8 レーンにおいてのみ有限な Bit Eroor Rate が観測されているが,他ではエラーが見つからず,Bit Error Rate の上限値を推定している. 観測はいずれのスループットにおいても 10 分間ほど行ったので,スループットの速いものほどデータ量が多く,エラー値が低く見積もられている.

Figure 72: 新 Sector Logic の IO ポート試験. 図の赤線, GTX と FPGA の間の送受信を検査した.

| Line | 0.8 Gbps                | 1.6 Gbps                | 3.2 Gbps                | 6.8 Gbps                | 8.0 Gbps                | 10.24 Gbps              |

|------|-------------------------|-------------------------|-------------------------|-------------------------|-------------------------|-------------------------|

| 0    | $< 2.5 \times 10^{-12}$ | $< 1.0 \times 10^{-12}$ | $< 5.1 \times 10^{-13}$ | $< 2.5 \times 10^{-13}$ | $< 2.3 \times 10^{-13}$ | $< 1.6 \times 10^{-13}$ |

| 1    | $< 2.5 \times 10^{-12}$ | $< 1.0 \times 10^{-12}$ | $< 5.1 \times 10^{-13}$ | $< 2.5 \times 10^{-13}$ | $< 2.3 \times 10^{-13}$ | $< 1.6 \times 10^{-13}$ |

| 2    | $< 2.5 \times 10^{-12}$ | $< 1.0 \times 10^{-12}$ | $< 5.1 \times 10^{-13}$ | $< 2.5 \times 10^{-13}$ | $< 2.3 \times 10^{-13}$ | $< 1.6 \times 10^{-13}$ |

| 3    | $1.4\times10^{-12}$     | $< 1.0 \times 10^{-12}$ | $< 5.1 \times 10^{-13}$ | $< 2.5 \times 10^{-13}$ | $< 2.3 \times 10^{-13}$ | $< 1.6 \times 10^{-13}$ |

| 4    | $< 2.5 \times 10^{-12}$ | $< 1.0 \times 10^{-12}$ | $< 5.1 \times 10^{-13}$ | $< 2.5 \times 10^{-13}$ | $< 2.3 \times 10^{-13}$ | $< 1.6 \times 10^{-13}$ |

| 5    | $< 2.5 \times 10^{-12}$ | $< 1.0 \times 10^{-12}$ | $< 5.1 \times 10^{-13}$ | $< 2.5 \times 10^{-13}$ | $< 2.3 \times 10^{-13}$ | $< 1.6 \times 10^{-13}$ |

| 6    | $< 2.5 \times 10^{-12}$ | $< 1.0 \times 10^{-12}$ | $< 5.1 \times 10^{-13}$ | $< 2.5 \times 10^{-13}$ | $< 2.3 \times 10^{-13}$ | $< 1.6 \times 10^{-13}$ |

| 7    | $< 2.5 \times 10^{-12}$ | $< 1.0 \times 10^{-12}$ | $< 5.1 \times 10^{-13}$ | $< 2.5 \times 10^{-13}$ | $< 2.3 \times 10^{-13}$ | $< 1.6 \times 10^{-13}$ |

| 8    | $1.0\times10^{-12}$     | $< 1.0 \times 10^{-12}$ | $< 5.1 \times 10^{-13}$ | $< 2.5 \times 10^{-13}$ | $< 2.3 \times 10^{-13}$ | $< 1.6 \times 10^{-13}$ |

| 9    | $< 2.5 \times 10^{-12}$ | $< 1.0 \times 10^{-12}$ | $< 5.1 \times 10^{-13}$ | $< 2.5 \times 10^{-13}$ | $< 2.3 \times 10^{-13}$ | $< 1.6 \times 10^{-13}$ |

| 10   | $< 2.5 \times 10^{-12}$ | $< 1.0 \times 10^{-12}$ | $< 5.1 \times 10^{-13}$ | $< 2.5 \times 10^{-13}$ | $< 2.3 \times 10^{-13}$ | $< 1.6 \times 10^{-13}$ |

| 11   | $< 2.5 \times 10^{-12}$ | $< 1.0 \times 10^{-12}$ | $< 5.1 \times 10^{-13}$ | $< 2.5 \times 10^{-13}$ | $< 2.3 \times 10^{-13}$ | $< 1.6 \times 10^{-13}$ |

Table 10: GTX loopback test のエラー率. データ表にしたがって送信されたデータをループ バックさせ, 受信側で得られたデータをデータ表と照らし合わせる. 受信データがデータ表 と異なるサンプル数を全サンプル数で除したのがこの表である. 表中の  $< 2.5 \times 19^{-12}$  のよう に範囲しか示されていないものは, 測定中にエラーが一度も起こらなかったために, エラー率の上限を推定して示している. 0.8Gbps の第 3, 第 4 レーンのみ, 有限の Bit Error Rate が観測されている.

表を見るとエラー率は 10<sup>-12</sup>~10<sup>-13</sup> であるが, 今回はこれで構わない. というのも, ハードウェアにハンダ付けや回路の設計ミスといった不良がないかを確かめるための試験だったからだ. 少なくとも, まともに動作するハードウェアであることは判明した. 今後, このハードウェアをもとに, より安定に動く実践的なハードウェアを開発し, 実際のセットアップで day 単位で稼働し, エラー率を調べる. また, 誤りが発生した場合の対処 (誤り訂正)の開発も検討している.

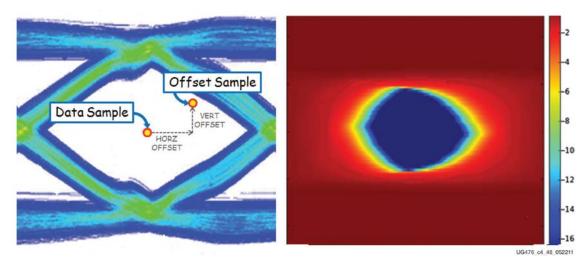

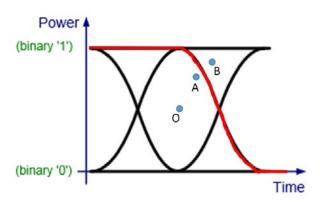

本実験ではアイパターン (Eye Diagram とも呼ばれる) も確認した. アイパターンは, BitError Rate を横軸 Unit Interval (UI), 縦軸を入力電圧としてプロットしたものだである. UI とは, 1/Bit Rate によって定義され, 時間軸を規格化したものである. たとえば 6.4Gbps の場合, UI は UI = 1/Bit rate = 156 ps となる.

具体的に Bit Error Rate の計算手順を紹介する. Bit Error Rate はデータ・サンプルとオフセット・サンプルが不一致のときにカウントされる. データ・サンプルは RX で受け取ったデータから復元されたデータである, オフセット・サンプルはデータ・サンプルの時間軸方

向および電圧方向にオフセットを与えたものである. Figure 73 左図にデータ・サンプルとオフセット・サンプルの具体例を示す.

Figure 73: Bit Error Rate 計算時の Data Sample と Offset Sample (左) とアイパターン(右)の例 [4]

データサンプルとオフセット・サンプルが異なる場合を Bit Error と定義し、総サンプル数に対する Bit Error の割合を Bit Error Rate と呼ぶ. たとえば、Figure 74 において、O 点がデータ・サンプル、A 点および B 点はオフセット・サンプルである. 赤い信号は、O 点および A 点では High であるが、B 点では Low である. したがって、A 点では Bit Error が観測されないが、B 点では Bit Error が観測される. そして総サンプル数に対する Bit Error の割合を Bit Error Rate と呼ぶ. ここで、サンプル点とは、横軸を 64 分割、縦軸を 256 分割した領域 [49]である. 全領域で Bit Error Rate を計算すると、Figure 73 右図のようなカラープロットを描くことができる. これがアイパターンである. 一般的なアイパターンは、データを重ねあわせただけのものが多いが、ここでのアイパターンは Bit Error Rate を二次元に描いた点で統計的である.

Figure 74: データ・サンプル(O 点)とオフセット・サンプル(A 点および B 点) [49]. 赤線で示された信号に対し、O 点と A 点は High だが、B 点は Low である. よって、A 点では Bit Error がカウントされないが、B 点では Bit Error がカウントされる.

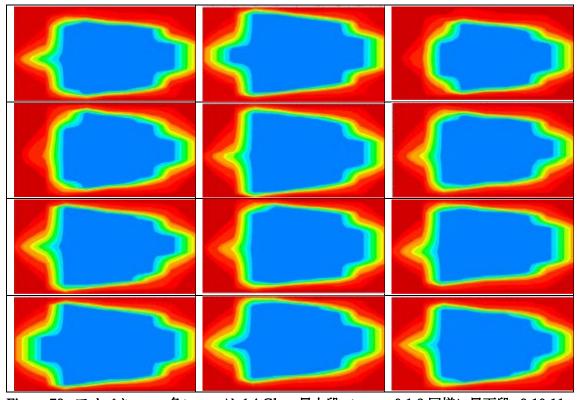

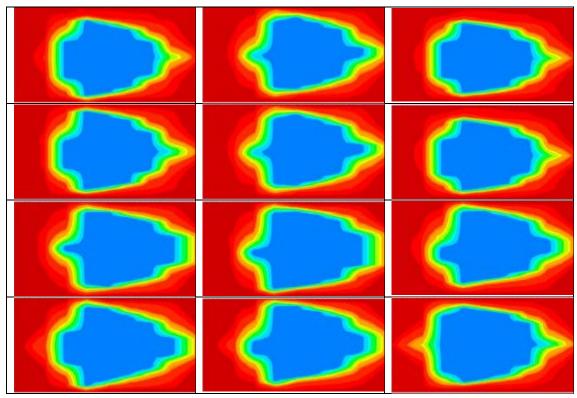

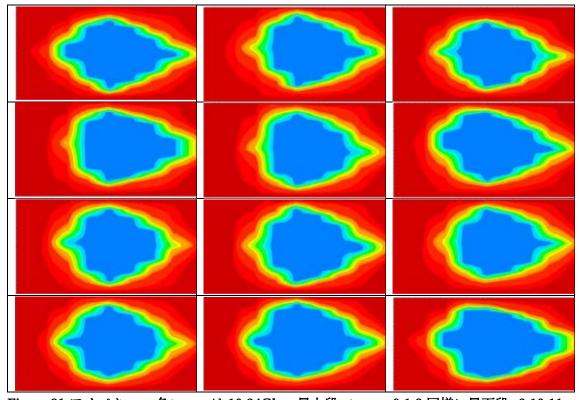

本実験で作成されたアイパターンの一例を Figure 75 に示す.3.2 Gbps 以下での信号の立ち上がり,立ち下がりが垂直になっていることが見てとれる.周波数が高いほど,立ち上がりおよび立ち下がりの時間が無視できなくなるため,高周波数ほど波形がダイヤになり,より周波数を上げていくと青い領域がつぶれていき,信号伝達が信頼できなくなる.アイパターンの目が開いている方がよいと言われるのはこのためである.

Figure 75: 各スループットにおけるアイパターン. 左上から右に 0.8Gbps, 1.6Gbps, 3.2Gbps, 左下から右に 6.4Gbps, 8.0Gbps, 10.24Gbps.

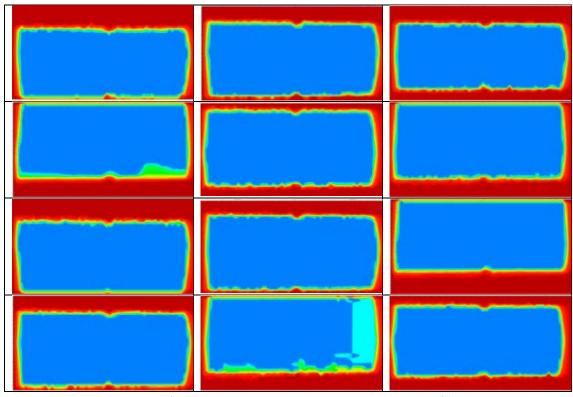

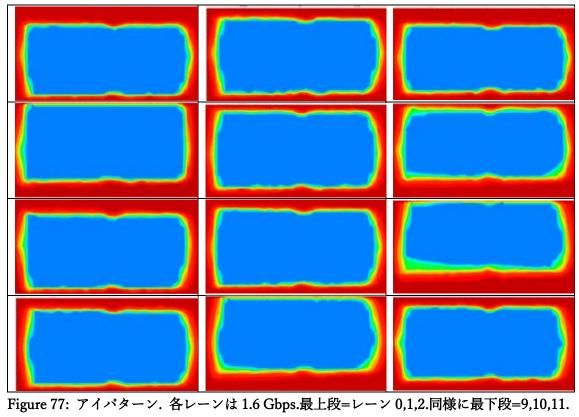

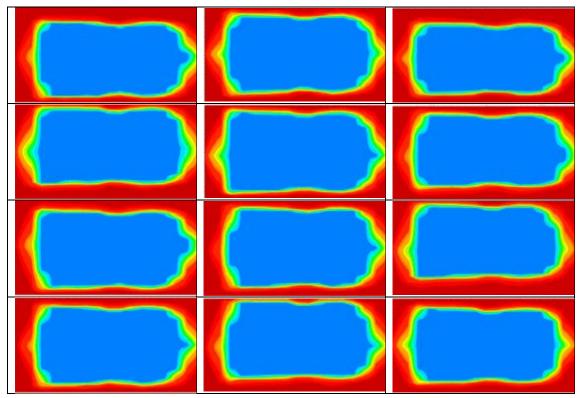

本実験で作成されたアイパターンをラインレート別に Figure 76, Figure 77, Figure 78, Figure 79, Figure 80, Figure 81 にまとめた. 各プロットは, 12 本のライン別に示してある. 一番上の段は左からライン 0, 1, 2. 上から二段目は左からライン 3, 4, 5. 上から三段目は左からライン 6, 7, 8. 最下段は左からライン 9, 10, 11. 横軸は UI であり, 縦軸は電圧を 256 段階に分けた目盛りが使われている.

Figure 76: アイパターン. 各レーンは 0.8 Gbps.最上段=レーン 0,1,2.同様に最下段=9,10,11.

Figure 78: アイパターン. 各レーンは 3.2 Gbps.最上段=レーン 0,1,2.同様に最下段=9,10,11.

Figure 79: アイパターン. 各レーンは 6.4 Gbps.最上段=レーン 0,1,2.同様に最下段=9,10,11.

Figure 80: アイパターン. 各レーンは 8.0 Gbps.最上段=レーン 0,1,2.同様に最下段=9,10,11.

Figure 81:アイパターン.各レーンは 10.24Gbps.最上段=レーン 0,1,2.同様に最下段=9,10,11

アイパターンから読み取れるものについて考える. 周波数依存性については, 低周波数ではアイパターンが長方形だが, 周波数が上がるほどアイパターンはダイヤに近づき, つぶれる. これは周波数が高いほど電圧の立ち上がり, 立ち下がりが無視できなくなるからであり, 一般的な予想通りである. 特に 8.0 Gbps, 10.24 Gbps はアイが小さく, 安定した動作が保障できない.

電圧のオフセットについては、まず最低レート 0.8 Gbps を Figure 76 で確認する. なぜなら、転送速度が遅い方が信号が安定して届くからだ――その予想にも関わらず、Table 10 ではエラーが観測されていた――. ライン 4 は安定しているが、他のものは基準値がずれている. たとえば、Table 10 でエラーが確認されたライン 3、ライン 8 はオフセットが大きく上にずれている. したがって、電圧の低いところで信号を観測しようとするとエラーになる.

6.4 Gbps 以上のアイパターンを見ると, 波形が時間軸方向で対称性を欠いており (図の左右対称性), さらにアイが右にずれていることもわかる.

ちなみに、LHC-ATLAS 実験では GTX ラインレートを 6.4 Gbps で使う予定である. Figure 79: アイパターン. 各レーンは 6.4 Gbps.最上段=レーン 0,1,2.同様に最下段=9,10,11. Figure 79 はラインレート 6.4 Gbps のアイパターンだが、アイパターンは開いており、 Table 10 を見ても Bit Error Rate の上限推定値は  $10 \times ^{-13}$  のオーダーであった.

#### **SiTCP**

検証目的: 新 Sector Logic で導入される SiTCP を使って新 Sector Logic からデータをパソコンに読み出せるか.

検証方法: FPGA にテストデザインをプログラムした. デザインは, FPGA 内部データを作り, SiTCP モジュールとの間に FIFO を置き, SiTCP から出力した. データの確認には SiTCP Utility を用いた. SiTCP Utility は SiTCP 用のソフトウェアツールであり, BBT 社が提供している. 試験したクロックは 150 MHz, 250 MHz, 1 クロックで 8 bit 転送する. つまり, 1.2 Gbps, 2.0 Gbps で転送される.,

検証結果: 1.2 Gbps, 2.0 Gbps でエラーは観測されなかった.

#### Figure 82: SiTCP から得た信号は SiTCP Utility というソフトウェアで受信した.

検証結果: 新 Sector Logic 1, 新 Sector Logic 2 ともに正しく読み出しできた. この実験により, Figure 83 の赤い配線で示すように, FPGA から SiTCP を使ってデータを読みだすことができることを確認した.

Figure 83: 新 Sector Logic の IO ポート試験. 図の赤線, SiTCP と FPGA の間の送受信を検査した.

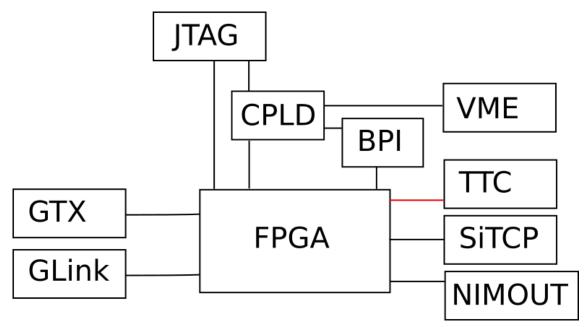

# G-Link

検証目的: G-Link を使って新 Sector Logic がデータを受け取ることができるか

検証方法: PT7 からテスト信号を G-Link で新 Sector Logic が受け取り, それを SiTCP で出力し, パソコンで確認した.

検証結果: GLink は正しく動作した. この実験で, Figure 84 に赤く示した通信が正常に動作することが確認された.

Figure 84: 新 Sector Logic の IO ポート試験. 図の赤い配線, GLink と FPGA の間の通信の検査をした.

#### TTC

TTC については次に示す3つの試験を行った.

# 検証1

検証目的: CLOCK の動作

検証方法: 新 Sector Logic のクロックソースを TTC に変えて新 Sector Logic が正しく動くかどうかを検証した.

検証結果: TTC からクロックを新 Sector Logic に送ることに成功

### 検証2

検証目的: Clonk, L1A, BCR, ECR, TTC\_RESET, TTC\_TEST\_PULS の試験

検証方法: VME を用いて Service Patch Panel から任意の回数の信号を新 Sector Logic に送り、それが新 Sector Logic 上の FPGA に書かれたカウンターの示す値と一致しているかどうかを確かめた.

# 検証3

検証目的: BUSY の検証

検証方法:新 Sector Logic 上の BUSY レジスタの High / Low を VME で切り替えて, 対応するピンの値が正しく切り替わるかどうか、オシロスコープを用いて確認した.

確認した.

検証結果: BUSY は正しく動作していた. Figure 85 にこの試験で検査され, 正常に動作することが確認された配線を赤く示した.

Figure 85: 新 Sector Logic の IO ポート試験. 図の赤線, FPGA と TTC の間の通信を検査した.

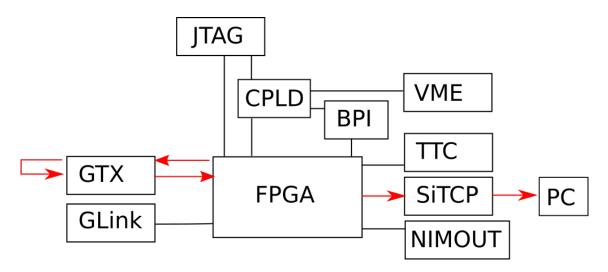

# 8.2. 新 Sector Logic - GTX から SiTCP ま

# での貫徹試験

新 Sector Logic が実際に NSW からデータを受け取り、FPGA 内部の論理回路を通り、SiTCP からデータが読み出せるかの試験を行った。本研究のメインは、この新 Sector Logic 読み出しプログラムを作製したことにある。

新 Sector Logic のデータフローは,次のようになるよう設計されている. まず,全体の流れを把握するためにも Figure 86 を参照していただきたい. FPGA 内部で生成した信号をGTX でループバックさせ,受け取った信号を FPGA で処理し,SiTCP で読み出し,PC で期待通りの処理がされて読み出されていることを確認した. FPGA 内部の処理も含め,順を追って詳述すると次のような手続きになる.

1. FPGA の内部で作成された信号を GTX の TX から送信し、ループバック経路 (後

- 述) を通り, 新 Sector Logic へ戻る.

- 2. GTX からの信号は 16bit, 320.632MHz で送られてくる. これを TTC クロックに合わせるため, FIFO に溜めて, 128bit ごとに 40.079MHz で読みだす.

- 3. 全  $12 \, \nu \nu \times 128 \, \text{bit} = 1536 \, \text{bit}$  のデータは、G-Link データやコインシデンスデータ と連結され、L1 Buffer に格納される。L1 Buffer は  $2048 \, \text{bit} \times 128 \, \text{words}$  のメモリでできている。G-Link とコインシデンスデータは FPGA 内部で作成した。また、L1Buffer の書き込みポインタ、読み出しポインタの差は後で適宜調整できるようになっている。L1A 信号を受信すると、SLID、L1ID や BCID がゼロサプレス回路内の FIFO に格納される。

- 4. L1Buffer に入ったデータは、128 クロック後、L1A 信号を受信したらデランダマイザに渡され、L1A 信号を受信しなければ破棄される.

- 5. デランダマイザに入ったデータは, FIFO によって 2048bit から多段的に 16bit まで 絞られる.

- 6. デランダマイザを出た 16bit のデータは, ゼロサプレス回路に送られる. ゼロサプレス内部では, 16bit 内に 1 が 1bit でもあるものがいくつあるか, 3 バンチ分数える. これが後段の ROD にデータを引き渡す際のデータサイズになる. データサイズカウント中, 1 があるかチェックされた 16bit は FIFO に格納され, データサイズのカウントが終わるのを待機する.

- 7. 2048×3/16=384 クロックかけて 3 バンチ分のデータをチェックし終わると, データサイズのカウントが終わると, データサイズも専用の FIFO に格納される. そして, データ読み出し作業に入る. 読み出されるデータはフォーマットにしたがって, SLID, L1ID, BCID そしてデータサイズから受け取り, 16bit のデータも FIFO から順に取り出される.

- 8. SiTCP に FPGA から送るデータのサイズは 8bit である必要があるので, ゼロサプレスから 32bit で出てきたデータは FIFO を通して 8bit ごとに SiTCP へ送られる.

- 9. SiTCP から出力されたデータをパソコンで確認する.

Figure 86: 読み出しの貫徹試験におけるデータの流れ. FPGA 内部で生成された信号を GTX でループバックさせ, 受け取った信号を FPGA 内部のロジック (L1Buffer やゼロサプレスなど) を通した後, SiTCP で読み出し, PC でデータを確認した.

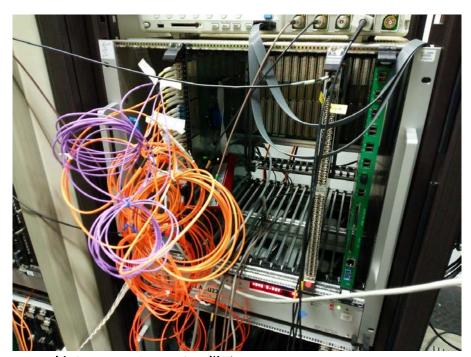

実際に試験して、この通り機能していることを確かめた。Figure 87 にテスト時の写真を載せた. 写真の左側が新 Sector Logic である. GTX ループバックのため 12 本のオレンジ色もしくは紫色の光ケーブルがつながっている.

L1A 信号は FPGA 内部で 100kHz のパルス波を生成して代えた.

Figure 87: 新 Sector Logic テストの様子

GTX のループバック経路については Figure 60 を参照すると, 四通りあることがわかる. さらに, Figure 87 のように光ケーブルを用いて信号を外に出すループバック経路もある. 1 番目の最短経路である Near-End PCS Loopback では成功したが, 他の 3 通りの経路と光ケーブルでは成功しなかった. しかし, IO ポート試験時に光ケーブルを用いたループバック試験に成功していた. 今後, この問題の原因を調査していく予定である.

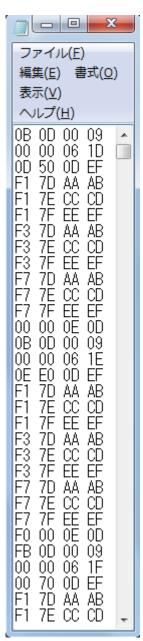

Near-End PCS Loopback によって経路受信したデータは Figure 88 に載せた. 試験的に GTX からループバックさせたデータは期待どおりに得られた. データは 10 秒以上送信され 続けた. FIFO が full になった場合に受信した L1A 信号,および 3 バンチ以内で連続して受信した L1A 信号は無視するよう設計されている.

Figure 88: 新 Sector Logic 出力データ. フォーマット通りにデータが出ていることが確かめられた. 一行あたり 32bit 表示している. SiTCP によって, 新 Sector Logic から得られたデータを, このように PC で簡単に確認することができた.

# 9.まとめ

CERN の LHC は 2019 年に二度目のアップグレード作業 (Long Shutdown 2, LS2) が行われる予定である. 本研究では、ATLAS 実験で用いられるミューオン検出器の一部 Sector Logic はミューオンの横運動量を測定し、トリガーを発行するハードウェアであった. 現在用いられている Sector Logic は目的の高運動量ミューオンではなてもトリガーを発行してしまうという問題を抱えている. そこで、LS2 の間に新たな検出器である New Small Wheel (NSW)を導入し、そのようなフェイクを削ぎ落とす予定である. それにともない、Sector Logic は NSW からのデータも受け取るように改良する必要がある. 本文で確認した通り、Sector Logic の変更点は、次の三点であった. 1. Sector Logic に NSW とデータ通信するための GTX 通信モジュールを搭載させた. 2. Sector Logic の読み出しロジックを新たに FPGA で構築した. 3. Sector Logic からのデータは SiTCP という TCP 通信によって PC に読みだすようにアップグレードする予定である.

本論文では、新 Sector Logic のプロトタイプを作成し、その設計や回路に問題がないことを確かめた。特に、GTX 通信の性能を評価したところ、電圧のオフセットも時間軸のオフセットもずれていることを確認した。ゆえに、0.8 Gbps でもエラーが生じていた。6.4 Gbps はアイが安定しており、エラーもなかった。また、8.0 Gbps 以上の高周波ではアイも小さくなっていることを確認した。FPGA 上の回路や SiTCP 通信も成功した。

今後は、今回のプロトタイプをもとに、より安定に動くファームウェアを開発し、実際の ATLAS の実験と同じ環境で長時間の試験をする予定である。その後、トリガー機能も新 Sector Logic 上の FPGA 上に構築して、読み出しとトリガーが共に問題なく動作することを確かめる.

# 10. 引用文献

- [1] "CERN | Accelerating science," [オンライン]. Available: http://home.cern/.

- [2] "The Large Hadron Collider | CERN," [オンライン]. Available: http://home.cern/topics/large-hadron-collider.

- [3] "ATLAS Experiment," [オンライン]. Available: http://atlas.ch/.

- [4] "7 Series FPGAs GTX/GTH Transceivers User Guide," [オンライン]. Available: http://www.xilinx.com/support/documentation/user\_guides/ug476\_7Series\_Transceivers.pdf.

- [5] "SiTCP ホーム," [オンライン]. Available: http://research.kek.jp/people/uchida/technologies/SiTCP/.

- [6] "Overall view of LHC experiments. CERN Document Server," [オンライン]. Available: https://cds.cern.ch/record/841555?ln=ja.

- [7] CERN, "LHC Design Report," 2004.

- [8] J. Varela, "Timing and Synchronization in the LHC Experiments," Presented at the 6th Workshop on Electronics for LHC Experiments, Krakóv, 2000.

- [9] J. Haffner, "The CERN accelerator complex. Complexe des accelerateurs de CERN," Oct 2013.

- [10] W. H. E. M. T. P. G. Arduini, "Alternative bunch filling scheme for LHC," Werner Herr, 2007.

- [11] [オンライン].

Available: http://www.lhc-closer.es/taking\_a\_closer\_look\_at\_lhc/0.beam\_lifetime.

- [12] "ATLAS Experiment Photos," [オンライン]. Available: http://www.atlas.ch/photos/full-detector-photos.html.

- [13] "CMS | CERN," [オンライン]. Available: http://home.cern/about/experiments/cms.

- [14] "The ALICE detector CERN Document Server," [オンライン]. Available: https://cds.cern.ch/record/1436153?ln=ja.

- [15] "Collaborations on the starting blocks CERN Document Server," [オンライン]. Available: http://cds.cern.ch/record/1124112.

- [16] "ATLAS Experiment | ATLAS and the Higgs: Resources," ATLAS Experiment, [オンライン]. Available: http://www.atlas.ch/HiggsResources/.

- [17] "Review of single vector boson production in pp collisions at  $\sqrt{s} = 7$ \$ TeV INSPIRE-HEP," [オンライン]. Available: http://inspirehep.net/record/1294662/plots.

- [18] "Track Reconstruction Performance of the ATLAS Inner Detector at  $\sqrt{s}$ = 13 TeV," [オンライン]. Available: https://atlas.web.cern.ch/Atlas/GROUPS/PHYSICS/PUBNOTES/ATL-

- [19] "ATLAS Experiment Photos," [オンライン]. Available: http://www.atlas.ch/photos/calorimeters-lar-barrel.html.

- [20] "ATLAS Experiment Photos," [オンライン]. Available: http://www.atlas.ch/photos/muons-combined.html.

PHYS-PUB-2015-018/.

- [21] ATLAS, "Muon Spectrometer Technical Design Report," 1999.

- [22] ATLAS, "The ATLAS Experiment at the CERN Large Hadron Collider," 2008.

- [23] Goodson, Jeremiah Jet (SUNY, Stony Brook); McCarthy, Robert (dir.) (SUNY, Stony Brook), "Search for Supersymmetry in States with Large Missing Transverse Momentum and Three Leptons including a Z-Boson," 2012.

- [24] ATLAS, "Technical Design Report for the Phase-I Upgrade of the ATLAS TDAQ System," 2013.

- [25] "ミュー粒子トリガー検出器 PukiWiki," [オンライン]. Available: http://www.hepl.phys.nagoya-u.ac.jp/public/www/Intro/atlas\_v2/index.php?%A5%DF%A5%E5%A1%BC%CE%B3%BB%D2%A5%C8%A5%EA%A5%AC%A1%BC%B8%A1%BD%D0%B4%EF.

- [26] E. A. J. A. A. A. a. a. G Aad, "The ATLAS Experiment at the CERN Large Hadron Collider," 2008.

- [27] "ATLAS Experiment Photos," [オンライン]. Available: http://www.atlas.ch/photos/muons-tgc.html.

- [28] 早川俊(神戸大学大学院,), "LHC シングルビームを用いた ATLAS 実験前後方ミューオントリガーシステムの性," 2007.

- [29] 平山翔(東京大学大学院), "ATLAS 実験前後方レベル 1 ミューオントリガーシステムの構築と検証," 2009.

- [30] 鈴木雄太, "Look Up Table 改良による ATLAS レベル 1 ミューオントリガーの性能 向上の研," 2012.

- [31] 桑原隆志, "ATLAS 前後方ミューオントリガーシステムの構築," 2007.

- [32] 大谷育生, "ATLAS ミューオントリガーシステムのアップグレードに向けたギガビ

- ット通信を用いたデータ収集系の検証及び読み出しプロトタイプの開発,"2013.

- [33] 門坂拓哉, "ATLAS 前後方ミューオントリガーシステム Sector Logic 及びオンラインソフト," 2008.

- [34] 平山翔, "ATLAS 実験前後方部レベル 1 ミューオントリガーシステムの構築と検証," 2009.

- [35] A. D. R. H. a. G. A. W Buttinger, "Performance of the ATLAS Level-1 Trigger System in 2011/12. Technical Report ATL-COM-DAQ-2012-033.," CERN, Geneva, May, 2012.

- [36] Y. Suzuki, "Upgrade of the ATLAS Level-1 Muon Trigger for the High Luminosity LHC," 2013.

- [37] B. S. f. t. A. M. Collaboratoin, "The New Small Wheel Upgrade Project of the ATLAS Experiment," *Nuclear Physics B Proceedings Supplement 00 (2014) 1-6,* 2014.

- [38] 徳永孝之, "LHC-ATLAS 実験 RUN3 に向けた新しいミューオントリガー装置の," 2015.

- [39] F. Bordry, "LS1 Status Report 116th LHCC," 2014/12/4.

- [40] 細山 謙二(高エネルギー加速器研究機構 加速器研究施設), "超伝導クラブ空洞," 低温工学 Vol.43 No.4, 2008.

- [41] "KEK:トピックス(クラブ空洞で新記録)," [オンライン]. Available: http://www2.kek.jp/ja/news/topics/2009/KEKBluminosity2.html.

- [42] T. Kawamoto, S. Vlachos, L. Pontecorvo, J. Dubbert, G. Mikenberg, P. Iengo, C. Dallapiccola, C. Amelung, L. Levinson, R. Richter, "New Small Wheel Technical Design Report," CERN. Geneva, 2013.

- [43] T. e. al., "A spark-resistant- bulk-Micromegas chamber for high-rate applications," *Nucl. Instr. Meth.*, 第 巻 640, p. 110, 2011.

- [44] 佐々木修, "Muon Endcap Trigger in Phase I New Sector Logic Board," 2013.

- [45] Xilinx, "Kintex-7 FPGAs Data Sheet:DC and AC Switching Characteristics," 24 11 2015. [オンライン]. Available: http://www.xilinx.com/support/documentation/data\_sheets/ds182\_Kintex\_7\_Data\_ Sheet.pdf.

- [46] Tomohisa Uchida(KEK), "SiTCP 説明書," [オンライン].

Available:

http://research.kek.jp/people/uchida/technologies/SiTCP/doc/SiTCP.pdf.

- [47] "プラットフォーム ケーブル USB II," [オンライン].

- Available: http://japan.xilinx.com/products/boards-and-kits/hw-usb-ii-g.html.

- [48] Xilinx, "LogiCORE IP Integrated Bit Error Ratio Tester (IBERT) for 7 Series GTX Transceivers v3.0," [オンライン]. Available: http://www.xilinx.com/support/documentation/ip\_documentation/ibert\_7series\_gtx/v3\_0/pg132-ibert-7series-gtx.pdf.

- [49] 嶺岸優司, "ATLAS 実験液体アルゴンカロリメータのアップグレード," 2015.

- [50] "CERN Document Server," [オンライン]. Available: https://cds.cern.ch/.

- [51] "LHCb Large Hadron Collider beauty experiment," [オンライン]. Available: https://lhcb-public.web.cern.ch/lhcb-public/en/Physics/Physics-en.html.

# 謝辞

本研究は様々な方にお世話になりました. 指導教官の坂本宏教授, 高エネルギー加速器研究機構の佐々木修教授には大変お世話になりました. 総合研究大学院大学の鈴木翔太さん, 京都大学の赤塚駿一さん, 神戸大学の谷岡凌さんにもお世話になりました. どうもありがとうございます. また, 各種手続きなど毎日お世話になった事務の方々, どうもありがとうございます.

東京大学大学院理学系研究科物理学専攻 素粒子物理国際研究センター 坂本研究室 渡邊直樹