# 修士学位論文

ATLAS実験のための新しいミューオントリガー装置の研究開発

東京大学大学院理学系研究科 物理学専攻素粒子物理国際研究センター 小林研究室

加藤千曲

2014年8月4日

#### 概要

ATLAS 実験は LHC 加速器を用いて新しい物理を探索する. 2012 年に発見された Higgs 粒子の精密測定や超対称性粒子の探索を行う. LHC は 2012 年までは重心系エネルギー 8 TeV, ルミノシティ  $0.6\times10^{34}{\rm cm}^{-2}{\rm s}^{-1}$  で稼働した. 今後は段階的にアップグレードを行い 2019 年からは 14 TeV,  $2\times10^{34}{\rm cm}^{-2}{\rm s}^{-1}$  で稼働する. ATLAS は 14 TeV,  $3\times10^{34}{\rm cm}^{-2}{\rm s}^{-1}$  でも対応出来るように準備する. しかしこのとき ATLAS の第一段階ミューオントリガーは要求 20 kHz に対し約 60 kHz になる. そこで ATLAS は新しいミューオン検出器を導入する. これによりトリガーの精度を上げ, 現状約 98% の間違って判定されるトリガーを約 66% 落とす.

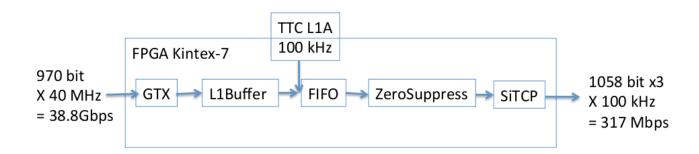

本研究ではこの新しいミューオン検出器のためのトリガー装置の研究開発を行った. 試作機を用いて FPGA 読み出し開発, 基板修正, 性能評価を進めた. その結果以下が判明した. 入力は要求約 39 Gbps に対し高速シリアル通信 GTX で約 80 Gbps 可能である. メモリは要求約 2000 kbit に対し FPGA の Block RAM で 16020 kbit 可能である. 出力は要求約 317 Mbps に対し FPGA TCP 処理技術 SiTCP で 891 Mbps 可能であり, 市販の Switching Hub で収集できる.

# 目次

| 第1章 | はじめに                                                                                            | 4                                |

|-----|-------------------------------------------------------------------------------------------------|----------------------------------|

| 1.1 | LHC 加速器                                                                                         | 4                                |

| 1.2 | ATLAS 検出器                                                                                       | 5                                |

|     | 1.2.1 全体像                                                                                       | 5                                |

|     | 1.2.2 Muon Spectrometer                                                                         | 7                                |

|     | 1.2.3 磁石                                                                                        | 9                                |

| 1.3 | ATLAS のトリガーと DAQ                                                                                | 10                               |

|     | 1.3.1 L1 トリガー                                                                                   | 10                               |

|     | 1.3.2 L2 トリガー                                                                                   | 12                               |

|     | 1.3.3 EF                                                                                        | 12                               |

| 1.4 | LHC のアップグレード                                                                                    | 12                               |

|     | 1.4.1 Long Shutdown 1                                                                           | 13                               |

|     | 1.4.2 Long Shutdown 2                                                                           | 13                               |

|     | 1.4.3 Long Shutdown 3                                                                           | 13                               |

| 1.5 | ATLAS のアップグレード                                                                                  | 14                               |

|     | 1.5.1 Phase-0                                                                                   | 14                               |

|     | 1.5.2 Phase-1                                                                                   | 14                               |

|     | 1.5.3 Phase-2                                                                                   | 15                               |

| 第2章 | L1 Endcap ミューオントリガー                                                                             | 16                               |

| 2.1 | TGC                                                                                             | 16                               |

|     | 2.1.1 TGC の動作原理                                                                                 | 16                               |

|     | 2.1.2 TGC の種類                                                                                   | 16                               |

|     | 2.1.3 TGC の配置                                                                                   | 17                               |

|     | 2.1.4 TGC のセクター                                                                                 | 17                               |

| 2.2 | L1 Endcap ミューオントリガー 概要                                                                          | 18                               |

|     | 2.2.1 p <sub>T</sub> 判定                                                                         | 10                               |

|     | 2.2.1 P1 13/C                                                                                   | 18                               |

|     | 2.2.2 段階的なコインシデンス                                                                               | 18<br>18                         |

|     | * -                                                                                             | 18                               |

| 2.3 | 2.2.2 段階的なコインシデンス                                                                               | 18<br>20                         |

| 2.3 | 2.2.2 段階的なコインシデンス                                                                               | 18<br>20                         |

| 2.3 | 2.2.2 段階的なコインシデンス                                                                               | 18<br>20<br>21                   |

| 2.3 | 2.2.2 段階的なコインシデンス          2.2.3 CW          L1 Endcap ミューオントリガー 電子装置          2.3.1 トリガーの流れと配置 | 18<br>20<br>21<br>21             |

| 2.3 | 2.2.2段階的なコインシデンス2.2.3CWL1 Endcap ミューオントリガー 電子装置2.3.1トリガーの流れと配置2.3.2フロントエンド                      | 18<br>20<br>21<br>21<br>21       |

| 2.3 | 2.2.2段階的なコインシデンス2.2.3CWL1 Endcap ミューオントリガー 電子装置2.3.1トリガーの流れと配置2.3.2フロントエンド2.3.3HSC クレート         | 18<br>20<br>21<br>21<br>21<br>24 |

| 2.4 | L1 Endcap ミューオントリガー のアップグレード | 27        |

|-----|------------------------------|-----------|

|     | 2.4.1 Phase-0                | 28        |

|     | 2.4.2 Phase-1                | 28        |

|     | 2.4.3 Phase-2                | 29        |

| 第3章 | 新 SL                         | 30        |

|     | •                            |           |

| 3.1 |                              | 30        |

| 3.2 |                              | 30        |

|     |                              | 30        |

|     |                              | 32        |

| 2.2 |                              | 32        |

| 3.3 | 新 SL 要求性能                    | 33        |

| 第4章 | PT7                          | 34        |

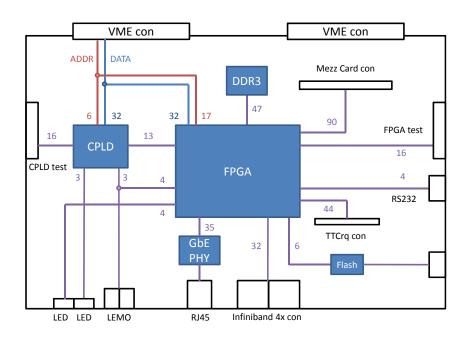

| 4.1 | PT7 構成                       | 34        |

|     | 4.1.1 FPGA                   | 34        |

|     | 4.1.2 CPLD                   | 34        |

|     | 4.1.3 Ethernet PHY           | 34        |

|     | 4.1.4 DDR3 SDRAM             | 36        |

|     |                              | 36        |

| 4.2 | PT7 入出力                      | 36        |

|     |                              | 36        |

|     |                              | 37        |

|     |                              | 37        |

|     |                              | 37        |

|     | •                            | 37        |

| 4.3 |                              | 38        |

|     |                              | 39        |

|     |                              | 39        |

|     |                              | 40        |

|     |                              |           |

| -   |                              | <b>43</b> |

| 5.1 |                              | 43        |

| 5.2 |                              | 43        |

|     |                              | 44        |

|     |                              | 44        |

|     |                              | 45        |

| 5.3 |                              | 45        |

|     |                              | 46        |

|     |                              | 46        |

|     |                              | 46        |

| 5.4 |                              | 48        |

|     | 5.4.1 PT7 CTY 接続試驗 内交        | 1Ω        |

|                         | 5.4.2 PT7 GTX 接続試験 結果                           | 48       |

|-------------------------|-------------------------------------------------|----------|

|                         | 5.4.3 PT7 GTX 接続試験 結論                           | 49       |

| 5.5                     | Kintex-7 評価ボード KC705 を用いた GTX SMA 波形確認          | 50       |

|                         | 5.5.1 Kintex-7 評価ボード KC705 を用いた GTX SMA 波形確認 内容 | 50       |

|                         | 5.5.2 Kintex-7 評価ボード KC705 を用いた GTX SMA 波形確認 結果 | 50       |

|                         | 5.5.3 Kintex-7 評価ボード KC705 を用いた GTX SMA 波形確認 結論 | 51       |

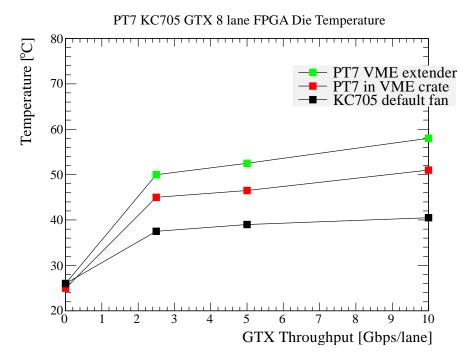

| 5.6                     | PT7 GTX FPGA 温度測定                               | 52       |

|                         | 5.6.1 PT7 GTX FPGA 温度測定 内容                      | 52       |

|                         | 5.6.2 PT7 GTX FPGA 温度測定 結果                      | 52       |

|                         | 5.6.3 PT7 GTX FPGA 温度測定 結論                      | 52       |

| <b>⇔</b> 0 <del>≠</del> | ΦC OT ENEL                                      | - 1      |

| -                       | 新SL 設計                                          | 54       |

| 6.1                     | メモリ資源の選定                                        | 54       |

|                         | 6.1.1 資源と型                                      | 54       |

|                         | 6.1.2 実装                                        | 55       |

| 6.9                     | 6.1.3 busy 確率                                   | 55<br>56 |

| 6.2                     |                                                 |          |

|                         | · / / / / · · · · · · · · · · · · · ·           | 56<br>56 |

|                         |                                                 | 56       |

|                         | 6.2.3 DDR3                                      | 56       |

|                         | 6.2.4 电// 电// 电// 电// 电// 电// 电// 中// 一         | 58       |

| 6.3                     | 新 SL FPGA 設計                                    | 60       |

| 0.5                     | 6.3.1 Zero Suppress                             | 60       |

|                         | 6.3.2 読み出し形式                                    | 60       |

|                         | 6.3.3 収集系                                       | 61       |

|                         | 6.3.4 Burst 事象                                  | 61       |

|                         | 6.3.5 Burst Stopper                             | 62       |

|                         | 0.0.0 Durst propper                             | UΖ       |

| 第7章                     | まとめ                                             | 63       |

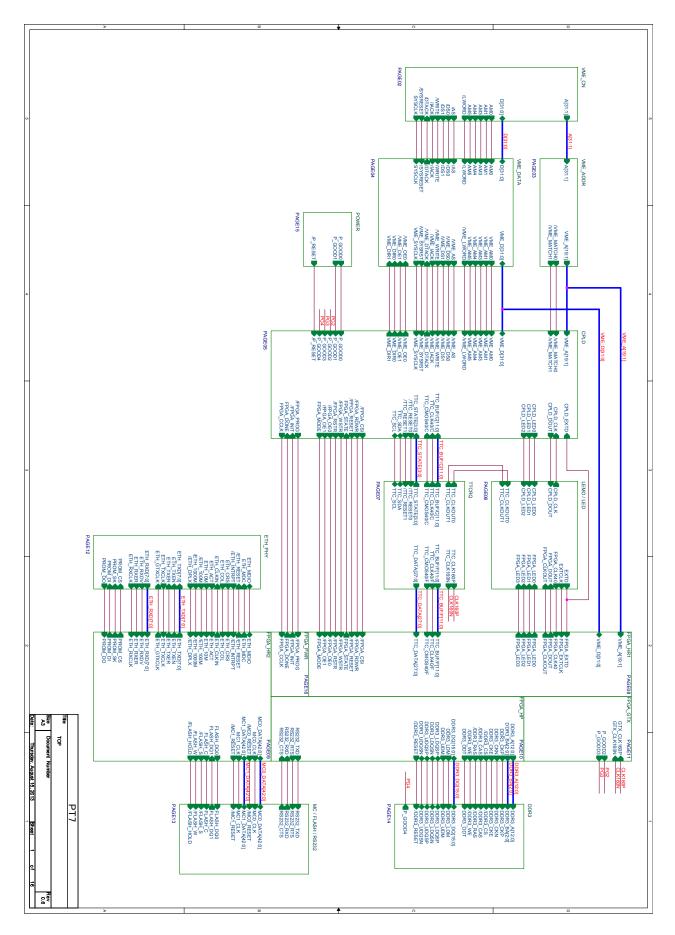

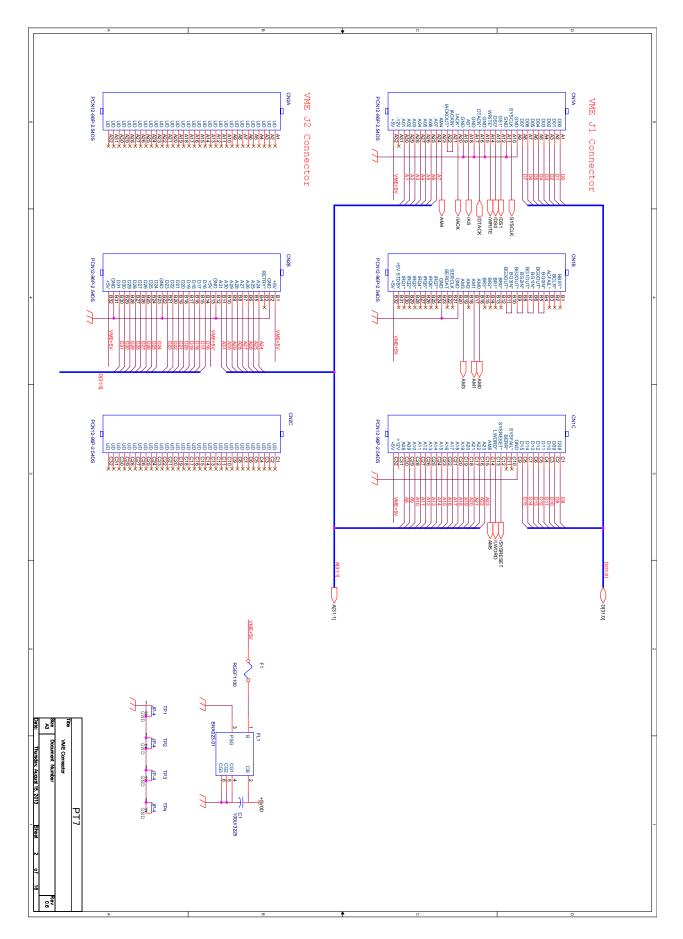

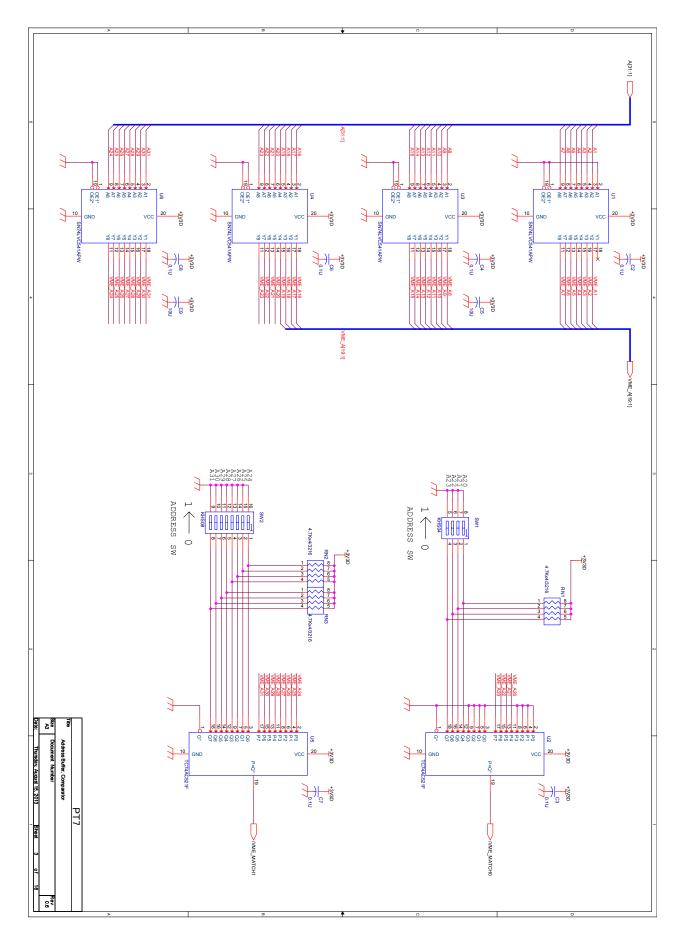

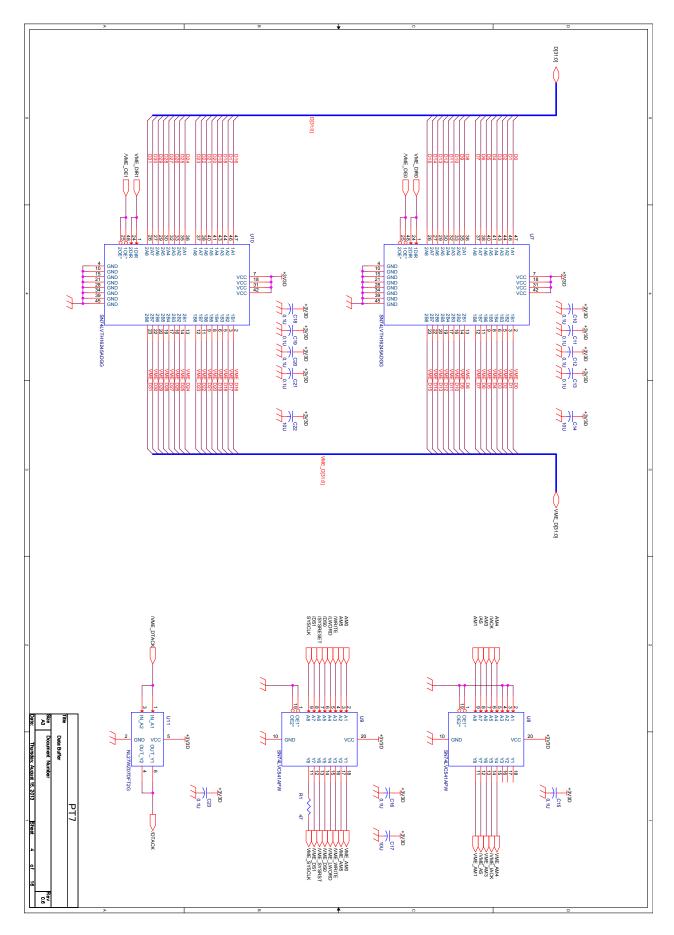

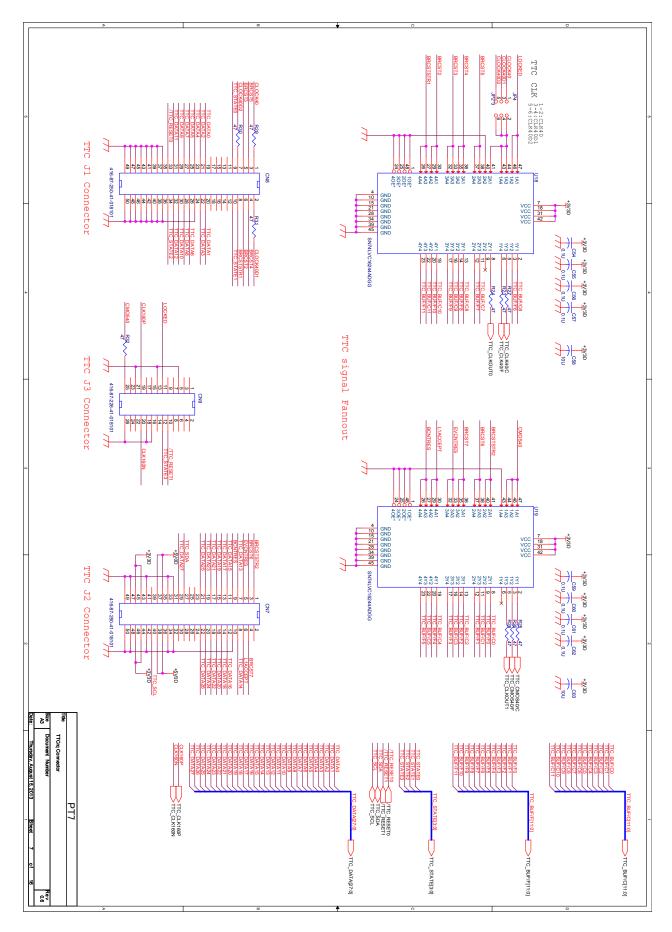

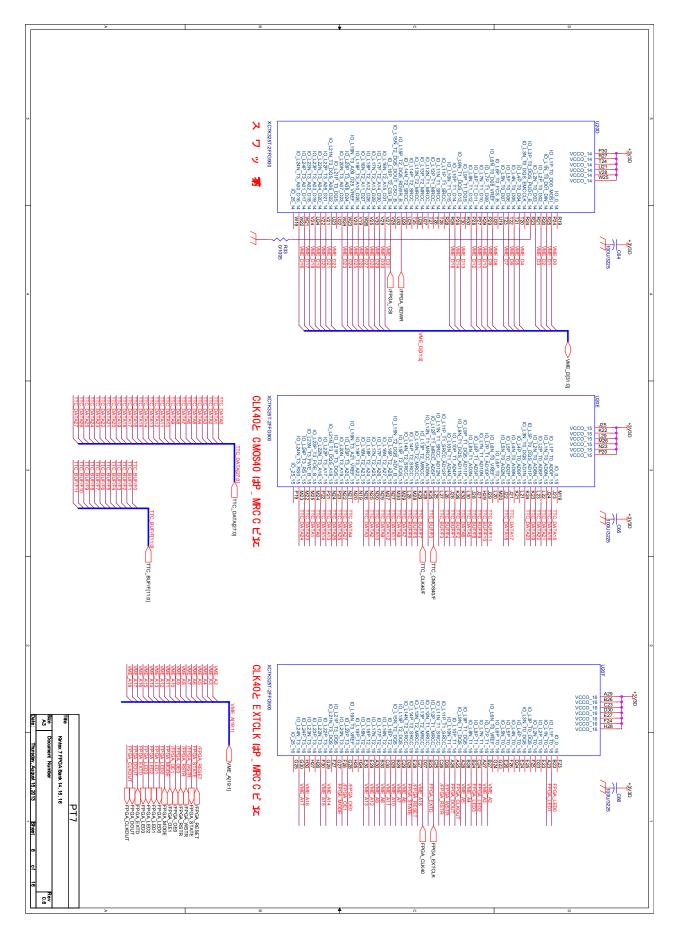

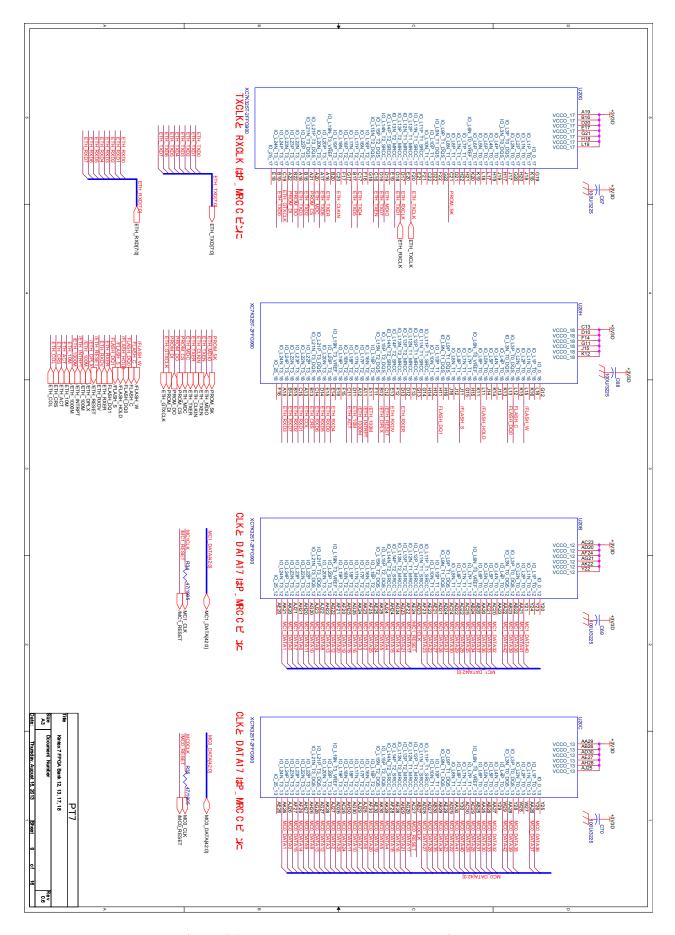

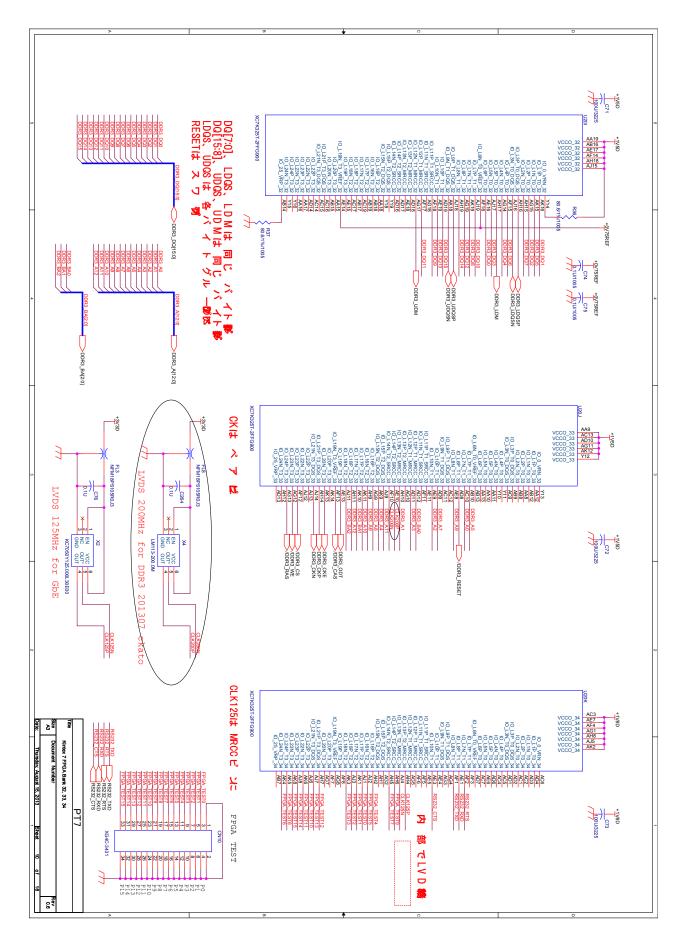

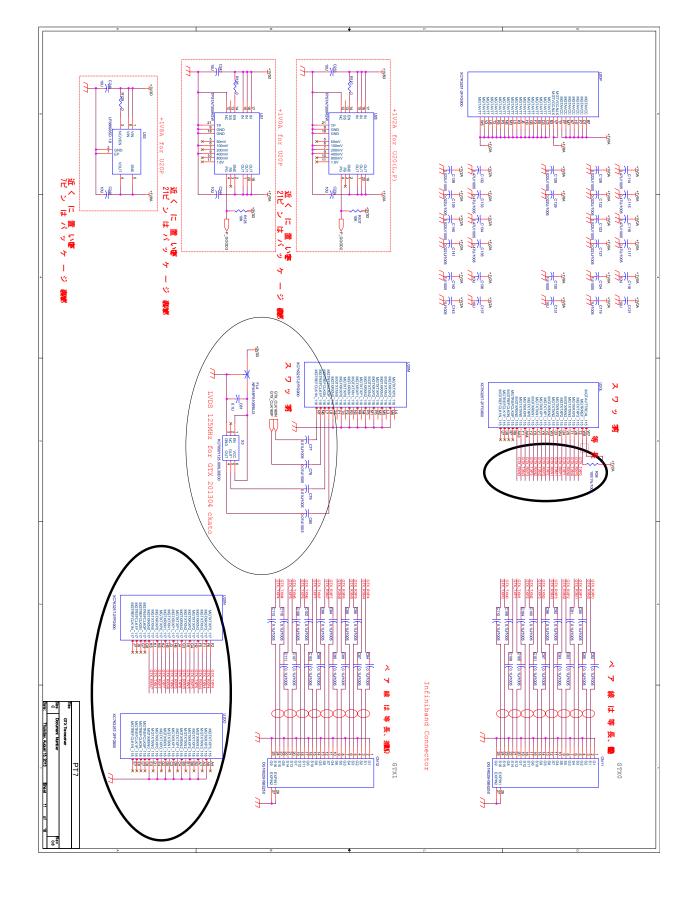

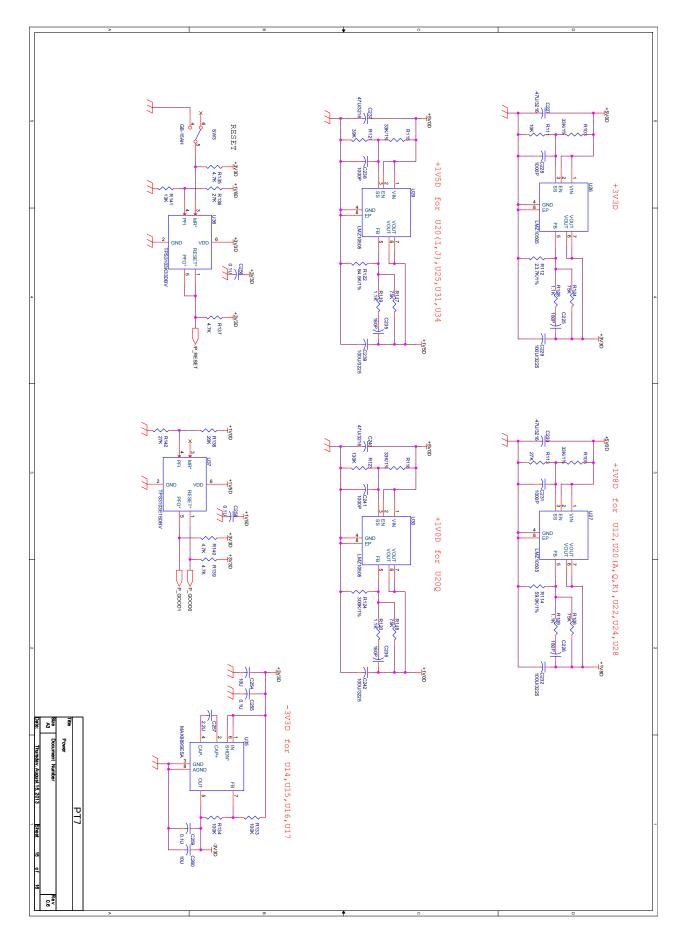

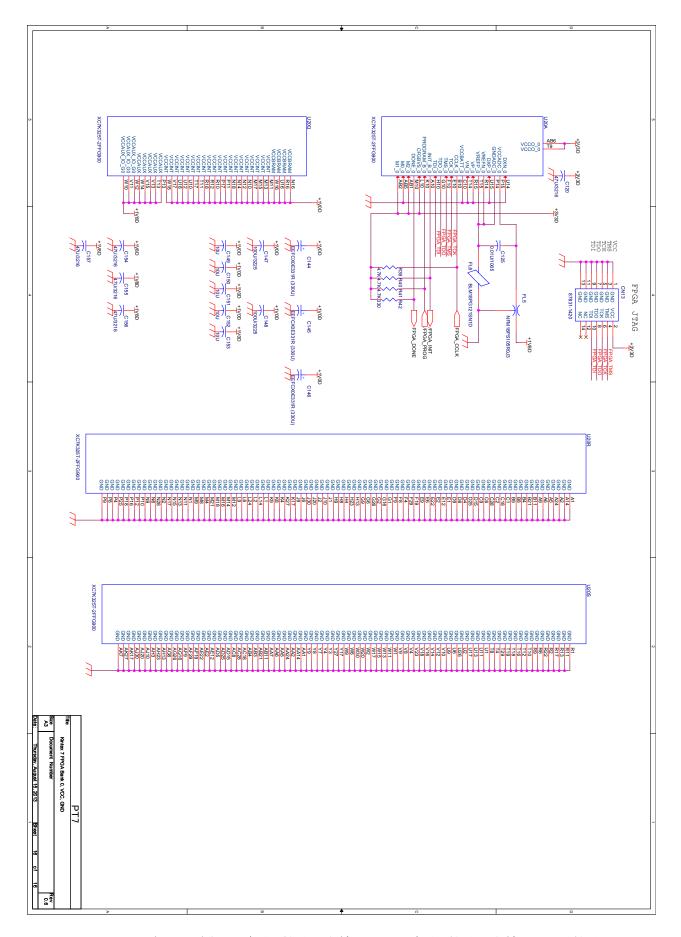

| 付録A                     | PT7v2 回路図                                       | 68       |

# 第1章 はじめに

ATLAS 実験は LHC 陽子-陽子衝突型加速器を用いて新しい物理を探索する. 2012 年には質量約 125 GeV の新粒子が発見された. 2013 年にはこの粒子が標準理論の予言する Higgs 粒子であることが確定した. 今後はこの Higgs 粒子の精密測定や超対称性粒子の探索などを行う. しかし例えば Higgs 粒子の生成確率は陽子陽子衝突 10<sup>9</sup> 事象に 1 事象程度と非常に希である. そのため検出器のデータ取得の際の事象選別, トリガーが重要になる.

LHC は 2012 年までは重心系エネルギー 8 TeV, ルミノシティ  $0.6 \times 10^{34} {\rm cm}^{-2} {\rm s}^{-1}$  で稼働した. 今後は段階的にアップグレードを行い 2019 年からは 14 TeV,  $2 \times 10^{34} {\rm cm}^{-2} {\rm s}^{-1}$  で稼働する. ATLAS は 14 TeV,  $3 \times 10^{34} {\rm cm}^{-2} {\rm s}^{-1}$  でも対応出来るように準備する. しかしこのとき ATLAS の第一段階ミューオントリガーは約 60 kHz になる. データ取得からの要求は 20 kHz である. そこで ATLAS は新しいミューオン検出器を導入する. これによりトリガーの精度を上げ, 現状約 98% の間違って判定されるトリガーを約 66% 落とす.

本研究ではこの新しいミューオン検出器のためのトリガー装置の研究開発を行った. 試作機を 用いた性能評価などを進めた. 本章ではその研究背景を述べる.

# 1.1 LHC 加速器

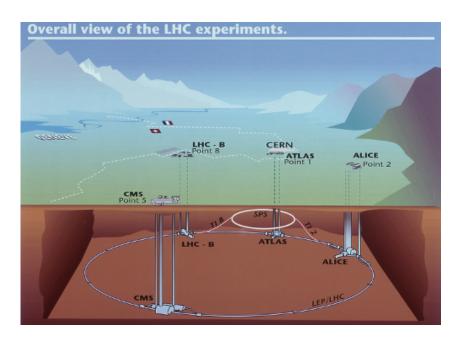

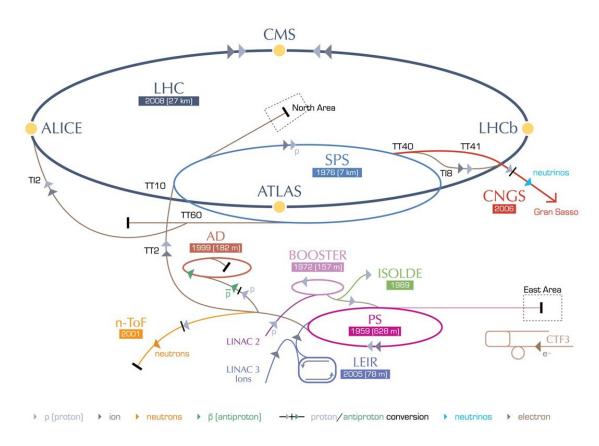

LHC(Large Hadron Collider) は陽子-陽子衝突型円形加速器である。スイス・ジュネーブ郊外のCERN 研究所, 地下約 100 m にある。2012 年の重心系エネルギーは 8 TeV, 最大瞬間ルミノシティは 7.7×10<sup>33</sup>cm<sup>-2</sup>s<sup>-1</sup>である。図 1.1に LHC の外観図を示す。表 1.1に LHC の設計値を示す。陽子の加速方法を述べる。まず陽子イオン源から出た陽子イオンを線形加速器 Linac2 で加速する。次に シンクロトロン PS Booster で 1.4 GeV まで加速する。Proton Synchrotron (PS), Super Proton Synchrotron (SPS) で 450 GeV まで加速する。その後 LHC でビームエネルギー7 TeV, 重心系エネルギー 14 TeV まで加速する。図 1.2に LHC と前段加速器を示す。表 1.2に LHC と前段加速器の長さとエネルギーを示す。

表 1.1: LHC 設計値 [1]. 2012 年までは重心系エネルギー 8 TeV, ルミノシティ  $0.6 \times 10^{34} \mathrm{cm}^{-2} \mathrm{s}^{-1}$

| リング周長     | $26.7~\mathrm{km}$                      |

|-----------|-----------------------------------------|

| 偏向磁場      | 8.33 T                                  |

| 重心系エネルギー  | 14  TeV                                 |

| ルミノシティ    | $10^{34} \text{ cm}^{-2} \text{s}^{-1}$ |

| バンチ間隔     | 24.95  ns                               |

| バンチあたり陽子数 | $1.15 \times 10^{11}$                   |

図 1.1: LHC 外観図 [2]. スイス・ジュネーブ郊外の CERN 研究所, 地下約 100 m にある.

表 1.2: LHC と前段加速器の長さとエネルギー [2]. 段階的に加速し, LHC でビームエネルギー 7 TeV, 重心系エネルギー 14 TeV まで加速する.

|         | length            | energy          |

|---------|-------------------|-----------------|

| Linac2  | $30 \mathrm{m}$   | 50  MeV         |

| Booster | $160~\mathrm{m}$  | $1.4~{\rm GeV}$ |

| PS      | $630~\mathrm{m}$  | $25~{\rm GeV}$  |

| SPS     | $6.9~\mathrm{km}$ | $450~{\rm GeV}$ |

| LHC     | $27~\mathrm{km}$  | $7~{ m TeV}$    |

# 1.2 ATLAS 検出器

# 1.2.1 全体像

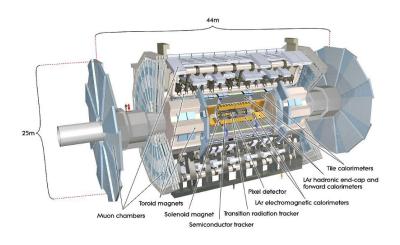

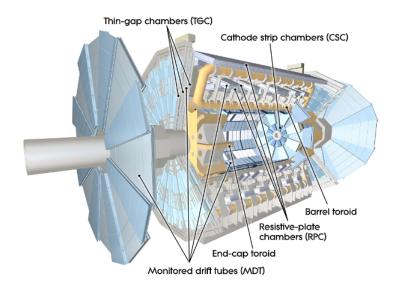

ATLAS は Higgs 粒子や標準理論を超える現象を探す. 直径 25 m, 長さ 44 m の円筒形で LHC の検出器では最大規模である. 衝突型加速器の検出器は内側から飛跡検出器, 電磁カロリメータ, ハドロンカロリメータ, ミューオン検出器で構成される. 飛跡検出器はソレノイド磁場で曲がる荷電粒子の飛跡運動量を測定する. 電磁カロリメータは電磁シャワーにより電子と光子のエネルギーを測定する. ハドロンカロリメータはジェットのエネルギーを測定する. ミューオンは最外部のミューオン検出器で軌跡を測定する. ATLAS は磁石が特徴的である. 一般的なソレノイド磁石に加えてトロイド磁石を用いる. これによりミューオンの運動量を測定する. 図 1.3 に ATLAS の全体像を示す. 図 1.4 に ATLAS 座標を示す.

# **CERN's accelerator complex**

図 1.2: LHC と前段加速器 [2]. まず陽子イオン源から出た陽子イオンを線形加速器 Linac2 で加速する. 次に シンクロトロン PS Booster で 1.4 GeV まで加速する. Proton Synchrotron (PS), Super Proton Synchrotron (SPS) で 450 GeV まで加速する. その後 LHC に入射する.

図 1.3: ATLAS の全体像 [4]. 内側から飛跡検出器, 電磁カロリメータ, ハドロンカロリメータ, ミューオン検出器.

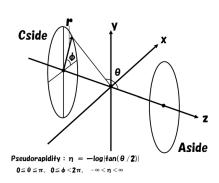

図 1.4: ATLAS の座標 [24]. ATLAS では xyz 座標もしくは  $r\phi z$  座標を用いる.

図 1.5: Muon Spectrometer[4]. ATLAS 最外部のミューオン検出器のまとまり.

ATLAS では xyz 座標もしくは  $r\phi z$  座標を用いる. xyz 座標系はビーム方向を z 軸, LHC 中心方向を x 軸, それらと垂直な方向を y 軸とする. z 軸は反時計回りが正である. ATLAS がわずかに傾いているため, y 軸は正確な天頂方向ではない. また, ATLAS の z 軸が正の方向を A-side, 負の方向を C-side と呼ぶ.  $r\phi z$  座標ではビーム方向を z, 動径方向を r, 方位角方向を  $\phi$  とする.

また、 擬ラピディティ $\eta$ を使う. これは衝突点からの天頂角 $\theta$ を用いて次式である. ATLAS の筒状の Barrel 部と円盤状の Endcap 部を $\eta$ で区別する.

$$\eta = -\ln\left(\tan\left(\theta/2\right)\right)$$

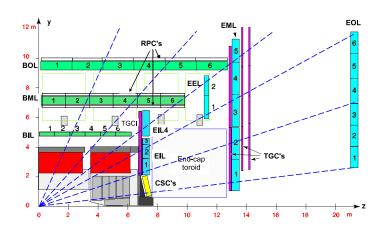

### 1.2.2 Muon Spectrometer

Muon Spectrometer [5] は ATLAS 最外部のミューオン検出器のまとまりである。Precision Chamber と Trigger Chamber がある。Precision Chamber はトロイド磁場の  $\phi$  方向と垂直な r-z 平面上の位置を  $50\mu$ m 程度の精度で測定する。トリガー Chamber は 25 ns 以内の応答, $p_{\rm T}$  測定によるトリガー,数 mm~1 cm の精度での第二座標  $(\phi)$  を測定する。図 1.5 に Muon Spectrometer を示す。表 1.3 に各 Chamber の性能を示す。

表 1.3: Muon Spectrometer の性能 [5]. Forward は頻度が高いので検出器を使い分けるなどする.

| 検出器 | 検出領域 $( \eta )$ | 表面積 (m²) | チャンネル数 (10 <sup>4</sup> ) | 分解能                |

|-----|-----------------|----------|---------------------------|--------------------|

| MDT | -2.7            | 5500     | 37                        | $80~\mu\mathrm{m}$ |

| CSC | 2.0 - 2.7       | 27       | 6.7                       | $60~\mu\mathrm{m}$ |

| RPC | -1.1            | 3650     | 35.5                      | ~1 mm              |

| TGC | 1.0 - 2.4       | 2900     | 44                        | ~1 cm              |

#### **Precision Chamber**

• Monitored Drift Tube (MDT)

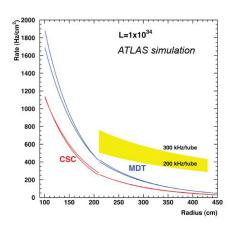

頻度上限が 500 Hz/cm<sup>2</sup>, 300 kHz/tube (2m) である. cathod 径 30 mm, anode 径 50 $\mu$ m の drift tube で構成する. drift tube 1 本の位置分解能は  $80\mu$ m である. spacer frame の両側 に, drift tube を 3 本か 4 本層状に並べ 1 つの chamber とする.

• Cathod Strip Chamber (CSC)

Forward  $(2.1 < |\eta| < 2.7)$  では頻度上限が  $1000 \text{Hz/cm}^2$  の CSC を用いる. wire 間隔 2.54 mm, strip 読み出し間隔 5.08 mm の, 位置分解能  $60\mu$ m.

# Trigger Chamber

• Resistive Plate Chamber (RPC)

Barrel を担当する. 高抵抗板を電極として用いるガス検出器の一種である. ATLAS では互いに直交する strip を用いて  $z-\phi$  情報を取得する.

• Thin Gap Chamber (TGC)

Endcap を担当する. Multi-Wire Proportional Chamber (MWPC) の一種である.anode wire と垂直な cathod strip を持つ. wire 間の距離 (1.8 mm) より wire ・ strip 間の距離 (1.4 mm) が短い. これによりバンチ間隔 25 ns 以内に  $r-\phi$  情報を読み出す.

# 配置

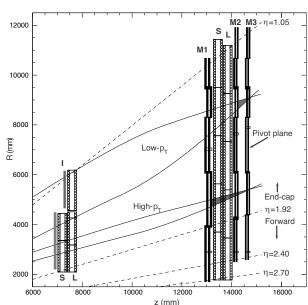

Muon Spectrometer では、Barrel 部に 3つの筒状のステーション (Inner、Middle、Outer)、Endcap 部に 4つの円盤状のステーション (I, M, O, Extra) がある。これらを EM (Endcap-Middle) などと表す。また、EM を BW(Big Wheel)、EI を SW(Small Wheel)と呼ぶ。表 1.4 に各ステーションの構成を示す。トロイド磁石が 8 回対称なので、各ステーションも  $\phi$  方向に 16 分割される。Barrel トロイド磁石間の Large sector が 8つ、Barrel トロイドの直近の Small sector が 8つである。表 1.4 に Large sector ステーションの構成。図 1.6 に Large sector r-z 平面配置図を示す。

図 1.6: Large sector r-z 平面配置図 [4]. Barrel 部に 3 つの筒状のステーション (Inner, Middle, Outer), Endcap 部に 4 つの円盤状のステーション (I, M, O, Extra) がある. これらを EM (Endcap-Middle) などと表す.

図 1.7: ソレノイドとトロイド [4]. これにより荷電粒子の飛跡を曲げて運動量を測定する. トロイド磁石が8回対称なので,各ステーションも $\phi$ 方向に16分割される. Barrelトロイド磁石間の Large sectorが8つ, Barrelトロイドの直近のSmall sectorが8つである.

表 1.4: Large sector ステーションの構成 [5]. Endcap は TGC でトリガーをかけ, Middle まで使っている.

| ステーション | 検出領域 ( η ) | トラッキング               | トリガー | 第二座標測定               |

|--------|------------|----------------------|------|----------------------|

| BI     | -1.0       | MDT                  |      |                      |

| BM     | -1.0       | MDT                  | RPC  | RPC                  |

| В0     | -1.0       | MDT                  | RPC  | RPC                  |

| EI     | 1.0 - 2.0  | MDT                  |      | TGC                  |

|        | 2.0 - 2.7  | $\operatorname{CSC}$ |      | $\operatorname{CSC}$ |

| EM     | 1.0 - 2.4  | MDT                  | TGC  | TGC                  |

|        | 2.4 - 2.7  | MDT                  |      | TGC                  |

| E0     | 1.4 - 2.7  | MDT                  |      |                      |

| EE     | 1.0 - 1.4  | MDT                  |      |                      |

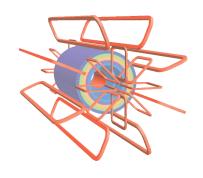

# 1.2.3 磁石

ATLAS はソレノイドとトロイドの 2 種類の超伝導電磁石を用いる. これにより荷電粒子の飛跡を曲げて運動量を測定する. 図 1.7 にソレノイドとトロイドを示す.

# ソレノイド磁石

ID の外側に z 方向約 2T の磁場を発生させる超伝導ソレノイド磁石がある. 荷電粒子を  $\phi$  方向に曲げ, ID で  $p_{\rm T}$  を測定する.

#### Barrel トロイド磁石

Barrel 部はカロリメータの外側に長さ 25m のトロイド磁石がある. 8 つの超伝導コイルにより  $\phi$  方向に約 0.5T の磁場が発生する. 荷電粒子を  $\eta$  方向に曲げ, RPC で  $p_T$  を測定する.

# Endcap トロイド磁石

Endcap 部にも長さ 5m のトロイド磁石がある. 各コイルは Barrel 部のものと  $22.5^{\circ}$  ずつずれて配置されている.  $\phi$  方向約 1T の磁場により荷電粒子を曲げ, TGC で  $p_{\rm T}$  を測定する.

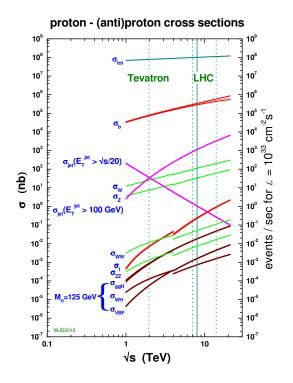

# 1.3 ATLAS のトリガーと DAQ

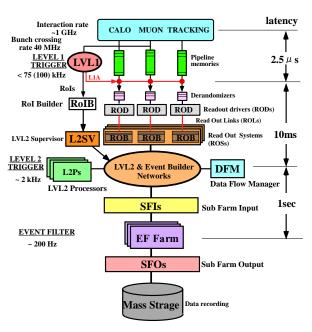

ATLAS では希な事象を探すためトリガーと Data Acquisition (DAQ) が重要になる. LHC では 40 MHz で衝突が起こり、一回の衝突で数 10 個の陽子が反応する. 図 1.8 に重心系エネルギーと断面積を示す。合計断面積  $\sigma_{\rm tot}$  はほとんどエネルギー落とさない反応である。これを全て拾うと DAQ 頻度が約  $1{\rm GHz}$  となる。しかし例えば Higgs 粒子の生成は 14 TeV では  $10^9$  事象に 1 事象程度である。そこで ATLAS では 3 段階のトリガーで DAQ 頻度 を  $200{\rm Hz}$  程度にする。Level1 (L1) で 75 kHz, Level2 (L2) で 2 kHz, Event Filter (EF) で 200 Hz, 程度である。L1 は  $2.5\mu{\rm s}$  以内に判定するためにハードウェアで行う。L2, EF はソフトウェアで行う。L2, EF をまとめて High Level Trigger (HLT) と呼ぶ。図 1.9 に ATLAS の 3 段階トリガーと DAQ を示す。

#### 1.3.1 L1 トリガー

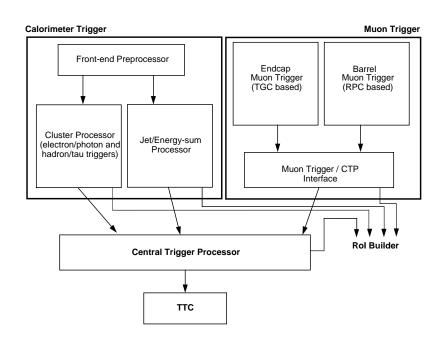

Level1 (L1) トリガー はミューオンの  $p_T$  や電子, 光子, ジェット等のエネルギー情報を用いる. 前者 は TGC, RPC から受け取る. 後者は電磁/ハドロンカロリメータから精度を落としたものを受け取る. これらの検出器と, Central Trigger Processor (CTP), Timing Trigger and Control distribution system (TTC) で構成する. 図 1.10 に L1 トリガー システムを示す.

読み出しデータは L1 の遅延時間  $2.5\mu s$  間は保持する必要がある. バンチ間隔は約 25 ns である. そのため 100 段程度のパイプラインメモリ, L1 Buffer でトリガーを待つ. CTP は MUon (MU), ElectroMagnetic (EM), Jet (Jet) 等のトリガーメニューを持つ. いずれかの基準を満たした場合に Level1 Accept (L1A) トリガー信号が発行される. L1A は TTC によりフロントエンドの L1 Buffer 配らる. derandomizer で L1A のばらつきを吸収し, Read Out Driver (ROD) に送信する. ROD はデータを ATLAS 共通形式に変換し, Read Out System (ROS) に送る. ROS は複数の Read Out Buffer (ROB) で構成され, L2 までデータを保持する. この流れとは別に, Region of Interest (RoI) 情報を L2 に渡す. RoI は L1 の粒子の  $\eta$  と  $\phi$  領域で, L2 に使用する.

図 1.9: ATLAS の 3 段階トリガーと DAQ [4]. LHC では 40 MHz で衝突が起こり, 一回の衝突で数 10 個 の陽子が反応する. ATLAS では 3 段階のトリガーで DAO 頻度 を 200Hz 程度にする

図 1.8: 重心系エネルギーと断面積 [9]. Higgs 粒 DAQ 頻度 を 200Hz 程度にする. 子の生成は 14 TeV では  $10^9$  事象に 1 事象程度.

図 1.10: L1トリガーシステム [4]. ミューオンと電磁/ハドロンカロリメータの検出器と, Central Trigger Processor (CTP), Timing Trigger and Control distribution system (TTC) で構成する.

図 1.11: TTC システム [22]. フロントエンドにタイミング/トリガー 信号やコマンドを配る.

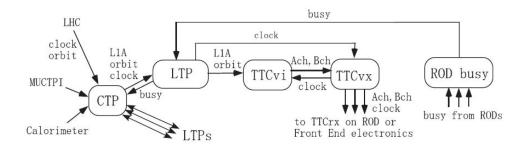

#### TTC

TTC はフロントエンドにタイミング/トリガー 信号やコマンドを配る. タイミング/トリガー信号は clock, L1A, Event Count Reset (ECR), Bunch Count Reset (BCR) 等である. 図 1.11 に TTC システムを示す. TTC は Local Trigger Processor (LTP), TTCvi, TTCvx, ROD busy で構成する. LTP CTP から Timing/トリガー 情報を受け取り, clock を TTCvx に, 他を TTCvi に渡す. L1A を渡すだけでなくトリガーを出すこともできる.

TTCvi はトリガーを A-Channel, その他を B-Channel として TTCvx に渡す. TTCvx は 2 種類の信号を Time Division Multiplexing (TDM) により多重化し, 光信号でフロントエンドに配る. RODbusy は ROD の busy 信号をまとめ, LTP 経由で CTP の L1A を止める. フロントエンドでの TTC 受信には, TTCrx ASIC を用いる. TGC フロントエンドでは TTCrx を持つ TTCrq カードを用いる. fan-out して各 L1 Buffer に L1A を配る.

# 1.3.2 L2 トリガー

Level2 (L2) では L1 より高精度なトリガー判定を行う. MDT, CSC, ID などを用いる. 40ms の遅延制約があるため, RoI を元に適切なデータを ROS から読む. L2 判定が出ると L2 Accept (L2A) が発行される. ROS のデータは L2A の時 Sub Farm Input (SFI) に書く.

#### 1.3.3 EF

Event Filter (EF) では RoIs で限定せず全ての情報を用いる. トリガー判定は EF Farm で並列処理する. FF Farm は複数の EF Sub Farm から構成する. EF Sub Farm は SFI からデータを受け, 最大 4sec かけてトリガーする. トリガー後 Sub Farm Output (SFO) から最終的なディスクに書く.

# 1.4 LHC のアップグレード

LHC は今後 Higgs 粒子の精密測定や超対称性粒子の探索を行う. このためにはより高いエネルギーと積分ルミノシティが必要である. そこで LHC は重心系エネルギーを設計値の 14 TeV にする. また, 瞬間ルミノシティを設計値の 5 倍,  $5\times10^{34} {\rm cm}^{-2} {\rm s}^{-1}$  にする. これを High-Luminosity LHC (HL-LHC) と呼ぶ. 2030 年頃までに積分ルミノシティ3000fb $^{-1}$  を目指す. LHC は 2009 年

の 900 GeV 運転に始まり 2010, 2011 年 7 TeV, 2012 年 8 TeV と重心系エネルギーを増強した. 2013 年は Long Shutdown (LS) に入る. LS では補修やアップグレードをする. 表 1.5 に HL-LHC 計画を示す.

表 1.5: HL-LHC 計画 [6]. 2019 年からは重心系エネルギー 14 TeV, ルミノシティ  $2 \times 10^{34} \mathrm{cm}^{-2} \mathrm{s}^{-1}$

| 年         | 重心系エネルギー (TeV) | 瞬間ルミノシティ $(cm^{-2}s^{-1})$ |

|-----------|----------------|----------------------------|

| 2012      | 8              | $6 \times 10^{33}$         |

| 2013-14   | LS1            |                            |

| 2015 - 17 | 13 <b>~</b> 14 | $1 \times 10^{34}$         |

| 2018      | LS2            |                            |

| 2019-21   | 14             | $2 \times 10^{34}$         |

| 2022      | LS3            |                            |

| 2023-     | 14             | $5 \times 10^{34}$         |

# 1.4.1 Long Shutdown 1

LHC の重心系エネルギーを 8 TeV から 13, 14 TeV にする. ルミノシティを設計値の  $1 \times 10^{34} \rm cm^{-2} s^{-1}$  にする. 加速管同士の接合を強化する, 弱くなった磁石を交換する, 放射線対策のために電子装置を移動するなどがある.

# 1.4.2 Long Shutdown 2

ルミノシティを 2 倍の  $2\times 10^{34} {\rm cm}^{-2} {\rm s}^{-1}$  にする. LHC Injectors Upgrade (LIU) が予定されている. Linac2 から Linac4 への移行, PS Booster のエネルギー増加, SPS の電子雲対策などがある. Linac2 は 50MeV だが, Linac4 では 160MeV になり, PS Booster は 1.4 GeV から 2 GeV になる. PS Booster では, Japan Proton Accelerator Research Complex(J-PARC) の金属磁性体合金を用いた高周波加速空洞が採用されるなど,日本の寄与が大きい [26].

# 1.4.3 Long Shutdown 3

ルミノシティを  $5 \times 10^{34} {\rm cm}^{-2} {\rm s}^{-1}$  にする. Interaction Region (IR) の磁石の強化, 超伝導クラブ空洞の導入などがある. IR の磁石にはビーム収束用の四重極磁石 (Q1, Q2, Q3) とビーム分離・再結合用の双極子磁石 (D1, D2) がある. このうち KEK が D1 の制作を検討しており, 6T 級の大口径磁石を作るための研究開発が行われている. クラブ空洞ではバンチの向きを回転して高ルミノシティを得ることができる. これは日本の KEKB 加速器で世界で初めて実用化した技術であり, 技術協力などで日本が貢献する [27].

# 1.5 ATLAS のアップグレード

ルミノシティが上がるにつれ、パイルアップの他にもさまざまな問題が出る. 読み出しやトリガーの負荷が増える検出器自体の放射線損傷が早まる cavern background  $^1$ が増えるなどである. これらに対応するため、ATLAS も 3 回の LS に合わせて段階的にアップグレードする. LHC の LS1、LS2、LS3 に対して Phase-0、Phase-1、Phase-2 と呼ぶ.

#### 1.5.1 Phase-0

Phase-0 の計画のひとつに Muon Spectrometer の改善がある. 現在 Endcap Extra (EE) Chamber は穴がある. このため Endcap 部と Barrel 部の境  $(1.0 < |\eta| < 1.3)$  でのトラッキング効率が低い. そこで残りを導入してこの穴を埋める. また, カロリメータとシールディングディスクの間  $(z \simeq 7\mathrm{m})$  はビームパイプがシールドされていない [5]. ここから光子や中性子が漏れ出てくる. ここに新しいシールドを置く.

#### 1.5.2 Phase-1

Phase-1 では L2 の一部を L1 に移すなどをする. 現在は Small Wheel (SW) の MDT と CSC が  $1.3 < |\eta| < 2.7$  のトラッキング情報を生成している. この SW を, New Small Wheel (NSW) にする. 動機は以下である.

- SW の MDT が設計ルミノシティ以上で性能劣化する.

図1.12に MDT と CSC の rate を示す. MDT の限界頻度は 500 Hz/cm<sup>-2</sup>, 300 kHz/tube (2m) である.MDT は 1 × 10<sup>34</sup>cm<sup>-2</sup>s<sup>-1</sup> の時点で頻度の余裕が少ない.

- フェイクトリガーを落とす

現在 L1 ミューオントリガーの約 98%はフェイクである. これはミューオン以外の荷電粒子によるバックグラウンドの存在や,  $p_{\rm T}$  分解能が悪いために生じる. NSW を用いたトリガーでこれを除く.

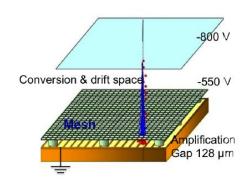

NSW は最終的に MicroMegas (MM) と small TGC (sTGC) に決定した。MM に入射した ミューオンは電極と金属製のメッシュの間の数 mm の領域でイオン対を生成する。電子はメッシュ に向かってドリフトする。メッシュと読み出し電極の間は約  $100\mu m$  で 40kV/cm 程度である。こ のためドリフト電子はメッシュを通過して電子雪崩で  $10^4$  倍に増幅する。陽イオンが 100 ns 程度 で捌けるのでトリガーとしても用いることができる。図 1.13 に MM の概略図を示す。sTGC は cathod strip の抵抗率を低減することで、 $30kHz/cm^2$  の高頻度に耐えられるようにした TGC である。MM、sTGC ともに  $100\mu m$  よりも良い位置分解能が得られる。

<sup>1</sup>反応後に検出器ホールを漂う熱中性子や低エネルギー光子のバックグラウンド

図 1.12: MDT と CSC の rate[10]. MDT の限界頻度は 500 Hz/cm<sup>2</sup>, 300 kHz/tube (2m).

図 1.13: MicroMegas の概略図 [10]. メッシュ と読み出し電極の間は約  $100\mu$ m で 40kV/cm 程度である. このためドリフト電子はメッシュ を通過して電子雪崩で  $10^4$  倍に増幅する.

#### 本研究の目的

本研究の目的はこの NSW を用いた新しい L1 Endcap ミューオントリガー装置を開発することである. これにより 2019 年の LHC 重心系エネルギー 14 TeV, ルミノシティ  $2\times10^{34} {\rm cm}^{-2} {\rm s}^{-1}$  での ATLAS 実験を可能にする. また, 装置に汎用性を持たせることで他の実験にも応用可能にする. 最新の FPGA を用いて開発を行い高速化, 集積化の要求に応える.

#### 1.5.3 Phase-2

Phase-2 では総線量の限界を迎える検出器と電子装置を交換する. ミューオントリガーではフェイクを減らすため, 大幅な変更が検討されている. L1 を 2 つに分けてハードウェアによるトラッキングトリガーを導入する. これを L0/L1 とする.

# 第2章 L1 Endcap ミューオントリガー

L1 ミューオントリガー はWやZの崩壊などからくる high  $p_T$  ミューオンを判定する. 本章では L1 Endcap ミューオントリガー Thin Gap Chamber (TGC) システムについて述べる. また, そのアップグレード計画を述べる.

### 2.1 TGC

# 2.1.1 TGC の動作原理

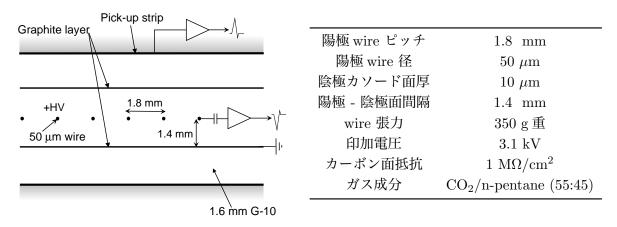

TGC は Multi Wire Proportional Chamber (MWPC) の一種である. 直交する anode wire と cathod strip により 2 次元情報を出力する. wire 間は 1.8 mm で, wire と strip 間は 1.4 mm と 短く, 25 ns 以内に応答する.  $4\sim33$  本の wire が R 方向の 1 ch, 1 本の strip が  $\phi$  方向の 1 ch で ある. 図 2.1 に TGC の構造を示す.

$CO_2$ : n-pentane が 55:45 のガスを用いる.  $CO_2$  が電離ガス, n-pentane がクエンチャーである. ガス中を荷電粒子が通過して電離した一次電子は, chamber 内の強電場を移動する. そして最も近くの wire に近づくと急激に加速され, 電子雪崩を起こす. wire はこの電子雪崩を信号として取り出し, また strip 側も同時に誘起する電荷を読み出す. 電離の際に生じる紫外線は n-pentane が吸収し, 必要以上の電子雪崩の発生を抑える.

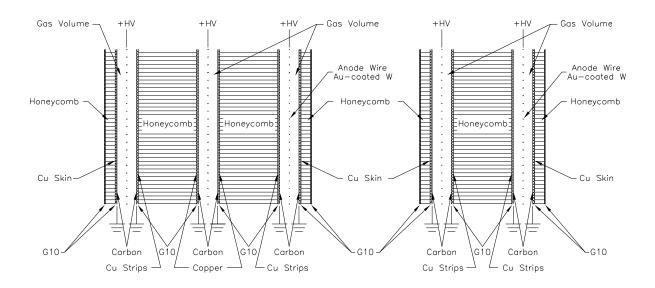

#### 2.1.2 TGC **の**種類

TGC は層の数で分類すると, Doublet と Triplet がある. Doublet は 2 つのガスギャップをハニカムで支え, 2 層の wire と 2 層の strip を持つ. Triplet では 3 つのガスギャップをハニカムで支え, 3 層の wire と上下 2 層の strip 層を持つ. 図 2.2 に Doublet と Triplet の構造を示す.

図 2.1: TGC の構造 [4]. wire と strip 間は 1.4 mm と短く, 25 ns 以内に応答する.

図 2.2: Doublet と Triplet の構造 [4]. Doublet は 2 つのガスギャップをハニカムで支え, 2 層の wire と 2 層の strip を持つ. Triplet では 3 つのガスギャップをハニカムで支え, 3 層の wire と上下 2 層の strip 層を持つ.

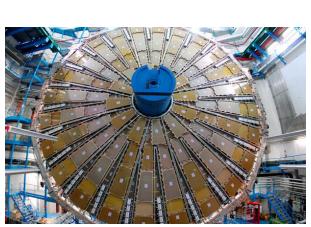

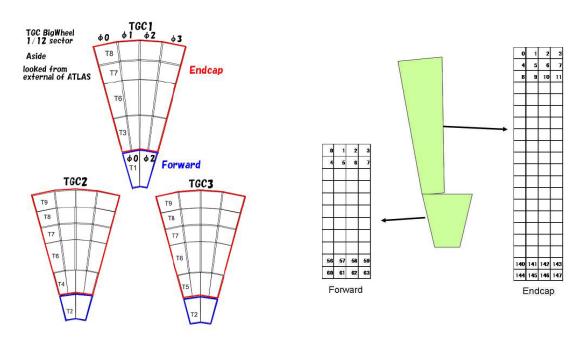

また、大きさで分けると T1~T9 がある. T1 と T2 は  $\phi$  方向に  $2\pi/24=0.26$ rad の幅を持つ. T3~T9 はその 1/2 の  $\phi$  幅である. Triplet の T1, T3, T6, T7, T8 をこの順に R の小さい方から並べて  $\phi$  方向に一周させたものが TGC1 (M1) である. T1 を 24 枚, そのほかを 48 枚使って 1 つの大きな円盤が出来る. 同様に Doublet の T2, T4, T6, T7, T8, T9 で作ったのが TGC2 (M2), Doublet の T2, T5, T6, T7, T8, T9 で作ったのが TGC3 (M3) である. M1, M2, M3 は MDT ともに Big Wheel (BW) を構成する. 図 2.3 に Big Wheel を示す.

#### 2.1.3 TGC **の配置**

BW の最も内側  $(z \simeq 13\text{m})$  が M1, 中段  $(z \simeq 14\text{m})$  が M2, 外側  $(z \simeq 14.5\text{m})$  が M3 である. IP から見ると wire が 7 層, strip が 6 層ある. M1 と M2 の 1m ほどの間隙に MDT がある. 図 2.4 に TGC の配置図を示す.

TGC では  $1.05 < |\eta| < 1.92$  を Endcap ,  $1.92 < |\eta| < 2.70$  を Forward と呼ぶ. T1, T2 の範囲が Forward である. トリガーや DAQ はこの 2 つで分けて処理される. なお Forward のうち  $2.40 < |\eta| < 2.70$  の領域は M1 しかないため, トリガー情報は生成されず位置のみ測定される.

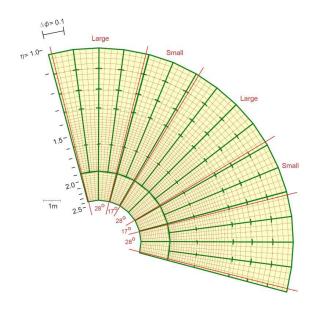

# 2.1.4 TGC のセクター

TGC の組み立てやデータ処理は、円盤を  $\phi$  方向に 1/12 分割したセクターという単位で行われる. また、Forward 部は chamber1 枚、Endcap 部は R 方向に連続した 4 枚(M1)または 5 枚(M2、M3)をトリガーセクターと呼ぶ、1 セクターには Forward のトリガーセクターが 2 つ( $\phi$ 0、 $\phi$ 2)、Endcap のトリガーセクターが 4 つ ( $\phi$ 0  $\sim$   $\phi$ 3)含まれる.

これらはさらに小さいサブセクターに分かれる. 1 つのサブセクターを wire, strip ともに 8 channel とすると, Endcap では  $37(R) \times 4(\phi) = 148$  サブセクター, Forward では  $16(R) \times 4(\phi) = 148$

図 2.3: Big Wheel[4]. M1, M2, M3 は MDT と ともに Big Wheel (BW) を構成する.

図 2.4: TGC の配置図 [4]. M1 だけ Triplet

64 サブセクターになる. サブセクターはトリガーする位置の最小単位であり, RoI に用いる. 図 2.5 に TGC のセクターとサブセクターの概略図を示す.

# 2.2 L1 Endcap ミューオントリガー 概要

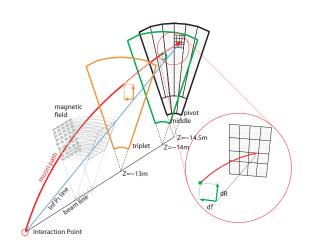

# 2.2.1 $p_{\rm T}$ 判定

TGC では磁場によるミューオンの軌跡の曲がり具合から  $p_T$  を判定する. 流れは以下である.

- 1. IP で陽子の衝突が起こり, W や Z の崩壊などによりミューオンが生成される.

- 2. ミューオンは BW に到達する前に Endcap トロイド磁場によって曲げられる.

- 3. 磁場を通過した後, BW の M1, M2, M3 の順にヒットする.

- 4. M3のヒット点と IP を結んだ直線がミューオンが無限運動量を持った時の飛跡とする.

- 5. この直線と磁場で曲がった飛跡のずれ, dR,  $d\phi$  から  $p_T$  を推定する.

$p_{\rm T}$  が高いほど磁場で曲げられにくいので dR,  $d\phi$  は小さくなる. 理想的には磁場は  $\phi$  方向なので  $d\phi=0$  だが, 磁場の非一様性から  $\phi$  方向にもずれる. 図 2.7 に dR,  $d\phi$  を示す.

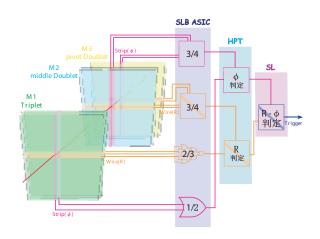

# 2.2.2 段階的なコインシデンス

#### 1. SLB ASIC

Doublet 内のコインシデンスと Triplet 内のコインシデンスは, wire と strip 独立に行う. このとき SLB (Slave Board)ASIC を用いる. SLB ASIC は 4 種類, Doublet /Triplet・Wire/Strip

図 2.5: TGC のセクターとサブセクター [24][25]. サブセクターは RoI に用いる.

図 2.6:  $dR, d\phi$  [22]. これらの情報から  $p_{\rm T}$  を推定する.

図 2.7: 段階的なコインシデンス [22]. 最後のコインシデンスは wire と strip 間で行う.

表 2.1: L1 トリガーメニューと  $p_{\rm T}$  の関係. L1\_MU20 の頻度を要求 20kHz に押さえたい.

| L1 menu    | pt1~6 | condition                  |

|------------|-------|----------------------------|

| L1_MU0     | pt1   | p <sub>T</sub> 6 GeV 未満    |

| $L1\_MU6$  | pt2   | $p_{ m T}$ 6 GeV 以上        |

| L1_MU10    | pt3   | 現在使用されていない                 |

| L1_MU11    | pt4   | $p_{\mathrm{T}}$ 11 GeV 以上 |

| $L1\_MU15$ | pt5   | $p_{\mathrm{T}}$ 15 GeV 以上 |

| $L1\_MU20$ | pt6   | $p_{\mathrm{T}}$ 20 GeV 以上 |

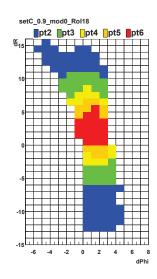

図 2.8: CW の例 [25]. 中心からのずれは、各 chamber の $\eta$ の位置較正による.

の (WD/SD), (WT/ST) がある. WD, SD では 3/4 コインシデンス, WT では 2/3 コインシデンス, ST では 1/2 コインシデンスをとる. さらに WD, SD ではコインシデンスマトリックスにより Low- $p_{\rm T}$  <sup>1</sup>情報が生成される. 図 2.7 に段階的なコインシデンスを示す.

# 2. HpT ボード

次のコインシデンスは Doublet と Triplet 間で行う. HpT (High- $p_T$ ) ボードで行う. HpT ボードは wire , strip の 2 種類がある. コインシデンス行列により High- $p_T$  2情報が生成され, 複数の Low- $p_T$ , High- $p_T$  track から高いものを選択して SL に送る.

#### 3. SL ボード

最後のコインシデンスは wire と strip 間で行う. Sector Logic (SL) ボードが処理する. Coincidence Window (CW) と呼ばれる仕組みを用いて最終的な  $p_{\rm T}$  情報が生成される.

#### 2.2.3 CW

L1 ミューオントリガーでは  $p_{\rm T}$  を pt1~pt6 の 6 段階に分ける. CW は SL に届いた dR,  $d\phi$  の 組が 6 段階のどれかをマップしたものである. CW は SL に Look Up Tabl (LUT) として実装されている. dR,  $d\phi$  をアドレスに変換して対応する  $p_{\rm T}$  値を読み出す. 表 2.1 に L1 トリガーメニューと  $p_{\rm T}$  の関係を示す.

図 2.8 は CW の例を示す. 中心からのずれは、各 chamber の $\eta$ の位置較正による. CW は RoI の数だけ存在する. 磁場の 8 回対称性から 1/8 円について考える. RoI, CW の数は  $6 \times 148 + 3 \times 64 = 1080$  である. CW はモンテカルロシミュレーションを用いた解析により修正される.

$<sup>^{1}</sup>$ M2 M3 の Doublet の距離が短く高い  $p_{\mathrm{T}}$  が測れない

$<sup>^2</sup>$ M1 M3 の Doublet と Triplet は離れているので高い  $p_T$  が測れる

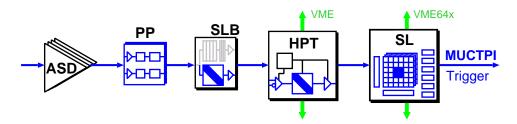

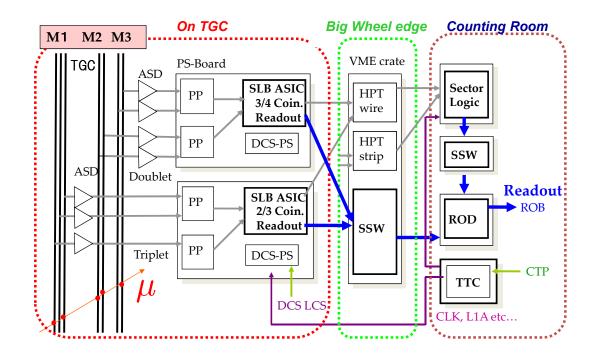

図 2.9: トリガーの流れ [23]. Amplifier Shaper Discriminator (ASD), Patch Panel (PP), SLave Board (SLB), High  $p_T(\text{HpT})$ , SL, Muon Trigger to CTP Interface (MUCTPI) である.

# 2.3 L1 Endcap ミューオントリガー 電子装置

# 2.3.1 トリガーの流れと配置

トリガーの流れは TGC, Amplifier Shaper Discriminator (ASD), Patch Panel (PP), SLave Board (SLB), High  $p_{\rm T}({\rm HpT})$ , SL, Muon Trigger to CTP Interface (MUCTPI) である. 一定の遅延時間で処理するために各所に可変ディレイ回路がある. PS ボードは PP と SLB を持つ. 表 2.2 に遅延時間の例を示す.

|        | ASD | cable | PS Board | cable | HpT | fibre | $\operatorname{SL}$ | cable | MUCTPI |

|--------|-----|-------|----------|-------|-----|-------|---------------------|-------|--------|

| クロック消費 | 0.5 | 2.5   | 6        | 3     | 6.5 | 18    | 9.5                 | 2     | 11     |

| 総クロック  | 5   | 7.5   | 13.5     | 16.5  | 23  | 41    | 50.5                | 52.5  | 63.5   |

表 2.2: 遅延時間の例 [28]. 現行の SL は約 10 クロックの遅延時間である.

各装置の配置を述べる.ASD は増幅整形デジタル化のため TGC の出力部にある.そこから LVDS  $^3$  信号をフラットケーブルで PS ボードに送る.PS ボードは複数でまとめられて BW 中にある.PS ボードの後は LVDS 信号をツイストペアケーブルで HpT ボードに送る.HpT ボードの入った HSC クレート は BW 外縁にある.図 2.10 に BW 中の PS ボードと BW 外縁の HSC クレートを示す.ここまでは実験ホール (UX15) である.

これ以降は 100m ほど離れた計測室 (USA15) にある. ATLAS では G-Link  $^4$ で光転送を行っている. HpT から SL も G-Link でつながれており, 40 クロック程度かけて SL に到達する. 図 2.11 に USA15 の様子を載せる.

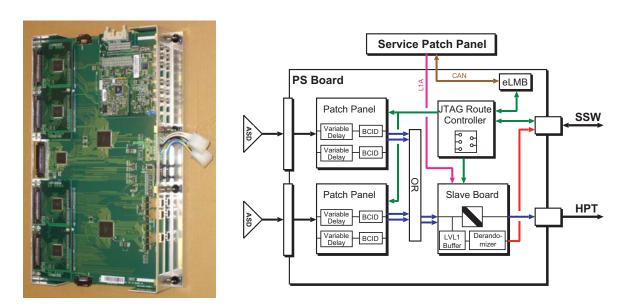

#### 2.3.2 フロントエンド

ASD から, PS ボードまでについて述べる. PS ボードは PP, SLB などの ASIC を持つ. フロントエンドを読み出し, 制御する.PS ボードは 1/2 セクターごとにまとめられ, Triplet 用は 10 個, Doublet 用は 17 個がまとめられている. 図 2.12 に PS ボードの写真とブロック図を示す.

<sup>&</sup>lt;sup>3</sup>Low Voltage Differential Signaling: 高速差動信号の規格. A nsI/TIA/EIA-644 において最大 655 Mbps (理想的な伝送路で 1.923 Gbps) と記されている

<sup>&</sup>lt;sup>4</sup>Agilent Technologies 社のトランシーバチップ HDMP-1032/1034 で用いられている通信規格. TGC では 20bit × 40MHz = 800Mbps で使用する

図 2.10: BW 中の PS ボードと BW 外縁の HSC クレート [23]. ここまでは実験ホール.

図 2.11: USA15 の様子 [23]. 実験ホールから 100m ほど離れた計測室である.

図 2.12: PS ボードの写真とブロック図 [23]. PS ボードは PP, SLB などの ASIC を持つ.

図 2.13: ASD の写真とブロック図 [11]. ASD ASIC は TGC のアナログ信号を増幅整形し, 閾値電圧を超えていたらデジタルパルスを出す.

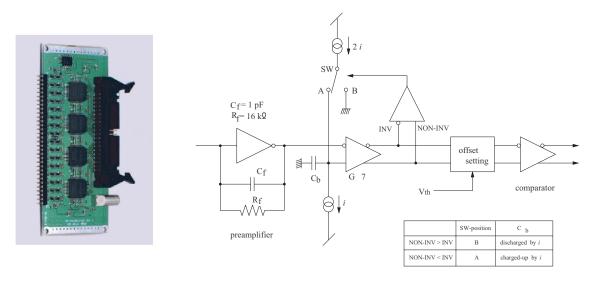

#### ASD

ASD ASIC は TGC のアナログ信号を増幅整形し, 閾値電圧を超えていたらデジタルパルスを出す. ASD ASIC は 4channel を処理する. ASD ボードは ASD ASIC を 4 つ持ち, 計 16 channel を担当する. また, 7 層の wire 及び 6 層の strip には全て同一の ASD ボードを用いる. 処理されたデジタル信号は LVDS で PS ボードに送られる. 図 2.13 に ASD の写真とブロック図を示す.

#### PP ASIC

PP ASIC はタイミング調整とバンチ識別をする. 各 PP に信号が届くタイミングは TOF(Time Of Flight) の差やケーブル長によりばらつく. 25/32=0.78ns を単位として  $0\sim24.2$  ns の範囲で遅延し、これを吸収する. バンチ識別では、TTC から供給される LHC クロックと同期をとる. 同じバンチのデータは同じクロックの立ち上がりにそろえる. 1 つの PP ASIC は 32channel、つまり 2 つの ASD ボードからの入力を処理できる.

#### SLB ASIC

SLB ASIC はトリガー部と読み出し部を持つ. 入力は共通で, 複数の PP からくる情報を並べた 最大 160 bit のヒットマップである. WD 及び SD のヒットマップは 4 層の wire / strip を 32bit  $\times$  4 のように並べた形になっている. 同様に WT のヒットマップは 3 層の wire を 32bit  $\times$  3 に並べた形である. ST は strip が 2 層なので 2 枚分の chamber を並べて 1 つのヒットマップとする.

トリガー部は、WD、SD、WT、ST の 4 種類を register で切り替える。WD、SD では 2 ヒット分の位置データと Low- $p_T$  情報が生成される。同様に WT では 3 ヒット分の位置データ、ST では 4 ヒット×2 chamber 分の位置データが生成される。これらトリガーデータと呼ぶ。

読み出し部は L1 Buffer と derandomier で構成される. L1 Buffer は 212bit × 128 段の shift register であり、最大  $3.2\mu s$  の間データを保持する. 212 bit のうち 160 bit はヒットマップである. 残りの 52 bit はトリガーデータ 40 bit, Bunch Crossing ID (BCID) カウンタ 12 bit である.

図 2.14: HpT ボードの写真 [22]. HpT ボードは Doublet と Triplet のコインシデンスをとる.

図 2.15: SL の写真 [23]. SL は R と  $\phi$  の情報を用いて最終的な  $p_{\rm T}$  を判定する.

L1A が来ると, 該当バンチと前後バンチのデータが derandomier に入る. その際 4 bit の L1ID カウンタが付加され, 216 bit 幅になる. 3 バンチ分のデータは別々のシリアライザから 4 bit 幅の LVDS で出力される.L1ID と BCID は TTC の Event Count Reset (ECR), Bunch Count Reset (BCR) で同期し, SLB 内で数える.

# 2.3.3 HSC クレート

HpT SSW Crate (HSC) は VERSAmodule Eurocard bus (VME) の 9U クレートである. 1 セクターに 1HSC クレートがあり, 合計 24 ある. BW の外縁で放射線を受けるため, HpT SSW Controller board (HSC) という特殊な VME マスターを持つ. HSC は G-Link で USA15 にある Control Configuration Interface board (CCI) から操作する.

# HpT

HpT ボードは Doublet と Triplet のコインシデンスをとる. HpT ASIC は wire か strip か, スイッチで選択する. 最大 6 track が High- $p_T$  track 候補になる. このうち  $p_T$  の高い 2 track を選出する. 2 track ない場合, Doublet の Low- $p_T$  track を加えて 2 track にする.

HpT ボードは Endcap Wire (EW), Endcap Strip (ES), ForWard (FW) の三種類がある。EW-HpT ボードは 1 トリガーセクターのデータを複数の SLB ASIC から受け、4つの HpT ASIC で処理する。最大 7 track  $^5$ のデータを G-Link で SL に送る。一方 ES-HpT ボードは 2 トリガーセクターを担当する。1 トリガーセクターにつき 2 HpT ASIC が処理する。それぞれ最大 4 track のデータを SL に送る。図 2.14 に FW-HpT ボードの写真を示す。

<sup>&</sup>lt;sup>5</sup>4 つのうち 1 つの ASIC は TGC の端なので、1 track しか選出しない

図 2.16: SL のブロック図 [22]. 1 つのトリガーセクターにつき, コインシデンス用 FPGA1 つと読み出し用 SLB ASIC1 つを用いる. L1Buffer と Derandomizer が SLB ASIC.

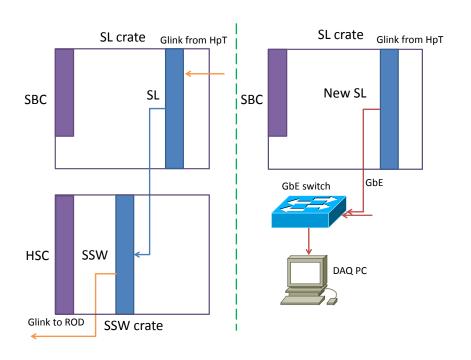

# 2.3.4 SL クレート

SL のクレートは USA15 にある.HpT とは G-Link で接続されている. 4 セクター分の SL と TTC の fan-out 装置, VME マスターとしての Single Board Computer (SBC) を持つ. 図 2.15 に SL の写真を示す.

#### $\mathbf{SL}$

SL は R と  $\phi$  の情報を用いて最終的な  $p_T$  を判定する. Endcap (EC) と ForWard (FW) の 2 種類存在する. EC-SL を 2 枚と FW-SL を 1 枚で 1 セクターである.

1つのトリガーセクターにつき、コインシデンス用 FPGA1 つと読み出し用 SLB ASIC1 つを用いる. 1枚の SL は 2 つのトリガーセクターのため、FPGA と SLB ASIC を 2 つずつ持つ. トリガーセクターごとに wire と strip のコインシデンスをとる.

FPGA では Sub Sector Cluster (SSC) ごとに 6 段階の pt 判定を行う. SSC は R 方向に 2 つ  $\phi$  方向に 4 つのサブセクターの集まりである. 次にプリセレクタにより各 pt につき 2 track 選ぶ. 最後に track セレクタで pt の順に 2 track を選び, MUCTPI に送る. 各 track の RoI, pt, BCID 等, 32 bit のパラレルデータを送る. BCID は SL の中で数える. 図 2.16 にブロック図を示す.

図 2.17: 読み出しの流れ [23]. SL は PS ボードと同様に SLB ASIC, SSW, ROD と読み出す.

# 2.3.5 SL の読み出し

SL は PS ボードと同様に SLB ASIC, Star SWitch (SSW), Read Out Driver (ROD) と読み出す. ただし SL の SSW は HSC クレートではなく USA15 の SSW 専用クレートにある. SLB ASIC は PS ボード のものと同じである. 32 bit のトリガーデータと SL の入力を読み出す. 図 2.17 に読み出しの流れを示す.

# SSW

SSW は SLB ASIC のデータを集めて圧縮する.FPGA を受信用に 6 つ, 送信用に 1 つ持つ. 1 つの受信 FPGA は最大 4 つの SLB ASIC からのデータを受ける.

圧縮は Zero Suppress で行う. これはデータを 8 bit ずつのセルにして, 全て 0 なら読み出さず, 1 があるものはセル番号を付けて読み出す. TGC のように 0 が連続する場合に有効である. 1 が多いとデータ量が増える. その後は送信用 FPGA から G-Link で ROD に送られる.

HSCrate の SSW は Doublet・Endcap / Forward , Triplet・Endcap / Forward の 4 種類がある.Doublet・Endcap はトリガーセクター 1 つ分, その他は 2 つ分をカバーし, 全部で 8 枚ある.

SL 用の SSW は 2 枚の EC-SL と 1 枚の FW-SL を受けるので, 1 枚で 1 セクターになる. 12 セクター分まとめられて USA15 の SSW 専用クレートにある. 図 2.18 に SSW を示す.

図 2.18: SSW[14]. SLB ASIC のデータを集めて 圧縮する. 圧縮は Zero Suppress で行う.

図 2.19: ROD[15]. TGC の読み出しデータが最終的に集まる装置である. データをATLAS 共通の形式にする.

#### ROD

ROD は TGC の読み出しデータが最終的に集まる装置である. データを ATLAS 共通の形式に する. ヘッダ・トレイラの情報を受けるために TTC 受信機を持つ. 1 セクター分の SSW のデータを受け取る. 形式変換後に S-Link[8] という光の規格で ROB に送る. また, エラーの場合には busy 信号を CTP に送る. 図 2.19 に ROD を示す.

# 2.3.6 TTC

TTC を受けるのは PS ボードの SLB ASIC, SL の SLB ASIC, ROD である. まず, BW 上の PS ボードには Service Patch Panel board (SPP) が連結されている. SPP は TTCrq という受信機で光をデコードし, フラットケーブルで各 PS ボードに TTC を配る. Doublet の 17 個連結された PS ボードに対応できるように, 最大 18 fan-out できる. SL は SPP を VME 用にした SL-SPP を用いる. これにより 12 枚の SL に TTC を配る. ROD では TTCrms という受信機を用いる. TTCoc という光 fan-out 装置で各 ROD に配る.

# 2.4 L1 Endcap ミューオントリガー のアップグレード

LHC は HL-LHC を目指して段階的にアップグレードする. それに伴い L1 ミューオントリガーもアップグレードが求められる. 本研究は Phase-1 における L1 Endcap ミューオントリガー装置のアップグレードに関わる.

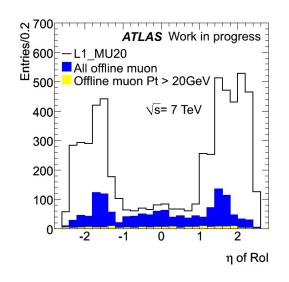

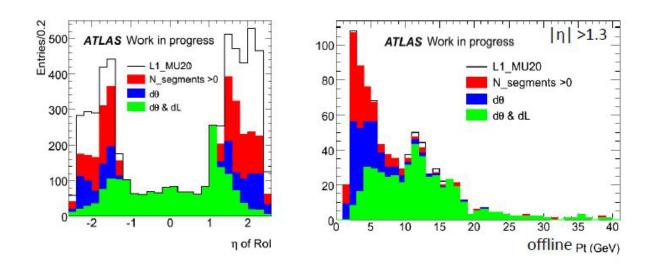

現状の問題は以下である。L1 ミューオントリガーで最も重要な L1\_MU20 を考える。これは  $p_{\rm T}$ 20 GeV 以上を判定する。2012 年時点では約 6 kHz である。しかしこのままでは Phase-1 で 割り当て 20 kHz を超えてしまう。図 2.20 は L1\_MU20 の  $\eta$  分布である。このように、本当の L1\_MU20 は全体の 2%しかない。残りの 98%はフェイクである。ほとんどが  $|\eta| > 1.0$  の Endcap TGC からきている。フェイクの原因は以下である。

- 別の荷電粒子別の荷電粒子が磁場に曲げられ、IP から来たように見えるものがある。高エネルギー中性子がビームパイプに当たり生成される陽子や、ビームハロー $^6$ がある。

- $p_T$ 20 GeV 以下のミューオン  $p_T$  分解能が悪く, 20 GeV 以上と誤ってしまうものもある.

$<sup>^6</sup>$ 陽子ビームがビームパイプ内残留ガスと弾性/非弾性散乱したり、ビーム同士が弾性衝突したりして生じる二次粒子.実験装置を横切るようにして通過する

図 2.20: L1\_MU20 の  $\eta$  分布 [16]. 98% が フェイクである.

図 2.21:  $d\theta$ , dL. これらが一定値以下になるようにカットをかける.

#### 2.4.1 Phase-0

Phase-0 では、現在用いられていない SW の TGC を用いる. この TGC (EI/FI) のヒットを要求することで、ビームパイプからくるフェイクを落とす. これにより頻度を約3割減らす. そこで EI/FI と BW のコインシデンスをとる. SL の  $R-\phi$  コインシデンスの後に行う. すでにファームウェアの開発 [21] は終わり、現在は BW と SW 間の遅延時間の調整中である.

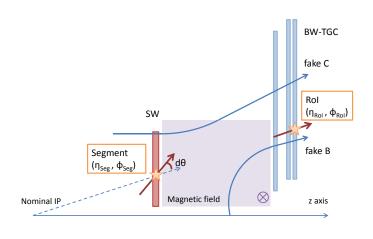

#### 2.4.2 Phase-1

Phase-1 では NewSmallWheel (NSW) を導入する. NSW のコインシデンスをとり, ビームパイプからの粒子を除く. さらに IP と NSW ヒットを結ぶ直線との角度の差  $d\theta$  を測り, IP からきていないミューオンやビームハローを除く. 1mrad 程度の角度分解能があれば良い. dL は以下の式で表す. 図 2.21 に  $d\theta$ , dL を示す. 手順は以下である.

$$dL = \sqrt{(\eta_{\text{RoI}} - \eta_{\text{Seg}})^2 + (\phi_{\text{RoI}} - \phi_{\text{Seg}})^2}$$

- 1. 全てのL1\_MU20のイベントに対して, NSW track を要求する (InnerSeg)

- 2. さらに  $d\theta$  が一定値以内であることを要求する ( $d\theta$  カット)

- 3. さらに dL が一定値以内であることを要求する (dL カット)

図 2.22 に  $d\theta$ , dL カットのシミュレーション結果を示す.  $d\theta$  は mrad 程度, dL は mm 程度でカットをかける低い  $p_{\rm T}$  は大幅に減り, 全体では 30% 程度まで落ちる. 効率は 96.6%程度と高い.

図 2.22:  $d\theta$ , dL カットのシミュレーション結果 [?]  $d\theta$  は mrad 程度, dL は mm 程度でカットをかける. 現状約 98% のフェイクを約 60% 落とす.

#### 2.4.3 Phase-2

Phase-2 では L0 が導入される. ここではミューオングループが導入を考えている Long L1 Buffer について紹介する. MDT のデータは L1 Buffer(L1B) と L1 Trigger Processor(L1TP) に分かれる. L1B は 1 kbit 程度で track 情報を用いたトリガー過程の間データを保持する. TGC/RPC のデータは同様に L1B と L0TP に分かれる. L0TP では迅速に L0A を判定する. これは BCID と RoI を含む. MDT の L1TP はこれを元に track 情報を生成し, L1A を判定する.

これに伴い, 電子装置を総取り換えする. L1 Buffer を USA15 に置く案がある. 放射線環境下の装置がを減らし, 維持管理しやすくする. また, 機能をまとめ装置数を減らす.

# 第3章 新SL

# 3.1 新SL 開発目的

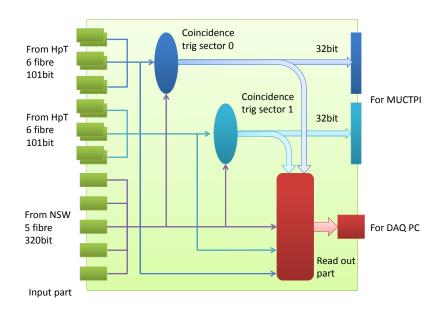

新 SL は phase-1 における SL のアップグレードである. NSW で IP を向く track と BW の RoI でコインシデンスをとる. 現行の HpT ボード入力に NSW 入力を追加する. このため SL ハードウェアのアップグレードが必要になる. 3.1 に 新 SL ブロック図を示す.

これに伴い読み出しもアップグレードする. 新 SL のトリガーの流れについては前章で述べた. このトリガーを開発するためにはまず読み出しを開通する必要がある. 現行の SL は PS ボード用の SLB ASIC と専用 SSW で読み出す. 新 SL では SLB ASIC の機能を新しい FPGA に組み込む. また FPGA TCP 技術 SiTCP と 市販の Switching Hub を用いる. これにより汎用性のある読み出しを構築する. 図 3.2 に SL と 新 SL の読み出しを示す.

# 3.2 新 SL 機能

新 SL の機能は入力部, コインシデンス部, 読み出し部である. 現 SL と同じ 2 トリガーセクターを受け持つ. このため 1 SL に 2 つのコインシデンス部と 1 つ入力, 読み出しがある.

# 3.2.1 新 SL 入力部

#### HpT 入力

まず従来の HpT 入力がある. これは G-link 光通信を用いる. EW-HpT からは High/Low- $p_{\rm T}$  を 7 track を受ける. 1 track 10 bit であり、7 track 70 bit を 4 fiber で受ける. 一方 ES-HpT からは High/Low- $p_{\rm T}$  を 4 track を受ける. 1 track 9 bit であり、4 track 36 bit を 2 fiber で受ける. G-link が 17 bit 幅なので、自明な bit を除き fiber 間で調整する. このためトリガーセクターあたり  $17\times5+16=101$ bit になる. 1 SL 2 トリガーセクターで 202 bit になる.

### NSW 入力

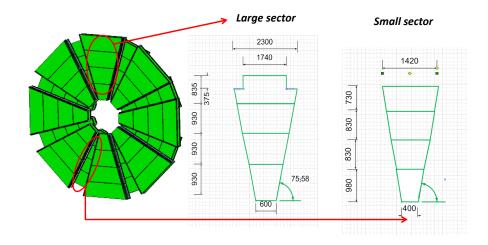

NSW はバレルトロイド磁石の配置から 8 回対称となる. コイル近くに 8 つの Small sector, その間に 8 つの Large sector となる. BW RoI に対して NSW RoI は広めにとる. 必要な広さは dL cut による. 1 つの NSW sector で足りるとは限らない. ここでは図 2.22 のオフライン解析の値 [16] に従う.  $d\eta$  が 0.07,  $d\phi$  が 0.06 で cut すると仮定する.  $\eta$  の 0.07 は BW RoI で 3 RoI,  $\phi$  の 0.06 は 2 RoI である. このため NSW RoI は隣の Small (Large) sector まで及ぶことがある. 3.3 に NSW 外観を示す. 3.3 に BW と NSW Large/Small sector の対応例を示す.

図 3.1: 新 SL ブロック図. 従来の HpT からの入力と新しく NSW からの入力がある.

図 3.2: SL と 新 SL の読み出し. 右は 新 SL で, 市販の Swithing Hub で収集できる.

図 3.3: NSW 外観 [10]. バレルトロイド磁石の配置から 8 回対称となる. コイル近くに 8 つの Small sector, その間に 8 つの Large sector となる.

この NSW のデータを光で USA15 の SL に送る. このとき以下を要求する.

- 角度分解能 1 mrad, dθ のために必要な最低限の分解能

- 40MHz で動作し, バンチごとのデータが前後しないこと

- 遅延時間は SL には 44 クロック以内に到達すること

SL は NSW の  $d\theta$ ,  $\eta$ ,  $\phi$  を受ける.  $d\theta$  については, 分解能 1 mrad で 15 mrad 程度のカットをかける [16]. この場合 4 bit と正負ビットの 5 bit でよい.

RoI ついては, NSW の精度による. 現在は R 8 bit,  $\phi$  6 bit で十分と言われている. これに TGC hit 2 bit, NSW hit 2 bit, 予約 1 bit を足す. 以上により 1 track 24 bit とする.

この track がいくつ必要か述べる. 1トリガーセクターから 2 High  $p_{\rm T}$  候補を出す.1/8 円中にトリガーセクターは 9 つなので 18 track になる. 1 fiber 4 track で, Large 12 track, Small 8 track とする. よって  $202+24\times4\times(2+3+3)=970$  bit が最大入力となる.

# 3.2.2 新 SL コインシデンス部

コインシデンス部は 2 つのトリガーセクターごとに用意する. 従来の  $R-\phi$  コインシデンスの後に NSW コインシデンスを追加する.  $\eta$  は  $\pm 3 {\rm RoI}$ ,  $\phi$  は  $\pm 2 {\rm RoI}$  に NSW track を要求する. 残った候補を Pre-selector, track selector で 2 つに絞り, encode して MUCTPI へ送る.

#### 3.2.3 新 SL 読み出し部

現在の SLB ASIC の仕組みを FPGA に組み込む. まず HpT からの入力が 2トリガーセクターで 202 bit ある. NSW の入力データは最大 8+12+12=32 track , 768 bit である. また, トリガーデータは 2トリガーセクターで 64 bit である. これらに BCID を付加し, L1 Buffer に格納する. BCID は SLB ASIC では 4 bit だが 新 SL では 12 bit にする. これで

図 3.4: BW と NSW Large/Small sector の対応例 [28]. large  $28^{\circ}$ , small  $17^{\circ}$  で  $360/8 = 45^{\circ}$ .

表 3.1: 新 SL 読み出しデータ. 入力が 970 と従来の約 5 倍になっている.

| L1A                 | BCR                  | input data        | trigger data     |  |  |  |

|---------------------|----------------------|-------------------|------------------|--|--|--|

| L1 count            | 1 count BC count Del |                   | coin. part       |  |  |  |

|                     | ↓ 12 bit             | ↓ 970 bit         | ↓ 64 bit         |  |  |  |

|                     | L1 Buffer (BCID)     | L1 Buffer (input) | L1 Buffer (trig) |  |  |  |

| $\Downarrow$ 12 bit | $\overline{\qquad}$  | <b>\</b>          | <b>#</b>         |  |  |  |

| Derandomizer        |                      |                   |                  |  |  |  |

| <b></b>             |                      |                   |                  |  |  |  |

|                     | Reado                | out Encoder       |                  |  |  |  |

202+768+64+12+12=1058bit になる. L1A が来たら L1ID 12 bit を付けて, 前後を加えた 3 バンチを derandomizer FIFO に渡す. 最後に SiTCP で読み出す. 最大約 317 Mbps なので 1 Gbps 以上の環境を用いる. 表 3.1 に新 SL 読み出しデータを示す.

# 3.3 新 SL 要求性能

- 入力 (202+768) × 40 MHz = 約 39 Gbps が可能であること

- メモリ 1058 bit × 2 k = 約 2000 kbit が可能であること

- 出力 1058 bit × 3 bunch × 100 kHz = 約 317 Mbps/SL が可能であること

# 第4章 PT7

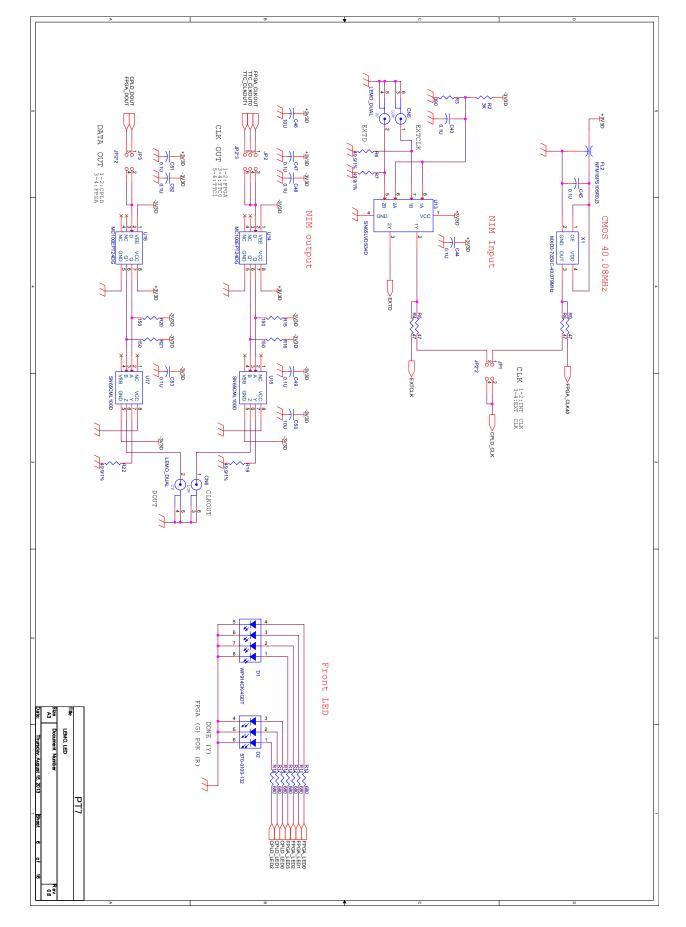

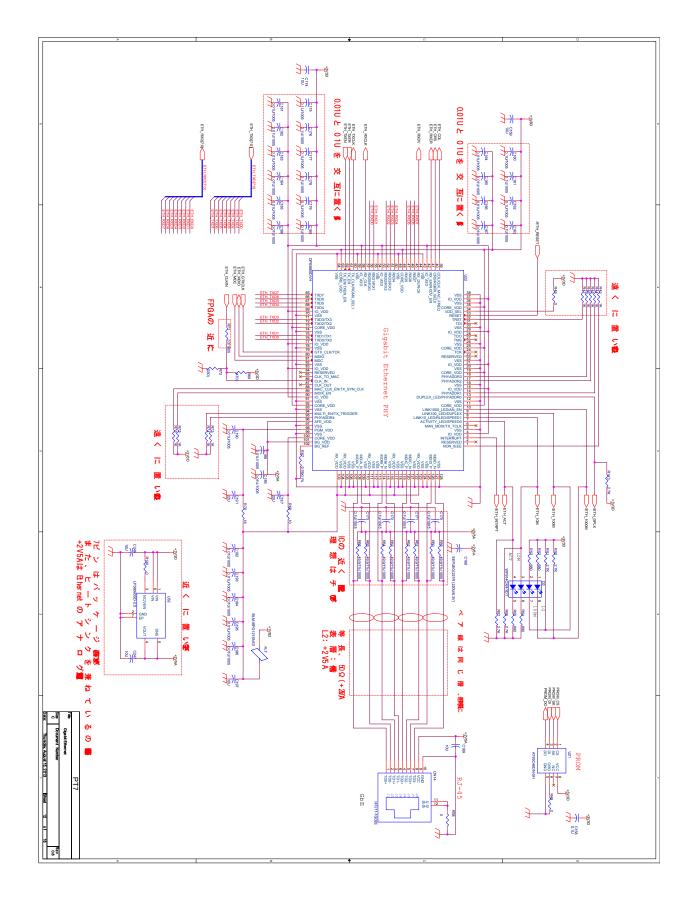

ProtoType7 (PT7) は本研究で開発した VME 装置である. 新 SL の試作機として 約 80 Gbps の大入力や TCP による出力を持つ. 汎用 VME 装置として NIM などにも対応する. 図 4.1 に PT7 を示す. 図 4.2 に PT7 のブロック図を示す.

# 4.1 PT7 構成

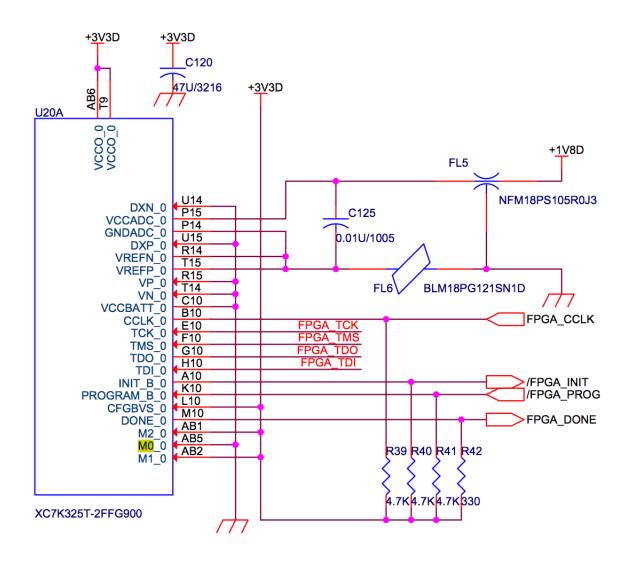

# 4.1.1 FPGA

FPGA は Xilinx の Kintex-7 FPGA XC7K325T-2FFG900 を採用した. 表 4.1 に Kintex-7 FPGA 性能比較 を示す. 325T は I/O が Kintex の中で最も多い. GTX を 16 lane のうち 8 lane を使用する. FFG900 では DDR3 SDRAM は 1333 MT/s, GTX は約 10 Gbps が可能である [35]. FFG676 ではピン数が足りない.

| 表 4.1: Kintex-7 FPGA 性能比較 [30]. XC7K325 | Tの採用が検討されている。 |

|-----------------------------------------|---------------|

|-----------------------------------------|---------------|

| device   | slice      | BRAM (Kb) | GTX | I/O bank | I/O |

|----------|------------|-----------|-----|----------|-----|

| XC7K160T | 25,350     | 11,700    | 8   | 8        | 400 |

| XC7K325T | 50,950     | 16,020    | 16  | 10       | 500 |

| XC7K410T | $63,\!550$ | 28,620    | 16  | 10       | 500 |

| XC7K420T | $65,\!150$ | 30,060    | 32  | 8        | 400 |

| XC7K480T | 74,650     | 34,380    | 32  | 8        | 400 |

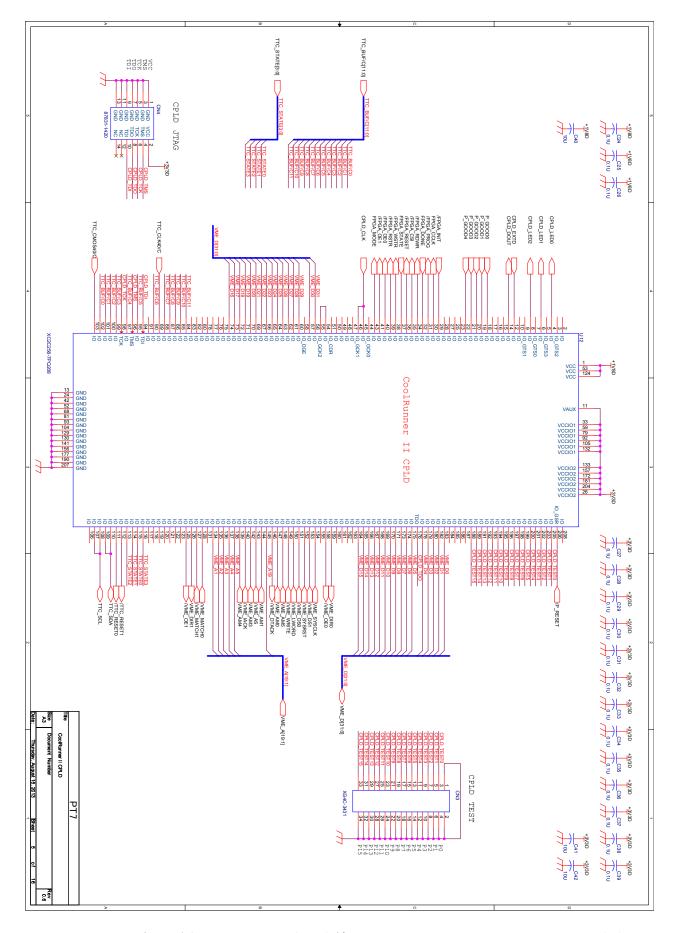

#### 4.1.2 CPLD

Xilinx の CoolRunner-II CPLD XC2C256-7PQ208 を採用した. これは TGC グループで長く使用されている.PT7 では不揮発性の CPLD で VME 制御と FPGA 書き込み をする. また TTCrq を I2C で制御する. Open collector 出力方式だが pull up 抵抗は TTCrq にある.

#### 4.1.3 Ethernet PHY

GbE のため、Texas Instruments 社の DP83865 Gig PHYTER を持つ.10BASE-T (Full/Half duplex), 100BASE-TX (Full/Half duplex), 1000BASE-T (Full/Half duplex) の6種に対応し、自動交渉機能で自動的に選択される. クロックは25 MHz と、1000BASE-T使用時には125 MHz を

図 4.1: PT7. 新 SL の試作機として 約 80 Gbps の大入力と TCP による出力を持つ.

図 4.2: PT7 ブロック図. 数字がバス幅で, 赤は VME のアドレス線, 青はデータ線である.

| 表 4.2: PT7v2 の クロック. PT7v2 では X3, X4 に関する |

|-------------------------------------------|

|-------------------------------------------|

|             | frequency                        | FPGA       | GTX     | CPLD       | NIM out          |

|-------------|----------------------------------|------------|---------|------------|------------------|

| X1          | 40 MHz                           | 0          |         | JP1        |                  |

| X2          | $125~\mathrm{MHz}~\mathrm{LVDS}$ | $\bigcirc$ |         |            |                  |

| X3          | 125 MHz LVDS                     |            | $\circ$ |            |                  |

| X4          | 200 MHz LVDS                     |            | $\circ$ |            |                  |

| VME sysclk  | $16~\mathrm{MHz}$                |            |         | $\bigcirc$ |                  |

| NIM in      |                                  | $\bigcirc$ |         | JP1        |                  |

| TTC cmos40  | $40~\mathrm{MHz}$                | $\bigcirc$ |         | $\bigcirc$ | $_{ m JP2}$      |

| TTC lvds160 | 160 MHz LVDS                     |            | $\circ$ |            |                  |

| TTC another | $40~\mathrm{MHz}$                | JP4        |         | JP4        | $JP4 \times JP2$ |

| FPGA nim    |                                  |            |         |            | JP2              |

FPGA からくべる. PHY の通信状態 LED を 4 つつけた. ACT, LINK, 100M (100BASE-TX) 1G(1000BASE-T) である.

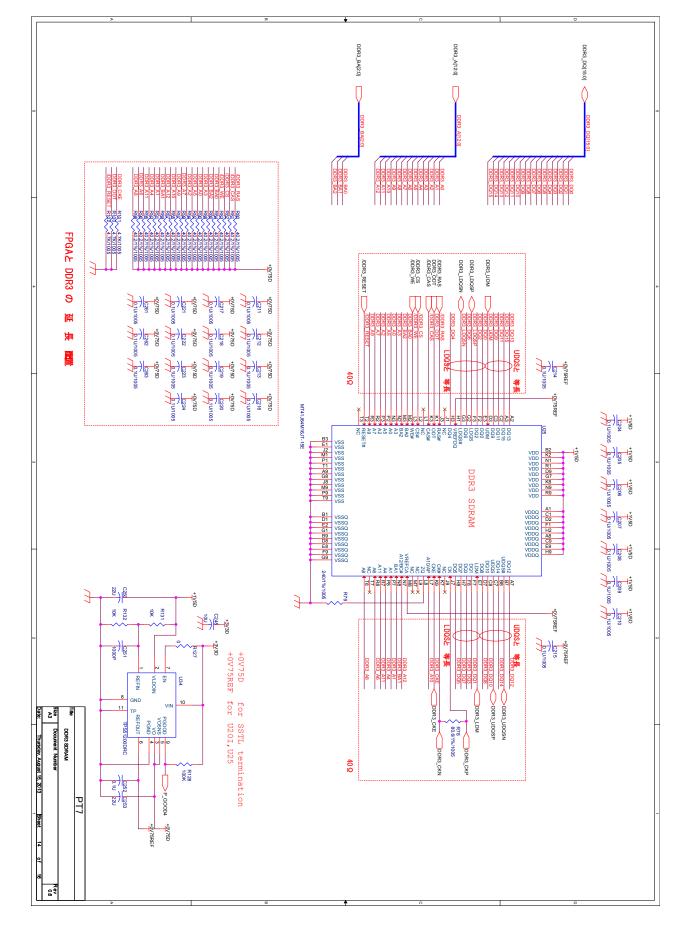

#### 4.1.4 DDR3 SDRAM

SDRAM として micron 社の MT41J64M16JT-15E を持つ. DDR3-1333 で $^1$ 型であり, 667 MHz まで対応できる. 16bit 幅 1333MT/s × 16 = 21.3Gbps で読み書きができる. 実際は, 125 MHz を 5 逓倍して 625 MHz とし, 最大約 20 Gbps で用いる.

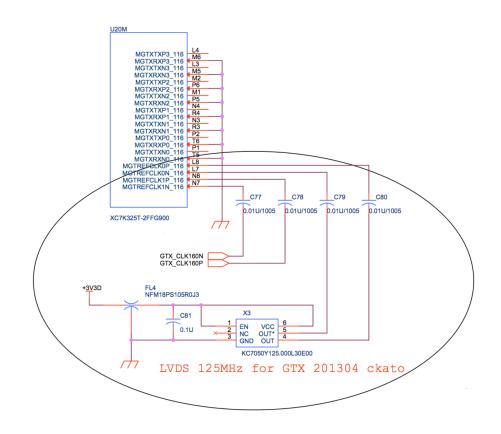

#### 4.1.5 Clock

表 4.2 に PT7v2 のクロックを示す. ○ は直接または fan-out してくべたものである. JP は jumper pin 番号である. これで接続を選ぶ. X1~X3 は水晶発振器である. X1 は LHC と同じ 40 MHz である. X2 は SiTCP に用いる. X3 は GTX に用いる. X4 は DDR3 に用いる. TTC からは 5 種類のクロックを受け取る. cmos40 が実際に用いられる. lvds160 はこれを 4 倍したものである. これを GTX の 2 つ目のクロックとする. another は残りの 3 種類を JP4 で選ぶ.

# 4.2 PT7 入出力

### 4.2.1 Multi Gigabit Transceiver

1 lane 10 Gbps の 高速シリアル送受信機 GTX を 8 lane 用いる. 4 lane ずつ Infiniband 4x コネクタ (図??) と接続する. 図??に Infiniband 4x コネクタ を示す. 2 つのコネクタがフロントパネルにある. 今回採用した Infiniband cable (図 4.4) には 9 本のグラウンド線と 16 本のシグナル線がある. 1 本で 4 lane の Full duplex が可能である. Infiniband DDR (double data rate: 5 Gbps) で,  $5 \times 4 = 20$ Gbps が可能である.

<sup>&</sup>lt;sup>1</sup>Double Data Rate 3: 1 クロックで 8 ワード読み書きできる. 数字は転送速度 (MT/s)

図 4.3: Mellanox CTMC1104130. 1本で 4 lane の Full duplex が可能.

図 4.5: G-Link 送受信カード. PT7 に接続可能.

図 4.4: 日本航空電子社 DG1R025HS8E250. Infiniband 4x コネクタ.

図 4.6: LVDS 送受信カード. PT7 に接続可能.

### 4.2.2 Gigabit Ethernet

FPGA は Gigabit Media Independent Interface (GMII)/Media Independent Interface (MII) を介して PHY と接続した. PHY は Medium Dependent InterfacI (MDi) を介して HALO Electronics HFJ11-1G02E コネクタと接続し、アナログ信号を送受信する.

#### 4.2.3 メザニンカード

Common Mezzanine Card (CMC) 規格準拠のメザニンカード用コネクタを 1 組持つ. 既存の G-Link 送受信カードや S-Link 送信カード, LVDS 送受信カードが使える. G-Link 送受信カードは HDMP-1032/1034 チップを持つ. G-Link 送受信カードは SN65LV1023ADB/ 1224BDB チップを持つ. 図 4.5 に G-Link 送受信カードを示す. 図 4.6 に LVDS カードを示す.

## 4.2.4 TTCrq コネクタ

ATLAS では TTC によりクロックやトリガー信号を配る. TTC 信号は光で送られ, TTCrq で受信解読する. TGC フロントエンドでは TTC 信号のうちクロック, L1A, ECR, BCR をフラットケーブルで配る. PT7 はこの TTCrq を直接載せて TTC を全て読み出すことが出来る. ただし取り付け位置がメザニンカードと重なるため, 同時に一方しか使えない. 図 4.7 に TTCrq を示す.

#### 4.2.5 その他

• NIM

図 4.7: TTCrq. TTC 信号を受信する. PT7 に接続可能.

高エネルギー実験で使用される NIM 信号の送受信が可能である. フロントパネルに LEMO コネクタが 4 つあり, 2 つが入力, 2 つが出力である. クロックやトリガーの入出力ができる.

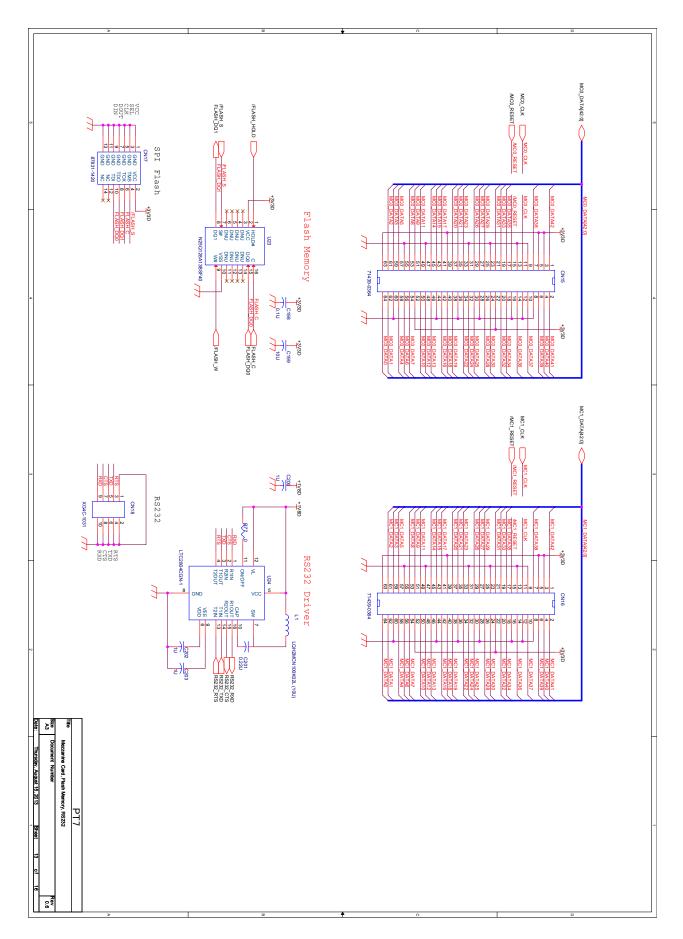

#### • RS232C

低速のシリアル通信規格である RS232C の信号を 10 ピンのボックスピンヘッダから出す. これらは Linear Technology 社の LTC2804 により送受信される. FPGA に組み込み CPU を載せた場合のコンソール等に用いる.

#### • JTAGピン

FPGA, CPLD 書き込み 用にそれぞれ JTAG ピンヘッダを持つ. Xilinx 社製の USB-JTAG ケーブルを使用可能. また Flash memory のために, 同じピンヘッダをもう 1 つ持つ.

#### • テストピン

CPLD と FPGA はともに 16 ピンのボックスピンヘッダを持つ. デバッグに用いる.

# 4.3 PT7 動作確認

2013年5月から7月にかけて PT7v1 の動作確認を行った. 以下の項目を確認した. 結果をもとに回路と基板を修正し, 2013年8月 PT7v2 を発注した.

#### • CPLD

JTAG による configuration VME による register 読み書き Test Pin NIM LED

#### • FPGA

JTAG による configuration

VME CPLD による configuration

VME による register 読み書き

Test Pin

NIM

LED

XADC

Microblaze RS232

DDR3

GTX IBERT 10 Gbps/ lane

SPI Flash PROM configuration

#### • Gigabit Ethernet

SiTCP default 読み書き SiTCP PROM 読み書き SiTCP none default 読み書き LED

• Mezzanine Card G-Link tx rx

#### 4.3.1 電源

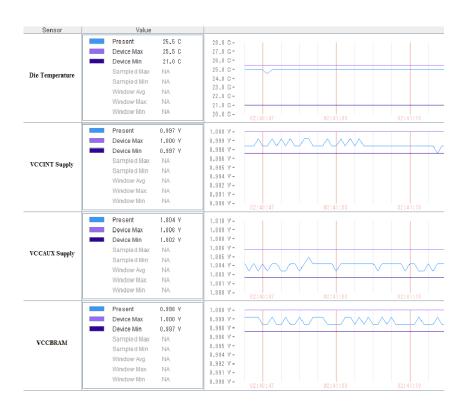

2013 年 2 月 PT7v1 の電源装置のひとつ U26 LMZ10505 の監視信号が立たない問題があった. LMZ10505 は 5 V から 3.3 V を供給する. 図?? に電源装置 U26 LMZ10505 を示す. 今回は R112 の抵抗が間違っていた. 2013 年 3 月に KEK で交換し解決した. また 2014 年 2 月 PTv2 10 台中 2 台で電源の監視信号が揃わなかった. これは監視電圧を分配する抵抗の精度が数%程度だったことによる. 監視電圧の閾値の約 4% 上になるように設定されていた. この抵抗を交換し監視信号を確認した. また XADC を JTAG で読み出し FPGA での正確な電源を確認した. 図 4.8 に PT7v2 XADC 結果を示す. 今回監視信号の立たなかった VCCINT は FPGA の要求 0.97 -1.03 V を満たし 0.997 -1.000 V だった.

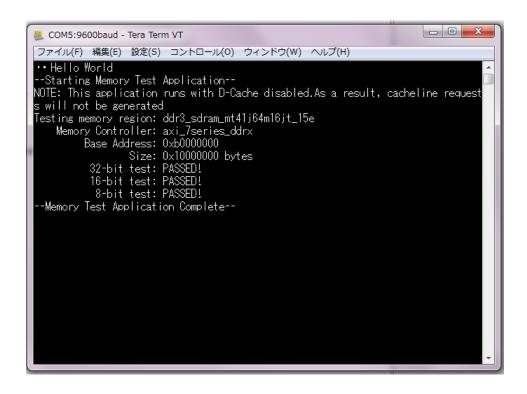

#### 4.3.2 DDR3 SDRAM

DDR3 の制御は大規模で高速のため FPGA の設計に時間がかかる. 2013 年 6 月 7 月にデバッグした. 最終的に GbE 用の 125 MHz clock を 200 MHz に積み替えて動作確認した. 参照 clock

図 4.8: PT7v2 XADC 結果. VCCINT は FPGA の要求 0.97 -1.03 V を満たし 0.997 - 1.000 V.

の扱いが難しく外付けの 200 MHz が望ましい. PLL を設定することもできるが実用上不便である.[37] 高速入出力 bank の設計や制約も詳細な知識が必要になる. 2013 年 11 月以降は FPGA 組み込み CPU Microblaze を利用して動作確認を行っている. PT7v2 では新しく追加した 200 MHz clock を用いている. 図 4.9 に PT7v2 DDR3 Memory Test 結果を示す.

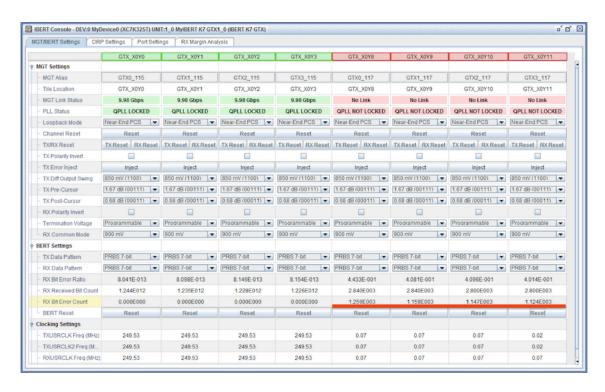

#### 4.3.3 GTX IBERT

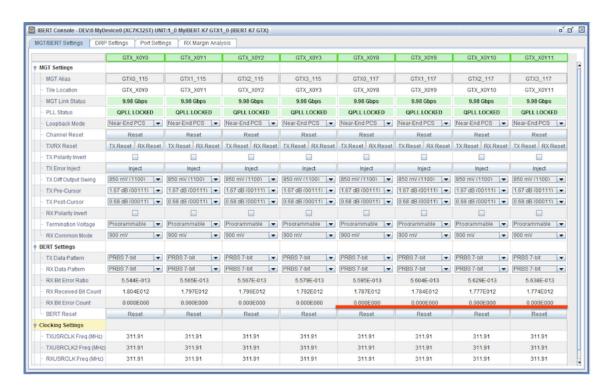

Integrated Bit Error Ratio Tester (IBERT) は Pseudo-Random Bit Sequence (PRBS) を用いて Bit Error Rate (BER) を測る. 本研究では回路基板の確認に用いた. 以下は near end pcs 内部 loop back で, bank 115 4 lane bank 117 4 lane の 10 Gbps での BER を測定した.

Xilinx の Chipscope という技術では、IBERT などの IP と対応するソフトウェアがある. これにより JTAG 経由で内部信号を診断する. 図 4.10、図 4.11 はその様子である.

PT7v2 では基準クロック配線の修正により bank117 が使えることを確認した. infiiniband 1m で loop back した場合も BER  $10^{-13}$  であり, 回路基板には問題がないことを確認した.

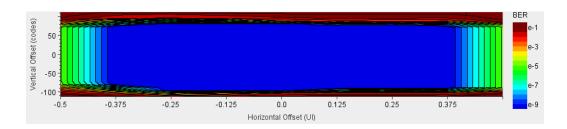

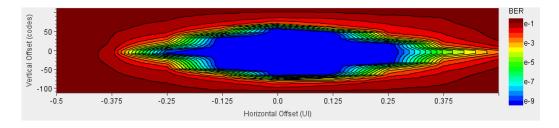

また統計的アイパターンを測定した. サンプリング時に縦軸に電圧, 横軸に時間のオフセットをつけて BER を測った. 1 codes: 約 7.3 mV, 1UI: 約 0.1 ns である. 図 4.12, 図 4.13 に結果を示す. 5Gbps では長方形に近い形で余裕がある. 10 Gbps では菱形に近い形になる. 今回は Infiniband 1m を用いたが, 10Gbps ではケーブル長や接続の回数での減衰が予想される.[17] 光接続の場合はケーブル長による減衰はより少ないことが知られている.

図 4.9: PT7v2 DDR3 Memory Test 結果. 新しく追加した 200 MHz clock を用いている.

図 4.10: PT7v1 GTX IBERT. 基準クロックが届かず赤線部 bank117 が bit error.

図 4.11: PT7v2 GTX IBERT. 基準クロックが届き赤線部 bank117 が error count 0.

図 4.12: PT7v2 GTX 5Gbps IBERT EYE. 5Gbps では長方形に近い形で余裕がある.

図 4.13: PT7v2 GTX 10Gbps IBERT EYE. 10 Gbps では菱形に近い形になる.

# 第5章 PT7 性能評価

## 5.1 PT7 性能評価 目標

PT7 を用いて新 SL の FPGA 読み出しを開発する. 具体的には FPGA に以下を実装する. 読み出し開発と性能評価を段階的に進め, 十分な性能が出るか確認した. 図 5.1 に PT7 を用いた 新 SL FPGA 読み出し 目標を示す.

- 高速シリアル転送 GTX で 新 SL 最大入力約 38.8 Gbps を再現する

- Bunch Count 12 bit, Event Count 12 bit, 仮の trigger 情報 64 bit を足す

- L1Buffer を意図する buffer で L1A 判定を待つ

- L1A が出たものは次の FIFO に書き込む

- FIFO で L1A のばらつきを吸収しつつ出力幅を 8 bit にする

- ZeroSuppress で全て 0 の 8 bit を捨てる

- SiTCP で最大 317 Mbps を読み出す

図 5.1: PT7 を用いた 新 SL FPGA 読み出し 目標. これを実装し十分な性能が出るか調べる.

# 5.2 PT7 SiTCP 性能評価試験

2013 年 8 月, 12 月に行った PT7 SiTCP 性能評価試験について述べる.

図 5.2: PT7 SiTCP 性能評価試験 環境. 白いケーブルは cat6 3m, 青は 100BASE-TX 用 1m.

#### 5.2.1 PT7 SiTCP 性能評価試験 内容

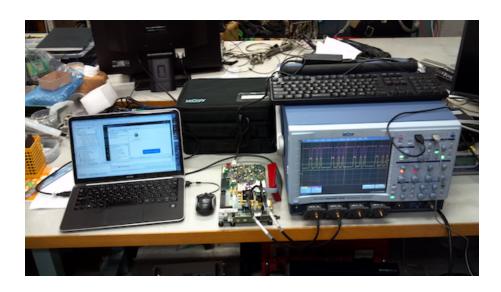

PT7 に実装した SiTCP の最大転送速度を測る. SiTCP と同じ 150 MHz で 8 bit の counter data をくべた. 1000BASE-T と 100BASE-TX で測定した. 3 台の PT7 と Switching Hub を用いて拡張性を確認した. 図 5.2 に PT7 SiTCP 性能評価試験 環境 を示す.

• Switching Hub

Corega CO-BSW16GTX

Port: 10/100/1000BASE-T×16

• LAN cable

Cat.6 3 m 白 100BASE-TX 用 1 m 青

PC

DELL PRECISION T3500

CPU: Intel Xeon W3565 @3.2GHz

Memory: DDR3-1333 24GB

OS: Scientific Linux CERN release 5.8

Network Interface Card: Broadcom BCM5761

### 5.2.2 PT7 SiTCP 性能評価試験 結果

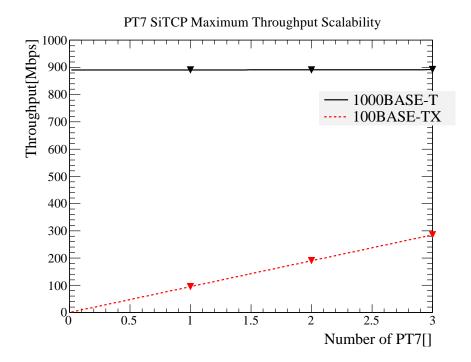

図 5.1 に PT7 SiTCP 単体の最大転送速度, 図 5.3 に PT7 SiTCP 最大転送速度 拡張性 を示す. まず, 実行転送速度は最大で帯域の約 95% になる. 最大データ 1460 Byte に対して, Ethernet TCP/IP のヘッダーが 76 Byte つくからである. 100BASE-TX では, 100 Mbps のうち 95 Mbps と予想通りである. 1000BASE-T では, 1 Gbps のうち 891 Mbps と 95% を下回っている. これは PC 側の限界と考える.

表 5.1: PT7 SiTCP 単体の最大転送速度. まず, 実行転送速度は最大で帯域の約 95% になる. 最大 データ 1460 Byte に対して, Ethernet TCP/IP のヘッダーが 76 Byte つくからである. 100BASE-TX では, 100 Mbps のうち 95 Mbps と予想通りである. 1000BASE-T では, 1 Gbps のうち 891 Mbps と 95% を下回っている. これは PC 側の限界と考える.

|                   | 1000BASE-T | 100BASE-TX |

|-------------------|------------|------------|

| Throughput[ Mbps] | 891        | 95         |

図 5.3: PT7 SiTCP 最大転送速度 拡張性. 100BASE-TX は予想通り比例しているが, 1000BASE-T は比例しない. この 891bps が現状の上限となる.

また, PT7 3 台を用いて最大転送速度の拡張性を確認した. 100BASE-TX は予想通り比例しているが, 1000BASE-T は比例しない. この 891bps が現状の上限となる.

### 5.2.3 PT7 SiTCP 性能評価試験 結論

PT7 SiTCP は 新 SL の出力要求最大 317Mbps に対して 891Mbps 可能である. また Switching Hub で収集できる. 891 Mbps は PC 側の限界なので, 設定や 10Gbps 環境で拡張出来る.

# 5.3 PT7 TTC 接続試験

2013年8月にCERNで行ったPT7v1 TTC接続試験について述べる.

図 5.4: PT7 TTC 接続試験 環境. オレンジのケーブルが TTC 装置からの光信号を運ぶ.

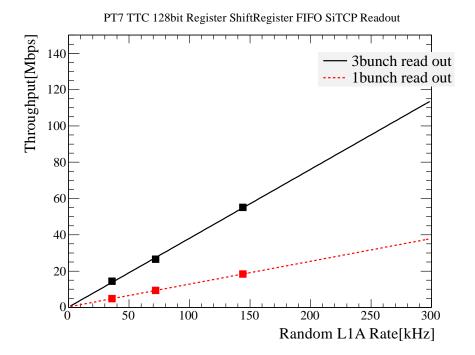

#### 5.3.1 PT7 TTC 接続試験 内容

PT7v1 では GTX が使えなかった. そこで新検出器入力を意図した 128 bit register を用意し、Shiftregister FIFO SiTCP の順に読み出した. Shiftregister は TTC からの 40 MHz に同期し、それ以降は 150 MHz で動かした. FIFO の書き込み許可は TTC random L1A と前段後段の ready とした. L1A の頻度を変えて読み出し量を測定した. SiTCP の前段の FIFO ではデータ幅を 8 bit にする必要がある. 今回は 2 段の FIFO を用いて幅を 128, 32, 8 とした. このときデータが意図通りの順番で読み出されるか確かめた. 図 5.4 に PT7 TTC 接続試験 環境 を示す.

### 5.3.2 PT7 TTC 接続試験 結果

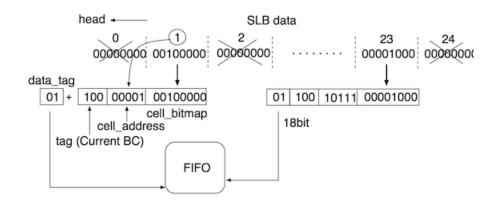

図 5.5 に PT7 TTC 接続試験 読み出し量と L1A 頻度を示す. 以下は読み出したデータの例である. 図 5.6 は現在検討されている NSW データ形式である. 意図した通りの順番で register と counter が読み出されている.

4A 31 33 33 33 22 22 22 11 11 11 00 00 00 CC CC 4A 32 33 33 33 22 22 22 11 11 11 00 00 00 CC CC 4A 33 33 33 32 22 22 21 11 11 11 00 00 00 CC CC

#### 5.3.3 PT7 TTC 接続試験 結論

L1A の頻度に対して予想通り L1A 頻度 x データ幅の値が得られた. 2段の FIFO で幅を変更した場合も, データは意図した順番通り読み出せた. PT7 は TTCrq で LHC 40 MHz clock と L1A を受信可能である. 従来の SLB ASIC を FPGA に組み込み可能である.

図 5.5: PT7 TTC 接続試験 読み出し量と L1A 頻度. 予想通りの読み出し量が得られた.

Field: TGC hit MM hit d $\theta$  (mrad)  $\phi$  index R index rsv Num of bits: 2 2 5 6 8 1

Max. number of tracks per a NSW sector is 8.

| Data Format from NSW to Sector Logic |            |      |               |  |  |

|--------------------------------------|------------|------|---------------|--|--|

| Words (16-bit)                       | first      | byte | second byte   |  |  |

| Word-0                               | con        | nma  | comma         |  |  |

| Word-1                               |            | trac | :k−0          |  |  |

| Word-2                               |            |      |               |  |  |

| Word-3                               | track-1    |      |               |  |  |

| Word-4                               | track-2    |      |               |  |  |

| Word-5                               |            |      |               |  |  |

| Word-6                               | track-3    |      |               |  |  |

| Word-7                               | ID (4-bit) |      | BCID (12-bit) |  |  |

図 5.6: 現在検討されている NSW データ形式. 1 track 24 bit を並べ, comma や BCID をつける.

図 5.7: PT7 GTX 接続試験 環境. 左の PT7 から 右の PT7 へ GTX を送信し TCP で確認した.

# 5.4 PT7 GTX 接続試験

2013年11月に行ったPT7v2のGTXと後段の接続試験について述べる.この試験では初めてPT7のFPGA読み出しが貫通した.しかしまだGTXの転送方式や高周波補償の制御が不十分である.現在,結果をもとに修正を続けている.

#### 5.4.1 PT7 GTX 接続試験 内容

PT7v2 の GTX と後段の読み出しを接続しデータが正しく読み出されるか確認した. 2 台の PT7v2 を用いて 1 台を GTX 送信,もう 1 台を GTX 受信にして読み出した. 図 5.7 に PT7 GTX 接続試験 環境を示す. 東京大学には TTC 環境がないため, PT7 の 40 MHz clock を代用した. これを 100 kHz に分周した clock で L1A を再現した. Shift-register は 40 MHz, FIFO SiTCP は 150 MHz で駆動した. 主な GTX の設定は以下のようにした.

• txdata width: 16 bit

• rxdata width: 16 bit

• line rate: 1.25 Gbps

#### 5.4.2 PT7 GTX 接続試験 結果

図 5.7 左側の PT7 で送信したデータは以下である.

$00\ 00\ 11\ 11\ 22\ 22\ 33\ 33\ 44\ 44\ 55\ 55\ 66\ 66\ 77\ 77$

00 00 11 11 22 22 33 33 44 44 55 55 66 66 77 77

00 00 11 11 22 22 33 33 44 44 55 55 66 66 77 77

図 5.7 右側の PT7 で受信したデータは以下である.

AA AA 46 D6 44 44 CC CC 88 88 55 55 66 66 77 77 AA AA 65 64 CC 4C CC CC 88 88 55 55 66 66 77 77 AA AA 56 45 CC CC CC CC 88 88 55 55 66 66 77 77

#### 5.4.3 PT7 GTX 接続試験 結論

GTX を利用するためには以下の問題を解決する必要がある.

#### • 頭出し

この例では TX RX ともに 8b10b をしていない. start from scratch という方式を用いている. この場合, 受信データの頭出しをユーザーが制御する必要がある. 例えば 4(0100) が 8(1000) になってしまった場合 1 bit 左に slide する. 現状ではこれが出来ていない.

#### • DC バランス

また, 8b10b をしない場合, 0000 や fff は最も DC バランスが偏る. 0000 が AAAA に化けたのはこのためと考える. ケーブルを抜いた状態の rx の信号は AAAA や 5555 である.

#### • 高周波補償

0000 の隣の 1111 の lane も壊れている. 隣の lane からの影響を受けている可能性がある. 高速シリアルの受信では、高周波の補償も重要になる.

### • 8b10b

8b10b は現在の高速シリアル伝送方式の主流である. これを用いた場合データが正しく decode されなかった. 特に本番の新 SL で光接続を使うので 8b10b の DC バランスは必須になる. 8b10b の decode を制御する必要がある.

#### 8b10b

8b10b は IBM が開発した高速シリアル転送方式である. 8 bit を 10 bit に変換して転送する. データの中にクロックを埋め込む. 0 か 1 の連続は 3 クロック以下になる. 表 5.2 に Xilinx 7 Series GTX 8b10b table の例を示す.

8b10b は変換表で行われる.表 5.2. 8 bit を 3 bit と 5 bit にわけ, それぞれ 1 bit 足して 6 bit と 4 bit にする. それぞれ 32 pattern と 8 pattern である. 00 から FF までは D00.0 から D32.7 までに対応する. さらに各 D は  $\pm$  2 種類ある. これを  $RD(Running\ Disparity)$  と呼ぶ. 直前の RD の逆を送る. これにより 0.1 を連続させない. K は制御用である.

図 5.8: Kintex-7 評価ボード KC705 を用いた GTX SMA 波形確認 環境. SMA P/N をみた.

表 5.2: Xilinx 7 Series GTX 8b10b table の例 [35]. 8 bit を 10 bit に変換して転送する.

| Name  | words | bits      | Current RD - | Current RD + |

|-------|-------|-----------|--------------|--------------|

| D16.1 | 30    | 001 1000  | 0110111001   | 100100 1001  |

| D18.0 | 12    | 000 10010 | 010011 1011  | 010011 0100  |

| D27.7 | fb    | 111 11011 | 110110 0001  | 001001 1110  |

| K27.7 | fb    | 111 11011 | 110110 1000  | 001001 0111  |

| D31.1 | 3f    | 001 1111  | 101011 1011  | 010100 1001  |

| D28.5 | bc    | 101 11100 | 001111 1010  | 001110 1010  |

| K28.5 | bc    | 101 11100 | 001111 1010  | 110000 0101  |

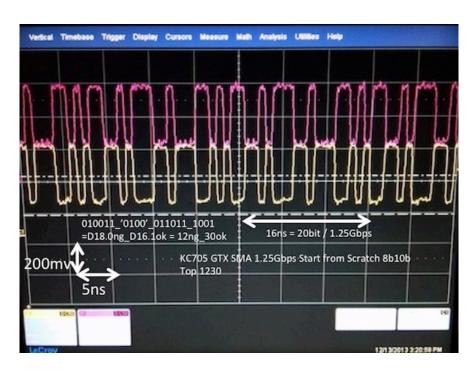

# 5.5 Kintex-7 評価ボード KC705 を用いた GTX SMA 波形確認

### 5.5.1 Kintex-7 評価ボード KC705 を用いた GTX SMA 波形確認 内容

PT7 GTX 制御の修正のため Kintex-7 評価ボード KC705 SMA 1lane 1.25 Gbps の波形をみた. LeCroy Wave Master 8420A 4GHz osciloscope Quad 20GS/s を用いた. 矩形波を見るためには約 4 倍の帯域幅が必要であり, sampling rate はさらにその 4 倍必要である. 図 5.8 に Kintex-7 評価ボード KC705 を用いた GTX SMA 波形確認 環境を示す.

#### 5.5.2 Kintex-7 評価ボード KC705 を用いた GTX SMA 波形確認 結果

図 5.98b10b なしの波形を示す. 周期は 12.8ns でデータも正常である. 図 5.10 に 8b10b ありの 波形を示す. 周期は 16ns で変換データも正常である.

図 5.9: 8b10b なしの波形. 周期は 12.8ns でデータも正常.

図 5.10: 8b10b ありの波形. 周期は 16ns で変換データも正常.

# 5.5.3 Kintex-7 評価ボード KC705 を用いた GTX SMA 波形確認 結論 GTX を利用するためには以下の問題を解決する必要がある.

#### 8b10b なし

FPGA 設計の最上階層でデータをくべた場合 tx は正常である. あとは rx の頭出しの制御である. Start from Scratch であれば slide, その他であれば comma align などである. Xilinx が提供する IP Core Generator の設計例に Frame generator と Frame checker という機能部分がある. これらは slide や comma align を制御をしつつデータを流し Bit Error を数える. 今回これを利用して Frame generator のなかでデータをくべた. しかし reset word が送出され続けた. この Frame generator の初期化過程を理解し, 利用することが課題である.

#### 8b10b あり

これも FPGA 設計の最上階層でデータをくべた場合 tx は正常である. 8b10b の変換については表 5.2 と合致している. rx 側の decode や初期化が課題である.

# 5.6 PT7 GTX FPGA 温度測定

#### 5.6.1 PT7 GTX FPGA 温度測定 内容

KC705 は 85'C 以下の運用を推奨している. KC705 は FPGA 冷却用のファンを持つが PT7 はない. PT7 で GTX などの高速信号を扱った際の温度上昇を確認する必要があった. 今回は GTX を 8lane 駆動し line rate を 10 Gbps まで上げながら FPGA 温度を測定した. VME crate の中の PT7, VME Extender の PT7, KC705 を比較した. 設定を変えてから 10 分経過した後の値を記録した. 2013 年 11 月 28 日に東京大学理学部旧 1 号館 434 室で測定した. この日の東京の平均気温は 14°C, 湿度 43%であった. 室内の温度は測定の初期値から約 24°C とわかる.

#### 5.6.2 PT7 GTX FPGA 温度測定 結果

図 5.11 に PT7 と KC705 の GTX 使用時の温度上昇を示す. KC705 は 10 Gbps でも 40°C 以下に保つことができた. PT7 は VME Extender の場合 10 Gbps では約 60°C まで上昇した.

#### 5.6.3 PT7 GTX FPGA 温度測定 結論

VME にはファンがあるが、気温が高い環境や装置が密集した場合には注意が必要である. 放熱板の導入を検討する. FPGA のサイズに合わせて  $31~\text{mm} \times 31~\text{mm}$  のクリップタイプを用いる. Advanced Thermal Solutions の ATS-53310D-C2-R0 が候補である.  $500\text{LFM}^{-1}$  で 6.3~C/W の 熱抵抗を持つ.図 5.12 に検討中の放熱板 ATS-53310D-C2-R0 を示す.

<sup>&</sup>lt;sup>1</sup>Linear Feet per Minute. 200LFM = 1m/s

図 5.11: PT7 と KC705 の GTX 使用時の温度上昇. KC705 は 10 Gbps でも 40°C 以下に保つことができた. PT7 は VME Extender の場合 10 Gbps では約 60°C まで上昇した.

図 5.12: 検討中の放熱板 ATS-53310D-C2-R0. 500LFM <sup>2</sup> で 6.3 ℃/W の熱抵抗を持つ.

# 第6章 新SL 設計

PT7 の開発を経て, 新 SL を設計する. 試験と修正を重ね, 量産, 導入する. 現時点で 新 SL の基板と FPGA の設計に関して言えることを述べる. [33] [32] [35] などを参考にする.

# 6.1 メモリ資源の選定

#### 6.1.1 資源と型

メモリ資源としては DDR3 SDRAM, Distributed RAM, Block RAM (BRAM) がある. 表 6.1 に FPGA 設計とおよその slice 数を示す. DDR3 は外付けで高速大容量であるが制御が複雑で約5400 slice 必要になる. FPGA 組み込み CPU Microblaze を用いた場合さらに約5000 slice 必要である. slice は FPGA の論理を実装する資源である. Distributed RAM は FPGA の slice を消費する. 約1/3 の slice が Distributed RAM として利用可能である. 今回の XCK325T では 最大で16000 slice を消費して4000 kbit 可能である. BRAM の場合は FPGA の slice を消費しない. 最大1024 bit 幅500 MHz まで可能である. 今回の XCK325T では BRAM 36Kb x 445 = 16020 kbit ある. 以上を踏まえ,まず全てBRAM で実装する.

表 6.1: FPGA 設計とおよその slice 数. 新 SL のメモリ資源を選定する際に参考にした.

|                              | size(kbit) | slice      |

|------------------------------|------------|------------|

| DDR3 SDRAM                   | 1000000    | 5400       |

| Block RAM                    | 16020      | 0          |

| Distributed RAM              | 4000       | 16000      |

| 新 SL GTX logic               | -          | 6201       |

| 新 SL Memory                  | 2000       | BRAM の場合 0 |

| 新 SL SiTCP logic             | -          | 2000       |

| 新 SL Kintex-7 XCK325T        | -          | 50950      |

| SL Forward Virtex-E XCV1000E | -          | 5120       |

| SL Endcap Virtex-E XCV3000E  | -          | 14336      |

| SL Forward logic             | -          | 4375       |

| 新 SL Forward logic           | -          | 15000      |

| SL Endcap logic              | -          | 10000      |

| 新 SL Endcap logic            | -          | 30000      |

|                              |            |            |

次に BRAM の使い方について述べる. SiTCP の前段では 8 bit の FIFO を用意する必要がある. SiTCP 前の FIFO は読み書き非同期で幅が可変な BRAM を使う. L1 Buffer は同期で幅も変えないので Shiftregister でも良い. Xilinx では Shiftregister が推奨されている. 最も簡単でタイミングも確実だからである [38]. しかし実際の運用では動作中に深さを調整する. その場合, FIFO が最も設計しやすい. 読み出し許可までの時間を register で制御する. VME や UDP で読み書き出来るようにする. 以上を踏まえ, まず全て FIFO で実装する.

#### 6.1.2 実装

現在目標とするメモリの実装について述べる。まず FIFO を 2 つ組む. 1 つは L1A を待つための L1Buffer である。もう 1 つは L1A のばらつきを吸収する Derandomizer である。L1Buffer は出力と入力の幅が同じ FIFO で組む。読み出し許可までの時間を register で制御する。L1A のときは Derandomizer への書き込みを許可する。Derandomizer は複数用意する。ひとつの FIFO では 1/8 までしか幅を変更できない。複数の FIFO を用いて SiTCP の 8 bit にする。

2013 年 12 月の試験では FIFO, Derandomizer 3 つ全て深さ 128 bit で試験した. 1024 bit 圧縮無しで 3 bunch 読み出し, どの FIFO も busy にならないことを確認した. この試験では L1A の代わりに PT7 40 MHz を分周した 100 kHz を用いた. そのため SiTCP 入出力は以下になる. 1024 bit x  $3 \times 100$  kHz = 307.2 Mbps. 8 bit  $\times 150$  MHz = 1200 Mbps. 実際の最大出力は約 891 Mbps. FIFO の深さは 128/8 + 128/32 + 128/128 = 21 に相当する. さらに 3 bunch 読み出しなので深さ 7 に相当する. ここでは L1A が規則的に 100 kHz なので 307.2 Mbps  $\le 891$  Mbps で十分である.

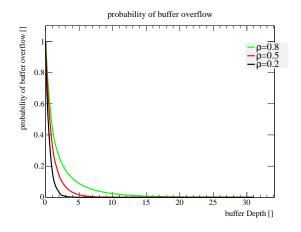

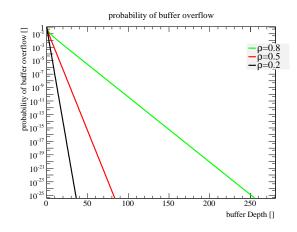

### 6.1.3 busy 確率

実際の FIFO に必要な深さは、待ち行列理論で考える。 実際は L1A が不規則にくるからである。 実際の L1A の間隔は最低 3 bunch あく. ここではマルコフ過程を仮定する. つまり入力と処理 の状態が持続する確率が過去の状態に依存しないとする. M/M/1/K 系,マルコフ過程で窓口が 1つ、深さ K を考える.

入力を $\lambda$ , 処理能力を $\mu$ とすると平均使用率 $\rho$  は以下である.

$$\rho = \frac{\lambda}{\mu}$$

深さKが満たされる確率 (輻輳確率) $P_K$ は以下である.

$$P_K = \frac{(1 - \rho)\rho^K}{1 - \rho^{K+1}}$$

$\rho$  は圧縮や後段の収集系による.  $P_K$  は図 6.1, 6.2 のようになる.  $\rho=0.5$ , K=7 では 0.01 程度失うが, K=50 では  $10^{-15}$ 以下である.実際の Derandomizer は 3 段で読み出し幅を1/8, 1/4, 1/4とする.深さを 1024 とすると 1 段目が 128, 2 段目が 32, 3 段目が 8, 合計で深さ 168 に相当する. これは 3 bunch 読み出しにとっては深さ 56 である.そこでBRAMを 1058bit× 1024 bit × 2= 約 2000 kbit 要求する. これにより busy 確率を  $10^{-15}$ 以下とする.

図 6.1: buffer depth と buffer overflow 確率.  $\rho = 0.5, K = 7$  では 0.01 程度失う.

図 6.2: buffer depth と buffer overflow 確率.  $\rho = 0.5, K = 50$  では  $10^{-15}$  以下である.

# 6.2 新 SL 基板設計

#### 6.2.1 クロック

クロック は意図通りの FPGA 設計ができる場所につける. FPGA 内部分周器は制約が多くいつも使えるとは限らない. GbE 125 MHz, GTX 125 MHz, DDR3 200 MHz をつける. 場所は PT7 と同じで良い.

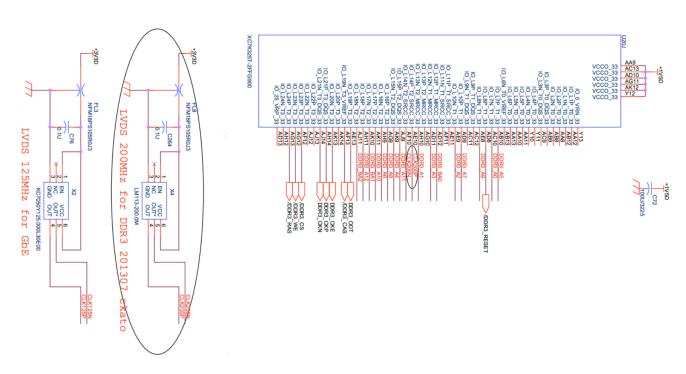

#### 6.2.2 GTX

XCK325T-2ffg900 は GTX 115 116 117 118 の 4bank を持つ. 1bank は 4lane の GTX を持ち 1lane 10 Gbps が可能である. 基本的に上下の bank からしか基準クロックを供給できない [35]. そのため bank 115, 117 を使う場合は 116 に基準 クロック をくべる. PT7v1 ではこれを 115 に配線したため 117 が使えなかった. 事前に FPGA を設計して確認しておくと良い. 図 6.3 に PT7v2 回路図 GTX 基準クロックを示す. PT7v2 では bank 115 から 116 に修正した.

#### 6.2.3 DDR3

DDR3 は本当に必要か確かめる。高速配線が多いと基板設計に時間がかかる。5 Gbps 以上の配線は特に前例が少ない。DDR3 は High Performance(HP) bank を用いる。impedance 調整のために各 bank に VRP/N 80.6 k Ω, VREF 0.75 V を必要とする。その pin を io として使った場合などは internal vref, dci\_cascade 制約で共有する。このため各 HP bank の電源電圧をそろえておく。図 6.6 に PT7v2 DDR3 用 HP bank 33 を示す。PT7v2 では bank 33 に基準クロック200MHz を追加した。

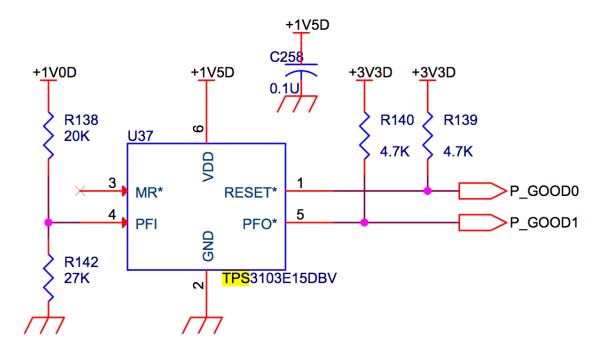

#### 6.2.4 電源監視機能

図 6.5 に PT7 U37 TPS3103E15DBV を示す. 1 台の PT7 では R142 27K を 33K に交換した. 1 V 電源が電圧降下の抵抗の精度数パーセントのばらつきで約 4% 下の閾値を下回ってしまった

図 6.3: PT7v2 GTX 基準クロック. PT7v2 では bank 115 から 116 に修正した

図 6.4: PT7v2 DDR3 用 HP bank 33. 基準クロック 200MHz を追加した.

図 6.5: PT7 U37 TPS3103E15DBV. 1 台の PT7 では R142 27K を 33K に交換した.

からである. 抵抗を交換し監視信号を確認した. その後 XADC で FPGA での正確な電圧を測定した. 今回監視信号の立たなかった電源 VCCINT は FPGA の要求 0.97 -1.03 V を満たし 0.997 -1.000 V だった. FPGA の要求は 3% 程度と厳しいので出来るだけ XADC で確認をする. 電源監視は LED でひとめでみることを目的とする. しかし抵抗のばらつきがあるので閾値の 10% 程度上で比較すると良い. もしくは関連する抵抗を高精度のものにすると良い.

#### 6.2.5 Configuration PROM

CERN では VME Single Board Computer (SBC) から FPAG を Configure する. VME は最大で 16 MHz x 32 bit で 500 Mbps 程度で動作する. FPGA の design の configuration 形式 のbit file は 100 Mbit 程度である. しかし VME crate のなかの SL を 1 台ずつ configure する必要がある. 1 crate 10 台とするとおよそ 2 sec かかる. SPI PROM では最大で 33 MHz x 1 bit で 33 Mbps 程度と遅いが配線が少ない. BPI PROM は最大で 33 MHz x 16 bit = 500 Mbps 程度で全ての SL を configure できる. この場合 100 Mbit / 500 Mbps = 0.2 msec で完了する.

新 SL でも FPGA configuration 用の PROM の導入を検討する. その場合 FPGA の m0, m1, m2 pin を DIP Switch か CPLD で可変にすると良い. (m0, m1, m2) = (1, 0, 0) が Master SPI mode, (m0, m1, m2) = (0, 1, 0) が Master BPI mode, (m0, m1, m2) = (0, 1, 1) が Select MAP mode である. 図 6.6 に PT7 FPGA m0, m1, m2 pin を示す.

また ISE 12 からは iMPACT JTAG download tool で PROM を直に書く機能が廃止された. FPGA を経由して PROM に書き込む必要があるが JTAG の接続が 1 つで済むので配線が減る.

図 6.6: PT7 FPGA m0, m1, m2 pin. Configuration mode を SelectMAP で固定している.

図 6.7: 従来の Zero Suppress. 全て 0 の 8 bit を捨て, 1 のある 8 bit は cell address などをつけて残す. data tag 2 bit は ROD への送信形式で 16 bit が header, data, trailer を識別する.

# 6.3 新SL FPGA 設計

#### 6.3.1 Zero Suppress

図 6.7 に概念図を載せる. 現行の SSW の zero suppress のものである. 全て 0 の 8 bit を捨て、1 のある 8 bit は cell address などをつけて残す. 0 が多い場合に圧縮が効く. data tag 2 bit は ROD への送信形式で 16 bit が header, data, trailer を識別する. g-link の場合は幅が 18 bit なので良い. 今回は SiTCP なので 16 bit にする. header, trailer を調整し, data tag 2 bit を省く. 2014年1月には、1024 bit 幅データへの zero suppress に成功した.

#### 6.3.2 読み出し形式

zero suppress 後の新 SL 読み出し形式について述べる. 表 6.2 に検討している新 SL 読み出し形式を示す. comma や over flow counter が必要になればつける. current next previous の id は readout data に含まれる. 従来の SLB ASIC [13] と SSW [14] を参考にした.

表 6.2: 検討している新 SL 読み出し形式. comma や over flow counter が必要になればつける.

| L1ID 4 bit BCID 12 bit readout data 16 bit readout data 16 bit readout data 16 bit trigger data 16 bit trigger data 16 bit trigger data 16 bit |

|------------------------------------------------------------------------------------------------------------------------------------------------|

| readout data 16 bit readout data 16 bit trigger data 16 bit trigger data 16 bit                                                                |

| readout data 16 bit trigger data 16 bit trigger data 16 bit                                                                                    |

| trigger data 16 bit<br>trigger data 16 bit                                                                                                     |

| trigger data 16 bit                                                                                                                            |

| trigger data 16 bit                                                                                                                            |

|                                                                                                                                                |

| trigger data 16 bit                                                                                                                            |

|                                                                                                                                                |

| trigger data 16 bit                                                                                                                            |

図 6.8: 新 SL 収集系. 新 SL 72 枚を市販の Switching Hub と PC で収集する.

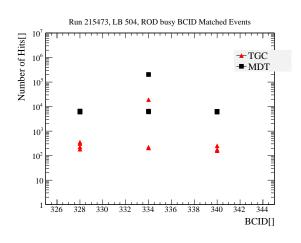

図 6.9: run 215473 ROD Busy 時の TGC MDT Hit 数. 普段の 2 桁程度多い事象がある.

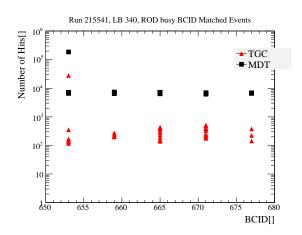

図 6.10: run 215541 ROD Busy 時の TGC MDT Hit 数. 普段の 2 桁程度多い事象がある.

#### 6.3.3 収集系

新 SL 72 枚を市販の Switching Hub と PC で収集する. zero suppress 無しの場合, 一枚 317 Mbps である. この場合 1 Gbps の switch でまとめられるのは数台までである. しかし本来のデータは 0 が多く zero suppress が効く. このためより多くをまとめられる. 現状の SL では 1/100 程度に圧縮されている. また, 衝突点片側に 36 枚など配置の制約もある. 費用と運用の効率を考える. 10 Gbps 環境も検討する. 図 6.8 に新 SL 収集系を示す.

#### 6.3.4 Burst 事象

2012 年の運転では Burst 事象が観測されている. L1A が 約 10 MHz で 数  $\mu$ sec 鳴る. L1A deadtime の 3bunch 間隔で鳴り続ける. ROD busy など buffer over flow を引き起こし L1A を停止する. システムを再起動しなければならない. Hit 数が普段の 2 桁程度多い事象が観測されている. 図 6.9 に run 215473 ROD Busy 時の TGC MDT ヒット数を示す. 図 6.10 に run 215541

ROD Busy 時の TGC MDT ヒット数を示す. 再構成後に残った Burst 事象を一つずつ含む. 電気的なノイズが原因と考えられている. この原因を究明し, 対策する必要がある.

私は RAW data からこの Burst を探す解析を行った. 2012年に SSW を監視する装置が導入された. その情報から LBN(Lumi Block Number) と BCID が一致する event を探した. Run 215414 215433, 215456, 215473, 215541, 215589 の各 12 stream を探した. 再構成出来た分では 215414, 215473, 215541 の JetTauEtmiss Stream に 4 つの Burst 事象 を発見した. この Burst は TGC MDT RPC で同時に起きることが判明した.

#### 6.3.5 Burst Stopper

2015 年からは従来の SL に Burst Stopper という仕組みを導入する [20]. 連続 M バンチ中に N 回以上の track を検知すると trigger 出力を veto する. 本研究の 新 SL 読み出しでもこれを導入する. これにより zero suppress を前提とする収集系を可能にする.

# 第7章 まとめ

本研究では ATLAS 実験のための新しいミューオントリガー装置, 新 SL の研究開発を行った. 2019 年の LHC 重心系エネルギー 14 TeV, ルミノシティ  $2\times 10^{34} {\rm cm}^{-2} {\rm s}^{-1}$  での稼働に備える. 新しいミューオン検出器 NSW を用いて, 現状約 98% のフェイクを約 66% 落とす. これにより第一段階ミューオントリガーへの要求精度 20 kHz 以下を満たす.

本研究の主な成果を述べる。新 SL 試作機 PT7 の動作確認をした。基板を修正し PT7 2 号機を製作した。従来の読み出し ASIC の L1Buffer と Derandomizer FIFO を FPGA に組み込んだ。FPGA TCP 処理技術 SiTCP は 新 SL の出力要求約 317 Mbps に対し最大約 891 Mbps を確認した。市販の Switching Hub で読み出せることを確認した。TTC 受信機 TTCrq で LHC 40 MHz clock や L1A を受信できる。メモリ資源を比較し FPGA の BRAM を選定した。BRAM では 新 SL 要求約 2000 kbit に対し 16020 kbit 可能である。高速シリアル通信 GTX 10 Gbps の Bit Error Rate は 8 lane 全て 10<sup>-13</sup> 以下であることを確かめた。GTX は 新 SL 入力要求約 39 Gbps に対し最大 80 Gbps 可能である。Zero Suppress を実装した。

GTX は頭出しや 8b10b の制御に課題が残った. 今後これを修正し, FPGA 読み出しを完成する. トリガーや収集系, 例外処理などを実装し性能評価をする. PT7 の結果をもとに 新 SL の設計を進める. 新 SL を ATLAS に導入し 2019 年の実験を可能にする.

# 謝辞

本研究に協力して頂いた皆様に感謝します.

小林富雄教授は研究の機会を与えて頂き, 進路や研究計画を相談して頂きました. 坂本宏教授は研究室に受け入れて頂き PT7, TGC の仕事に関わらせて頂きました. KEK 佐々木修教授は TGC の実際の仕事の指導を頂きました. KEK 池野正弘氏には PT7v2 の基板修正や IC の交換でお世話になりました. KEK 内田智久氏には FPGA 講習会や DAQ 研究会で助言を頂きました. KEK Esys の庄子正剛氏, OpenIt の皆様は研究会や回路室で助言を頂きました. GND 宮沢正和代表には PT7v2 の制作でお世話になりました.

ICEPP の先生方にお世話になりました. 徳宿克夫教授は Burst 探しの解析の際にこれは新物理かもしれないからと言って頂きました. 川本辰男准教授は ATLAS 見学に連れて行って頂きました. 浅井祥仁教授はたまに博士課程での研究計画を考えるときに相談して頂きました. 田中純一准教授は冬休みにも関わらず電話で進学後の相談を受けて頂きました. 中村智昭特任助教は修論を見て頂きました. 真下哲郎准教授は計算機のデータ置き場を割り当てて頂きました. 井上慶純助教は計算機関係でお世話になりました. 難波俊雄助教は大部屋で圧着端子などの道具を借して頂きました. 石田明助教はパルス技術実験でお世話になりました.

ATLAS, TGC の先生方にお世話になりました. 神戸大の蔵重久弥教授は CERN で SBC の設定を指導して頂きました. 都立大の福永力教授は独特の議論の展開が参考になりました. KEK の岩崎博行教授は独特のお話しが参考になりました. 名古屋大の戸本誠教授は 2013 年春の学会発表練習のときに指導を頂きました. 京都大の石野雅也准教授は ASD や Fan 交換の作業でお世話になりました. 京都大の隅田土詞助教は Burst 解析で再構成など grid の使い方を教わりました. KEK の青木雅人助教は Burst 解析で plot や slimming などを教わりました.

Weizmann 研究所の皆様にお世話になりました. Meir Shoa 氏には生活の面倒から作業場の規則, 防空壕の場所などを教わりました. Boris Yankovsky 氏は sTGC の製作を学ばせて頂きました. Amit Kiler 氏は wire を張る工程とそれを半田で留める方法を教わりました. Li Chang Yu 氏は全体にわたって TGC の点検と修正を教わりました. Ben Moshe Meny 氏は Tel Aviv 大学での宇宙線試験の施設を見学させて頂きました. Gil Cohen 氏は TGC の接着という緊張感のある工程を教わりました. Roey Idan 氏は現地で最初の友人で, グラファイト磨き教わりました. Lidan Shemesh 氏はガス系の接着を教わりました. Dror Margalit 氏は蜂の巣の作業を教わりました. Oron Goresh 氏は事務手続きを手助けして頂きました. Barak Hamami 氏は昼食時の注文の仕方を教わりました. Hadar Alper 氏は出国手続きでお世話になりました.

ICEPP 事務, 物理教務の皆様にもお世話になりました. 塩田雅子氏は飛行機の関係などでお世話になりました. 手塚淑恵氏は放射線関係などでお世話になりました. 竹本葉子氏は旧1号館, 3号館, 物品関係でお世話になりました. 宮園あき子氏は会議室の鍵などでお世話になりました. KEK本田由子氏は KEK 出張関係でお世話になりました.

ICEPP 先輩の皆様にもお世話になりました. 結束晃平氏は進路や仕事などいろいろ助言を頂き

ました. 道前武氏は車で送ってもらったり食事に呼んで頂きました. 東裕也氏は 2013 年春の学会前は発表を見て頂き指導を頂きました. 山口博史氏は最近も KEK などで CMB の仕事の話をして頂きました. 二ノ宮陽一氏は会議や解析の質問でお世話になりました. 吉原圭亮氏は進路や自動二輪の話をして頂きました. 宮崎彬氏は飲み物を頂き, いろいろな話を伺いました. 風間慎吾氏はいじめ問題の話などをして頂きました. 佐々木雄一氏は寮の先輩の話などをして頂きました. 山口洋平氏は年末に一緒に年越しそばを食べて頂きました. 稲田聡明氏は書類の書き方などを教わりました. 大谷育生氏は FPGA VME の基礎から CERN での生活を教わりました. 大和田健太氏は少し ROOT の使い方を教わりました. 小林愛音氏は CERN 出張前の持ち物などを教わりました. 森永真央氏は screen や dq2-get の使い方を教わりました. 崔原碩氏は留学生の事情などを教わりました. 黒崎龍平氏は授業や解析の様子を聞きました.

他大学先輩の皆様にもお世話になりました.総研大の鈴木友氏は TGC の L1A 頻度削減の内容について教わりました.名古屋大の長谷川慧氏は Burst 探しの時に変数の意味やどんどん手を挙げて質問することを教わりました.東工大の奥山豊信氏は CERN でたまに車で送って頂きました.東工大の野辺拓也氏は CERN で漫画や音楽の話をして頂きました.神戸大の岸本巴氏は CERNで家や車,自転車でお世話になりました.名古屋大の若林潤氏は CERNで 17 の設定などを教わりました.名古屋大の山内克弥氏は CERNでうどんを打って頂きました.京都大の田代拓也氏は CERNで家や白車でお世話になりました.

ICEPP 同期の皆様にもお世話になりました. 大川真耶氏は一番席が近くで, 最後の方は解析の話を聞きました. 川西裕紀氏は席が近くだったのでたまに机を借りたりしました. 西村美樹氏は向かいの部屋でよく食事に行きました. 横山晴道氏は断られることが多かったですが食事に行きました. 陳詩音氏は冒険家で, いつも自分を追い込んでいて参考になりました. 小坂井千紘氏はたまに昼食に声をかけてくれました. 露木孝尚氏は理論に転向したり話が面白かったです.

他大学同期の皆様にもお世話になりました。神戸大の来見田吏恵氏は SL 実装や Burst Stopper について参考にさせて頂きました。神戸大の稲丸由夫氏は高知学会の時に映画や楽器の話をして頂きました。東工大の本橋和貴氏は一緒に山に登って夏の学生の話をして頂きました。東工大の樋口浩太氏は露木孝尚氏の話やお米の話などをして頂きました。東工大の小林大氏は CERN での家の相談などをして頂きました。

ICEPP 後輩の皆様にもお世話になりました. 浦野祐作氏は会議室をとってくれました. 徳永孝 之氏は PT7 動作確認手引きや GTX 制御で協力してくれました. 久島真悟氏は体操の技を見せてくれました. 嶺岸優司氏は PT7 より高速配線が多い新基板の回路図を見せてくれました. 安達俊介氏は出張先のお土産をくれました. 山道智博氏は Swiss Pass について教えてくれました. 寺尾 伸吾氏は boxing の話をしてくれました. 山本遼氏は進路の話をしてくれました.

他大学後輩の皆様にもお世話になりました. 総研大の鈴木翔太氏は PT7 を用いた TTC 読み出しの件で CERN や KEK で作業しました. 神戸大の長谷川誠氏は車の仕事の話などを聞かせて頂きました. 京都大の救仁郷拓人氏は関西風の話題で盛り上げて頂きました.

多くの皆様のおかげで2年間研究出来ました.

最後に、家族や友人の皆様、この機会に感謝します.

ありがとうございました.

# 参考文献

- [1] CERN: LHC Design Report, 2004.

- [2] CERN Document Server / Photos http://cds.cern.ch/collection/Photos

- [3] CERN TWiki / ATLAS Public Results

- [4] ATLAS: The ATLAS Experiment at the CERN Large Hadron Collider, 2008.

- [5] ATLAS: Muon Spectrometer Technical Design Report, 1999.

- [6] ATLAS: New Small Wheel Technical Design Report, 2013.

- [7] TTC http://ttc.web.cern.ch/ttc/

- [8] S-link http://hsi.web.cern.ch/hsi/s-link/

- [9] James Stirling: Tevatron and LHC parton luminosity comparison plots http://www.hep.phy.cam.ac.uk/~wjs/plots/plots.html

- [10] ATLAS: Letter of Intent for the Phase-I Upgrade of the ATLAS Experiment, 2012.

- [11] Osamu Sasaki: Amplifer-Shaper-Discriminator ICs and ASD boards, 1999

- [12] R.Ichimiya, H.Kurashige, R.Kurumida: Design of the TGC Sector Logic for the ATLAS Endcap Muon Trigger System, 2013.

- [13] ATLAS-Japan TGC electronics group: Slave Board ASIC Technical Document, 2005.

- [14] Hiroshi Nomoto: Star Switch Spec, 2009.

- [15] https://atlas-proj-tgc.web.cern.ch/atlas-proj-tgc/ROD/TGCROD.html.

- [16] Yu Suzuki: Upgrade of the ATLAS Level-1 Muon Trigger for the High Luminosity LHC, 2013.

- [17] 大谷育生:ATLAS ミューオントリガーシステムのアップグレードに向けた ギガビット通信を 用いたデータ収集系の検証及び読み出しプロトタイプの開発, 2013

- [18] 神谷隆之: ATLAS 前後方ミューオントリガーシステムのアップグレードに向けた読み出し系システムインフラストラクチャの研究開発, 2011.

- [19] 二ノ宮陽一: High-luminosity LHC へ向けた ATLAS ミューオントリガー検出器用読み出し システムの開発, 2011.

- [20] 来見田吏恵: ATLAS 実験 RUN2 に向けたレベル 1 ミューオントリガーへの新しいアルゴリズム導入, 2013.

- [21] 田代拓也: ATLAS 実験における新しいミューオントリガー回路の開発と実装, 2012.

- [22] 桑原隆志: ALTAS 前後方ミューオントリガーシステムの構築, 2007

- [23] 門坂拓哉: ATLAS 前後方ミューオントリガーシステム Sector Logic 及びオンラインソフトウェアの開発, 2008.

- [24] 平山翔: ATLAS 実験前後方レベル1ミューオントリガーシステムの構築と検証, 2009.

- [25] 鈴木雄太: Look Up Table 改良による ATLAS レベル 1 ミューオントリガーの性能向上の研究, 2012.

- [26] 徳宿克夫: LHC/ATLAS アップグレードの展望, 2011.

- [27] 中本建志: LHC アップグレード計画 (HL-LHC, LIU) と日本の貢献, 2012.

- [28] 佐々木修: Muon Endcap Trigger Updates, ATLAS Upgrade Week 2012.

- [29] 内田智久: Hardware-Based TCP Processor for Gigabit Ethernet, 2008.

- [30] XILINX: 7 Series FPGAs Overview, DS180 (v1.14) July 29, 2013