# ATLAS ミューオントリガーシステムのアップグレードに向けた ギガビット通信を用いたデータ収集系の検証 及び 読み出しプロトタイプの開発

東京大学大学院理学系研究科 物理学専攻 素粒子物理国際研究センター 坂本研究室 大谷 育生

2013年2月5日

### 概要

2012 年 7 月 4 日, LHC における ATLAS 実験及び CMS 実験はともに  $5\sigma$  の確度で Higgs と見られる新粒子を発見したと発表した。新たな素粒子が見つかったのは 2000 年のフェルミ研究所におけるタウニュートリノ以来であり,素粒子標準モデルにおける素粒子が全て出そろったことになる。これは非常に歴史的な発見であり,物理に携わる者,はたまた一般の人々にとってさえも刺激的なニュースとなった。

しかしこれで物理が終わったわけではない.この新粒子の精密測定や標準理論を超えた現象の探索を通して,まだ解明されていない謎に迫るべく邁進せねばならない.それには現状の加速装置及び検出器では限界があり、アップグレードを重ねていく必要がある.

我々ATLAS 実験のミューオングループでは、精密な測定を妨げる不確定要素を取り除くため、トリガーのシステムを改善していく予定である。私はエレクトロニクスのアップグレードに際して有効な技術として、2つのギガビットクラスの高速通信技術を取り上げ、その検証実験を行った。1つは FPGA 組み込み TCP/IP プロセッサであり、複数のコンフィギュレーションでパフォーマンスの確認を行い、その有用性を確認した。もう1つは FPGA 内蔵マルチギガビットトランシーバであり、10Gbps の速度で問題なく作動することを確かめた。さらにこれら技術を搭載した読み出し用プロトタイプを設計・開発し、来たるべきアップグレードに有用な資産をもたらした。

本論文ではまず第1章、第2章で ATLAS 実験やトリガーシステムの概要を簡単に説明する。第3章、第4章で私の行った2つの実験について、第5章で読み出しプロトタイプ制作について述べる。

# 目次

| 第1章 | LHC における ATLAS 実験                           | 11   |

|-----|---------------------------------------------|------|

| 1.1 | LHC                                         | . 11 |

|     | 1.1.1 LHC 概要                                | . 11 |

|     | 1.1.2 LHC で行われている実験                         | . 12 |

| 1.2 | ATLAS 検出器                                   | . 14 |

|     | 1.2.1 検出器全体像                                |      |

|     | 1.2.2 内部飛跡検出器                               | . 15 |

|     | 1.2.3 カロリメータ                                | . 17 |

|     | 1.2.4 ミューオンスペクトロメータ                         | . 18 |

|     | 1.2.5 マグネット                                 | . 21 |

| 1.3 | トリガー及びデータ収集                                 | . 22 |

|     | 1.3.1 トリガー全体像                               | . 22 |

|     | 1.3.2 Level 1 Trigger                       | . 23 |

|     | 1.3.3 High Level Trigger                    | . 25 |

| 1.4 | ATLAS で目指す物理                                | . 25 |

|     | 1.4.1 Standard Model Higgs                  | . 26 |

|     | 1.4.2 Higgs 生成過程                            | . 27 |

|     | 1.4.3 Higgs 崩壊過程                            | . 28 |

|     | 1.4.4 プロパティ測定のまとめ                           | . 29 |

|     | 1.4.5 アップグレードに向けて                           | . 31 |

| 1.5 | LHC アップグレード計画                               | . 32 |

|     | 1.5.1 Long Shutdown 1 (2013-2014)           | . 33 |

|     | 1.5.2 Long Shutdown 2 (2018)                | . 33 |

|     | 1.5.3 Long Shutdown 3 (2022)                | . 33 |

| 1.6 | ATLAS アップグレード計画                             | . 34 |

|     | 1.6.1 phase-0                               | . 34 |

|     | 1.6.2 phase-1                               | . 35 |

|     | 1.6.3 phase-2                               | . 37 |

| 第2章 | レベル 1 エンドキャップミューオントリガーシステム                  | 39   |

| 2.1 | TGC について                                    | . 39 |

|     | 2.1.1 TGC 動作原理                              | . 39 |

|     | 2.1.2 TGC <b>の分類</b>                        | . 40 |

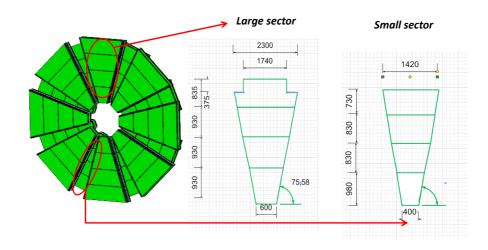

|     | 2.1.3 TGC の配置                               | . 41 |

|     | 2.1.4 TGC のセクター                             | . 42 |

| 2.2 | トリガースキーム・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ | . 43 |

|                   | $2.2.1$ $p_{ m T}$ 算出の概要 $\dots$                   | 43 |

|-------------------|----------------------------------------------------|----|

|                   | 2.2.2 段階的なコインシデンス                                  | 43 |

|                   | 2.2.3 Coincidence Window                           | 45 |

| 2.3               | トリガーエレクトロニクス                                       | 46 |

|                   | 2.3.1 全体のフロー                                       | 46 |

|                   | 2.3.2 フロントエンド                                      | 48 |

|                   | 2.3.3 HSC クレート                                     | 50 |

|                   | $2.3.4$ SL $\mathcal{D} \mathcal{V} - \mathcal{F}$ | 51 |

|                   | 2.3.5 SL からの読み出し                                   | 52 |

|                   | 2.3.6 TTC                                          | 54 |

| 2.4               | レベル1ミューオントリガーの改善に向けて                               | 54 |

|                   | 2.4.1 現状の問題                                        | 54 |

|                   | 2.4.2 フェイクミューオンの原因                                 | 55 |

|                   | 2.4.3 phase-0 での対策                                 | 56 |

|                   | 2.4.4 phase-1 での対策                                 | 56 |

|                   | 2.4.5 phase-2 での対策                                 | 58 |

|                   | 2.4.6 アップグレードに向けた開発計画                              | 59 |

| 笙り辛               | ギガビットイーサネットによるデータ収集系の構築実験                          | 60 |

| <b>知り早</b><br>3.1 | イーサネット及び TCP/IP                                    |    |

| 3.1               | 3.1.1 イーサネット                                       |    |

|                   | 3.1.2 TCP/IP                                       |    |

|                   | 3.1.3 UDP                                          |    |

| 3.2               | SiTCP                                              |    |

| 9.2               | 3.2.1 機能                                           |    |

|                   | 3.2.2 TCP 読み出し試験                                   |    |

| 3.3               | 1Gbps データ収集系の構築                                    |    |

| 0.0               | 3.3.1 実験の準備                                        |    |

|                   | 3.3.2 1対1の通信                                       |    |

|                   | 3.3.3 2対1の通信                                       |    |

|                   | 3.3.4 2対2の通信                                       |    |

| 3.4               | 100Mbps <b>データ収集系の構築</b>                           |    |

|                   | 3.4.1 実験の準備                                        |    |

|                   | 3.4.2 1対1の通信                                       |    |

|                   | 3.4.3 複数対1の通信                                      |    |

| 3.5               | 結論                                                 | 77 |

|                   |                                                    |    |

| -                 | マルチギガビットトランシーバ GTX Transceiver の検証実験               | 79 |

| 4.1               |                                                    |    |

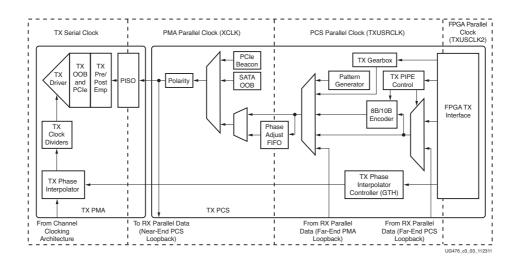

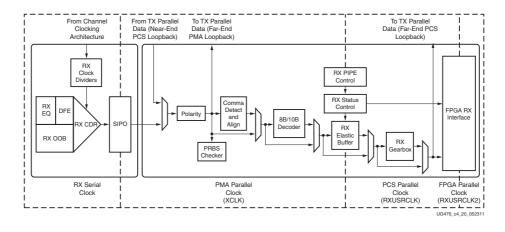

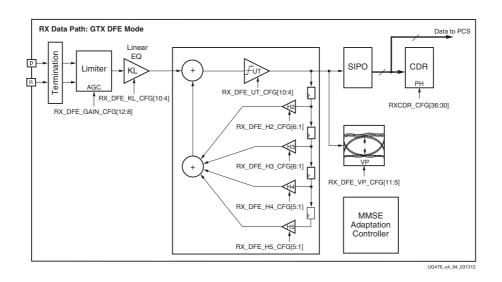

|                   | 4.1.1 Xilinx Multi-Gigabit Transceiver             |    |

|                   | 4.1.2 GTX Transceiver                              |    |

| 4.2               | 実験の目的及び対象・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・      |    |

|                   | 4.2.1 実験目的                                         | 83 |

|     | 4.2.2 KC705 評価キット                  | ۶4 |

|-----|------------------------------------|----|

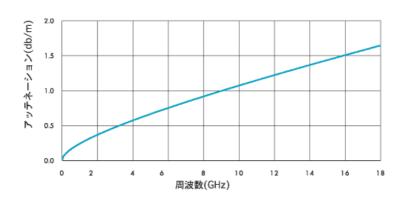

|     | 4.2.3 同軸ケーブル                       | 35 |

| 4.3 | GTX Transceiver の検証                | 6  |

|     | 4.3.1 <b>電流の測定</b>                 | 6  |

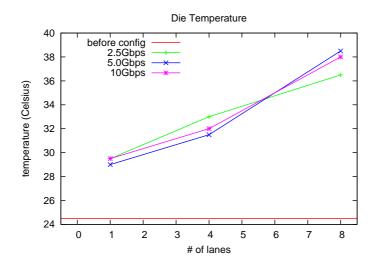

|     | 4.3.2 温度変化の測定                      | 39 |

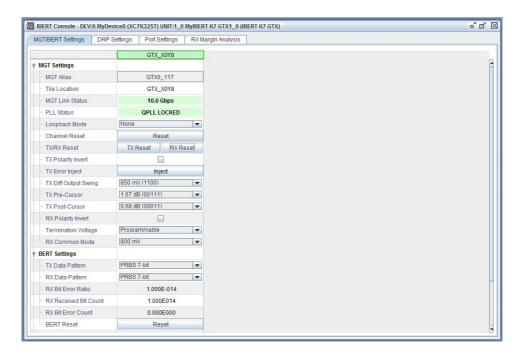

|     | 4.3.3 ビットエラーレート測定                  | 1  |

|     | 4.3.4 アイパターン測定                     | )2 |

| 4.4 | 結論                                 | 17 |

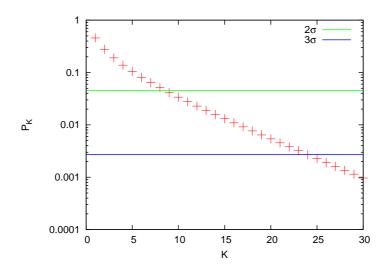

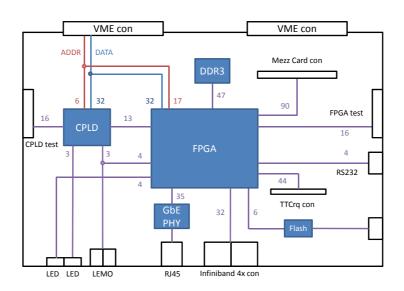

| 第5章 | Sector Logic アップグレード用プロトタイプの開発 9   | 8  |

| 5.1 | Sector Logic <b>ボードのアップ</b> グレード計画 | 18 |

|     | 5.1.1 アップグレードの動機                   | 18 |

|     | 5.1.2 New Small Wheel への要求         | 9  |

|     | 5.1.3 新 Sector Logic の概要           | 0  |

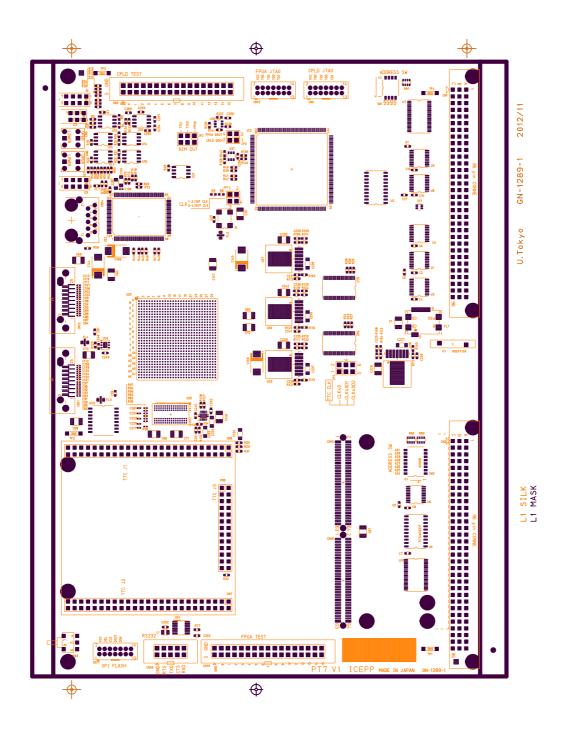

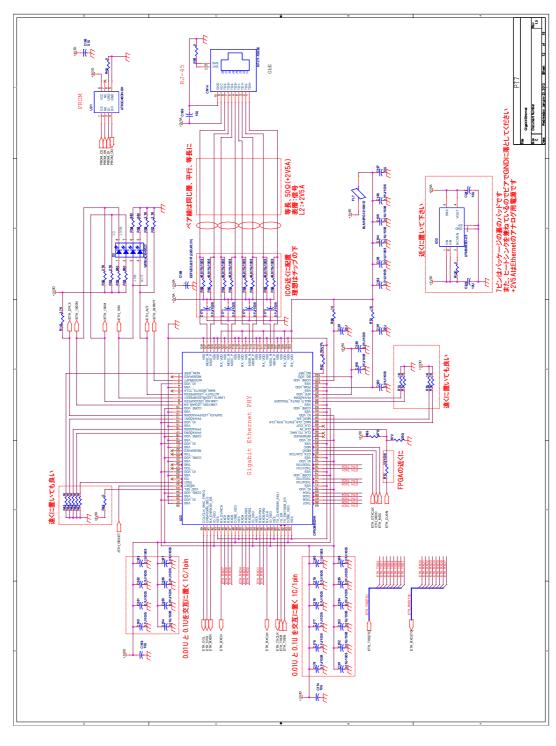

| 5.2 | PT7 の開発                            | )4 |

|     | 5.2.1 開発目的                         | )4 |

|     | 5.2.2 <b>要求される性能</b>               | )4 |

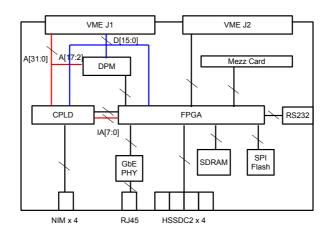

|     | 5.2.3 PT7 の構成                      | )5 |

| 5.3 | 各コンポーネントの説明10                      | )6 |

|     | 5.3.1 FPGA                         | 06 |

|     | 5.3.2 CPLD                         | )7 |

|     | 5.3.3 Ethernet PHY                 | )7 |

|     | 5.3.4 DDR3 SDRAM                   | 18 |

|     | 5.3.5 Flash memory                 | 18 |

|     | 5.3.6 クロック                         | 9  |

| 5.4 | 外部とのインターフェース                       | .0 |

|     | 5.4.1 VME バス                       | .0 |

|     | 5.4.2 <b>マルチギガビットトランシーバ</b>        |    |

|     | 5.4.3 ギガビットイーサネット                  | 2  |

|     | 5.4.4 メザニンカード                      | 2  |

|     | 5.4.5 TTC                          | 2  |

|     | 5.4.6 その他の I/O                     | .3 |

| 5.5 | 開発状況及び今後の方針11                      |    |

|     | 5.5.1 開発状況                         | 4  |

|     | 5.5.2 <b>今後の</b> 方針                |    |

| 第6章 | おわりに 11                            | 6  |

| 付録A | イーサネットの規格について 11                   | 7  |

| A.1 | イーサネット開発の経緯11                      | 7  |

|     | イーサネットの種類11                        |    |

| A.3 | 10/100/1000BASE-T                  | 8  |

|     | オートネゴシエーション 11                     |    |

| A.5        | ケーブルのカテゴリについて          | . 120 |

|------------|------------------------|-------|

| B.1<br>B.2 | PT6 について         開発の経緯 | . 122 |

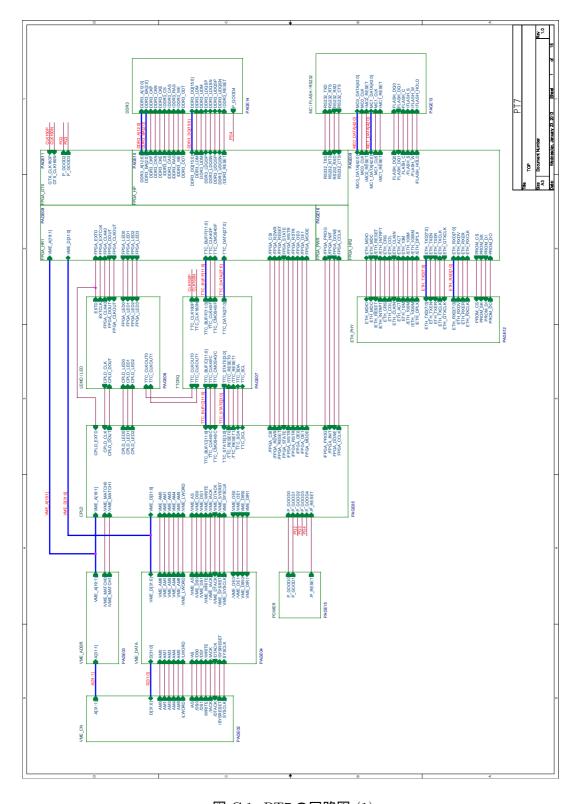

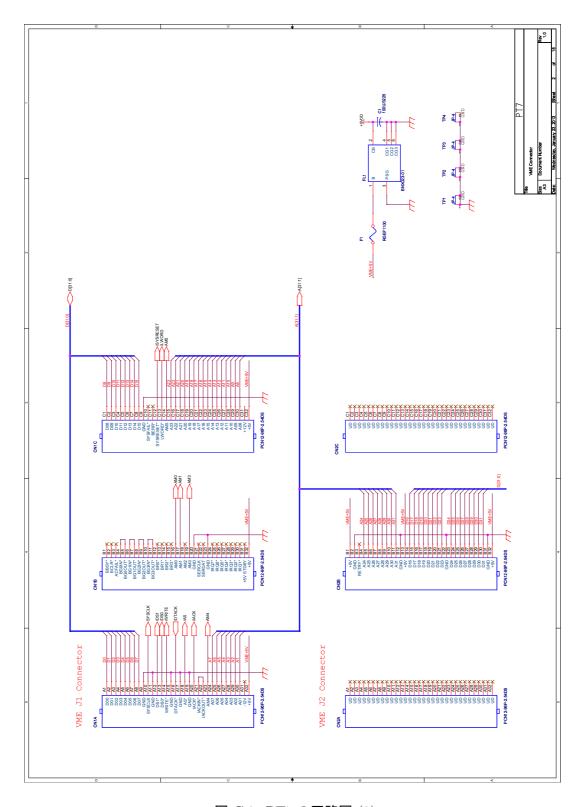

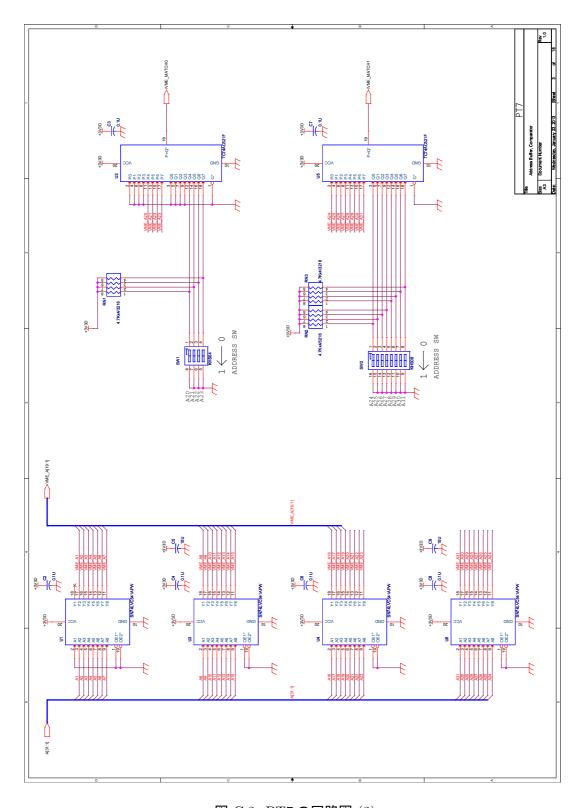

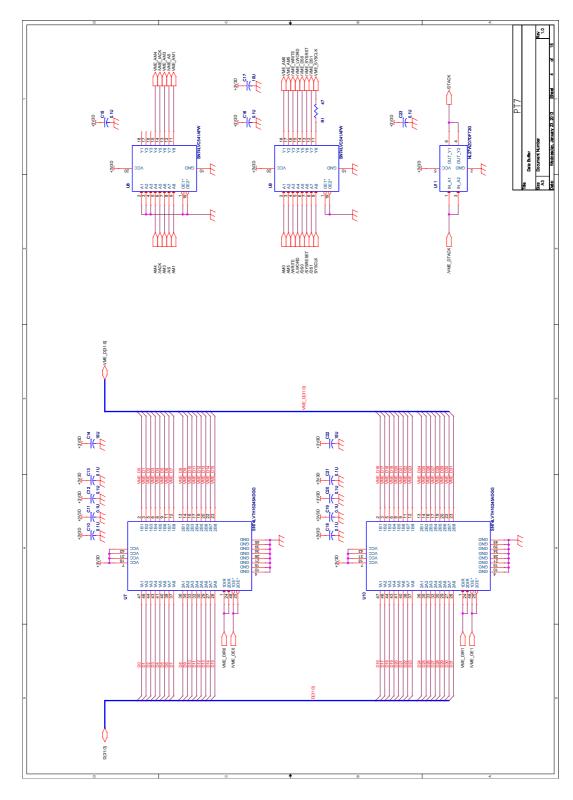

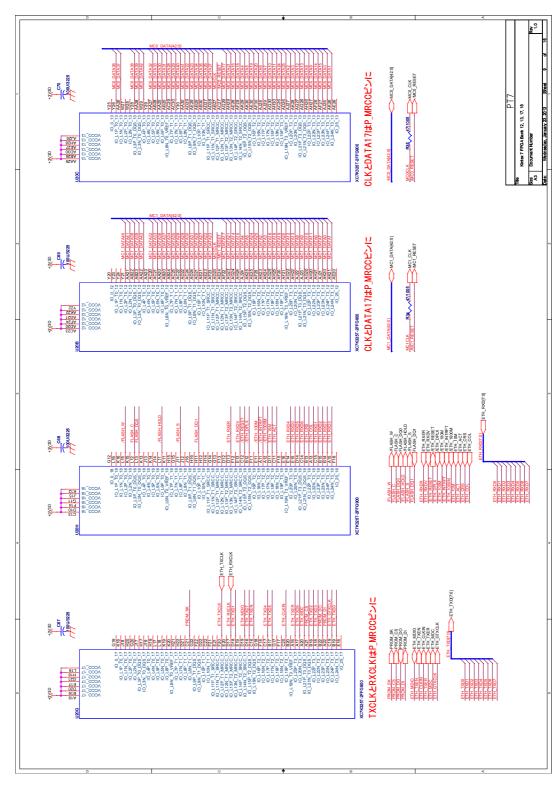

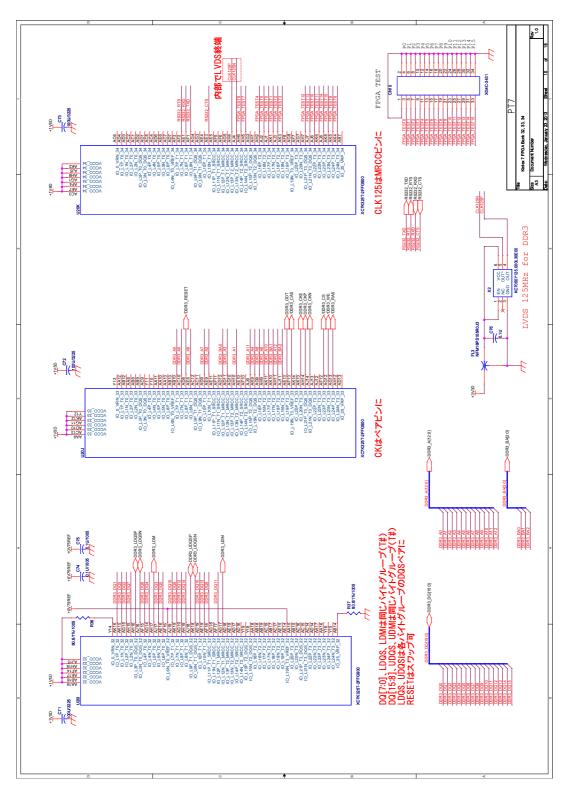

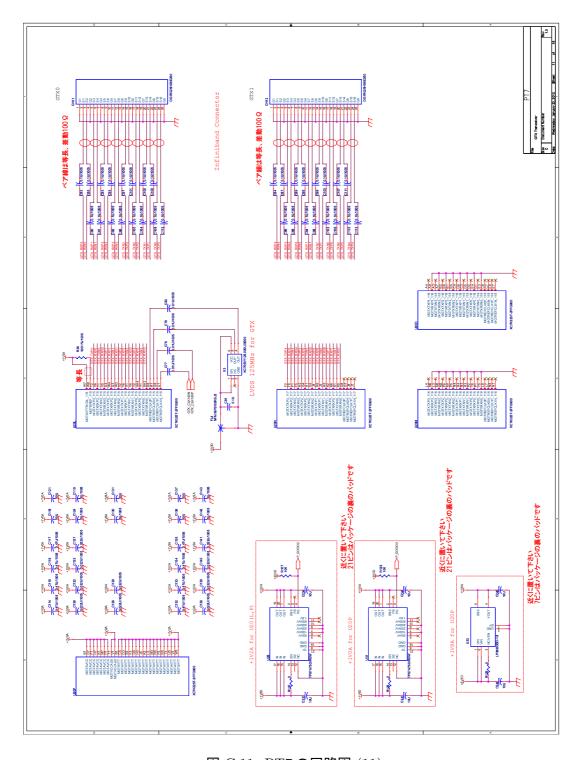

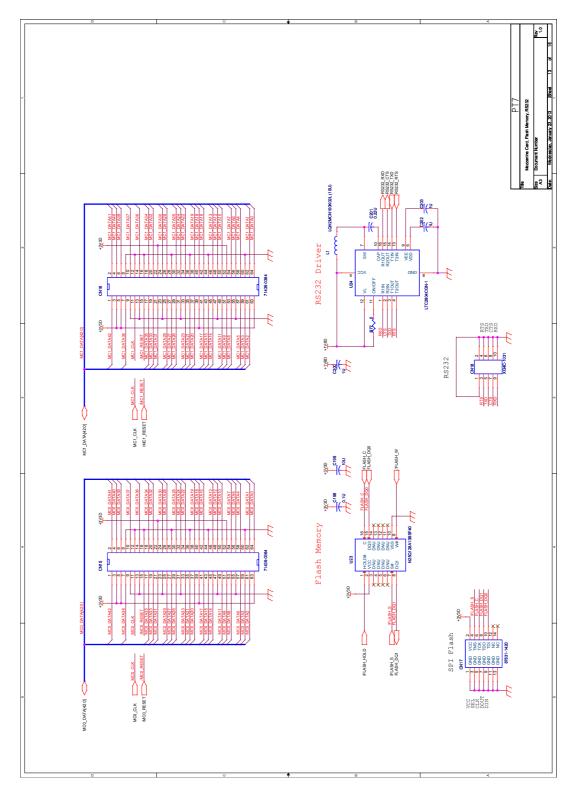

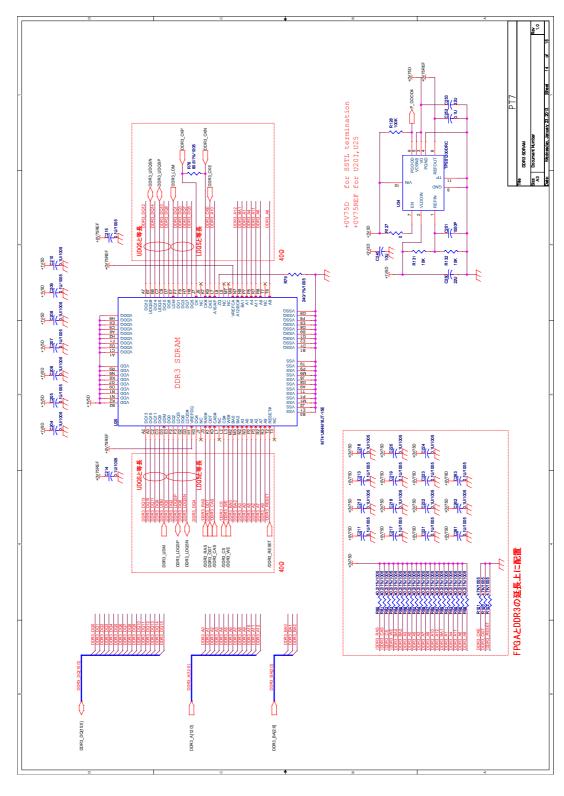

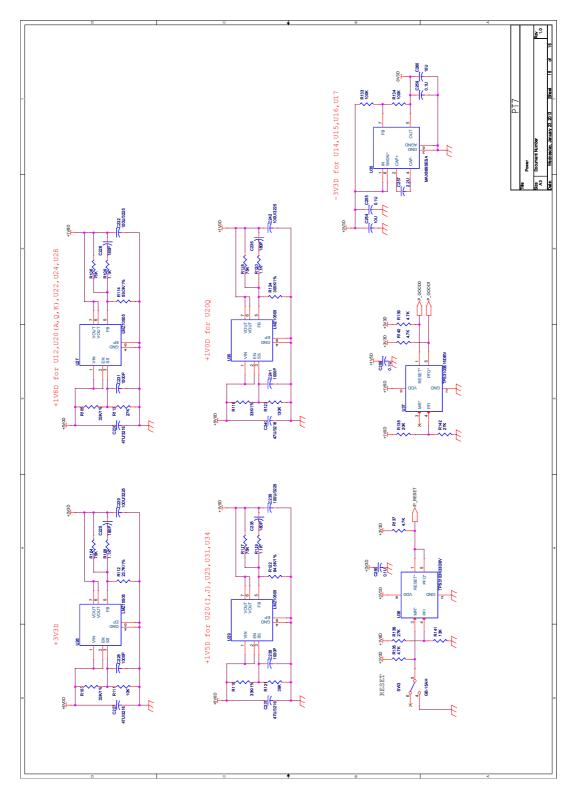

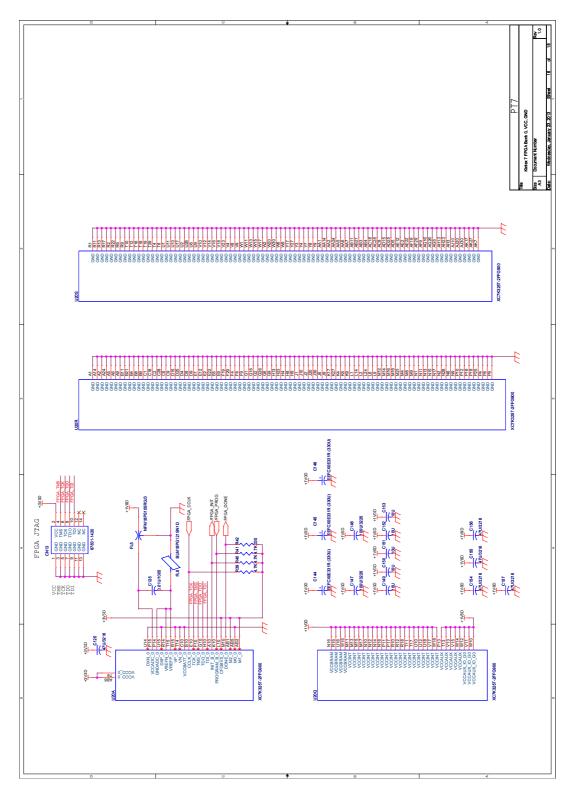

| 付録C        | PT7 の回路図               | 124   |

| 付録D        | List of abbreviations  | 141   |

# 図目次

| 1.1  | LHC <b>外観図</b> [4]                       | 11 |

|------|------------------------------------------|----|

| 1.2  | LHC と前段加速器 [4]                           |    |

| 1.3  | ATLAS 検出器 (左), CMS 検出器 (右)[4] $\dots$    | 13 |

| 1.4  | ALICE 検出器 (左), LHCb 検出器 (右)[4]           | 13 |

| 1.5  | ATLAS 検出器全体像 [6]                         | 14 |

| 1.6  | ATLAS における座標系 [25]                       | 15 |

| 1.7  | バレル部 ID[6]                               | 16 |

| 1.8  | カロリメータ [6]                               | 17 |

| 1.9  | ミューオンスペクトロメータ [6]                        | 18 |

|      | r-z 平面ステーション配置図 (Large sector)[6]        | 20 |

| 1.11 | ソレノイド磁石, トロイド磁石 [6]                      | 21 |

|      | 重心エネルギーに対する断面積プロット $[13]$                | 22 |

| 1.13 | TDAQ 概要 [6]                              | 23 |

| 1.14 | L1 トリガーシステム [6]                          | 24 |

| 1.15 | $\mathrm{TTC}$ を構成するモジュール $[23]$         | 24 |

| 1.16 | 2012 年 7 月時点でのプロット [5]                   | 25 |

|      | Higgs <b>生成過程</b> [23]                   | 27 |

| 1.18 | Higgs <b>生成断面積</b> [11]                  | 28 |

| 1.19 | Higgs 崩壞分岐比 [11]                         | 28 |

| 1.20 | 結合定数の測定精度 [12]                           | 30 |

| 1.21 | ルミノシティの変遷 [5]                            | 32 |

| 1.22 | 検討中の D1 磁石 [32]                          | 33 |

| 1.23 | クラブ衝突の概念図 [31]                           | 33 |

| 1.24 | IBL <b>挿入前後のイメージ</b> [15]                | 34 |

| 1.25 | 予測されるカウントレート $[14]$                      | 35 |

| 1.26 | MicroMegas の概略図 [14]                     | 35 |

| 1.27 | High Granularity Calorimeter Trigger[14] | 36 |

| 1.28 | FTK とトリガーフロー [21]                        | 37 |

| 1.29 | 新しい ${ m ID}$ のイメージ $[16]$               | 38 |

| 2.1  | TGC の内部構造 [6]                            | 39 |

| 2.2  | ダブレット, トリプレットの構造 [6]                     | 40 |

| 2.3  | Big Wheel[6]                             |    |

| 2.4  | TGC の配置図 [6]                             | 41 |

| 2.5  | TGC におけるセクター及びサブセクター [25][29]            | 42 |

|      | 7 決定の什組み [23]                            | 43 |

| 2.7  | 段階的なコインシデンス [23]                                     | 44 |

|------|------------------------------------------------------|----|

| 2.8  | CW の例 [29]                                           | 45 |

| 2.9  | トリガーフロー [24]                                         | 47 |

| 2.10 | BW 上の PS ボード及び HSC クレート [24]                         | 47 |

|      |                                                      | 47 |

| 2.12 | PS ボードの概要 [24]                                       | 48 |

| 2.13 | ASD の概要 [23]                                         | 49 |

|      |                                                      | 50 |

|      |                                                      | 50 |

|      |                                                      | 51 |

| 2.17 | リードアウトフロー [24]                                       | 53 |

|      |                                                      | 53 |

| 2.19 | ROD の写真 [25]                                         | 53 |

| 2.20 | L1_MU20 の $\eta$ 分布 [17]                             | 55 |

| 2.21 | $d	heta,dL$ カットの模式図 $\ldots$                         | 57 |

| 2.22 | d	heta,dL カットの結果 $[17]$                              | 57 |

| 2.23 | phase-2 トリガースキーム [33]                                | 58 |

|      | phase-2 のエレクトロニクス配置例 [28]                            | 59 |

| 0.1  |                                                      | co |

| 3.1  | SiTCP のブロック図 [46]                                    |    |

| 3.2  | TCP のチェック                                            |    |

| 3.3  |                                                      | 65 |

| 3.4  | *                                                    | 67 |

| 3.5  |                                                      | 67 |

| 3.6  |                                                      | 68 |

| 3.7  |                                                      | 68 |

| 3.8  |                                                      | 71 |

| 3.9  | MSS 設定値に対するスループットの変化                                 |    |

|      |                                                      |    |

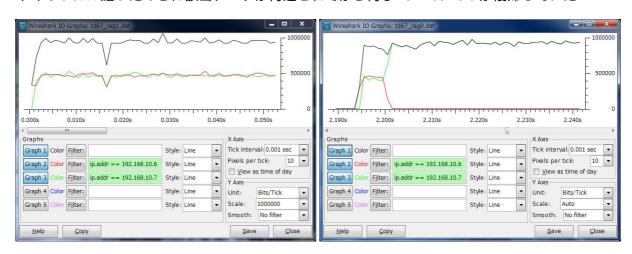

|      | 1G 環境 2 対 1 通信における帯域使用状況 (左: Nagle on, 右: Nagle off) |    |

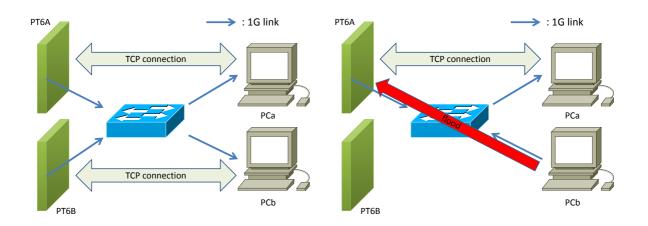

|      | 2 対 2 の通信                                            |    |

|      | flood 環境下の通信                                         |    |

|      | LAN ケーブルの結線                                          |    |

|      | 100Mbps テスト環境                                        |    |

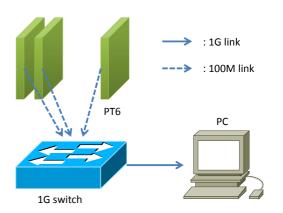

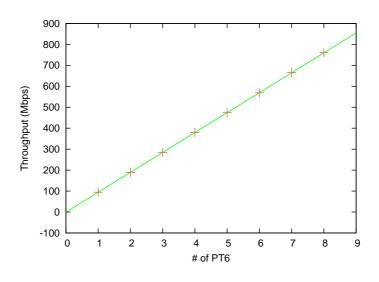

| 3.16 | 100M 環境 複数対 1 通信スループットのプロット                          | 77 |

| 4.1  | GTX TX のブロック図 [59]                                   | 80 |

| 4.2  | GTX RX のブロック図 [59]                                   | 81 |

|      | DFE のブロック図 [59]                                      |    |

| 4.4  | KC705 の写真                                            |    |

| 4.5  | 同軸ケーブルの構造 [62]                                       | 85 |

| 4.6  | 同軸ケーブルの減衰率 [62]                                      |    |

|      |                                                      | 86 |

| 4.8  | ループバックの様子                                                                                                            | 88  |

|------|----------------------------------------------------------------------------------------------------------------------|-----|

| 4.9  | VCCINT に流れる電流                                                                                                        | 88  |

| 4.10 | MGTAVCC に流れる電流                                                                                                       | 89  |

| 4.11 | MGTAVTT に流れる電流                                                                                                       | 89  |

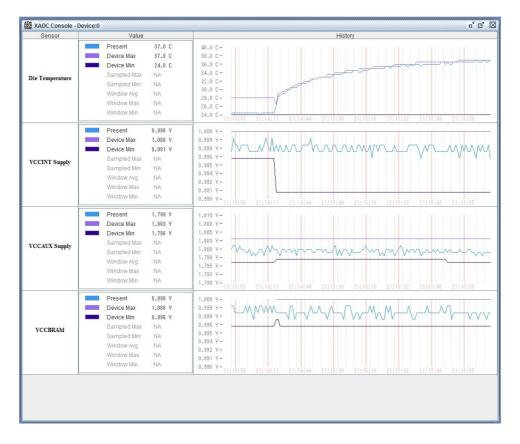

| 4.12 | XADC のコンソール                                                                                                          | 90  |

| 4.13 | FPGA <b>ダイ上の温度</b>                                                                                                   | 91  |

| 4.14 | IBERT 画面                                                                                                             | 91  |

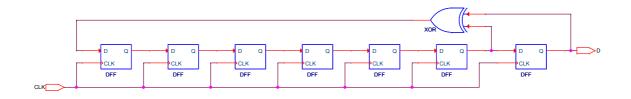

| 4.15 | PRBS-7 の生成回路                                                                                                         | 92  |

|      | アイパターンの例 [59]                                                                                                        |     |

|      | 統計的アイ生成部のブロック図 [59]                                                                                                  |     |

| 4.18 | ケーブル 3m の統計的アイ                                                                                                       | 95  |

| 4.19 | ケーブル 5m の統計的アイ                                                                                                       | 95  |

|      | ケーブル $7\mathrm{m}$ の統計的アイ $\ldots$                                                                                   |     |

|      | ケーブル $9\mathrm{m}$ の統計的アイ $\dots$                                                                                    |     |

|      | ケーブル $11\mathrm{m}$ の統計的アイ $\ldots$ |     |

| 4.23 | ケーブル $14\mathrm{m}$ の統計的アイ $\ldots$                                                                                  | 95  |

|      | CTLE 周波数応答 [59]                                                                                                      |     |

| 4.25 | CTLE 周波数応答+ケーブルの減衰                                                                                                   | 97  |

| 5.1  | SL のリードアウトのイメージ                                                                                                      | 00  |

| 5.2  |                                                                                                                      |     |

| 5.3  | NSW の外観 [14]                                                                                                         |     |

| 5.4  | BW と NSW sector の対応例 [33]                                                                                            |     |

| 5.5  | PT7 のブロック図                                                                                                           |     |

| 5.6  | DDR3 SDRAM プロック図 [65]                                                                                                |     |

| 5.7  | Infiniband ケーブル及びコネクタの写真                                                                                             |     |

| 5.8  | ####################################                                                                                 |     |

| 5.9  | TTCrq の写真                                                                                                            |     |

|      | PT7 <b>フロントパネル</b>                                                                                                   |     |

|      | PT7 レイアウト                                                                                                            |     |

| 9.11 |                                                                                                                      | 110 |

| 6.1  | ATLAS の人々[4]                                                                                                         | 116 |

| D 4  | P                                                                                                                    |     |

|      | PT6 の写真 [28]                                                                                                         |     |

|      | PT6 ブロック図 [28]                                                                                                       |     |

| В.3  | raw data monitor 概念図                                                                                                 | 123 |

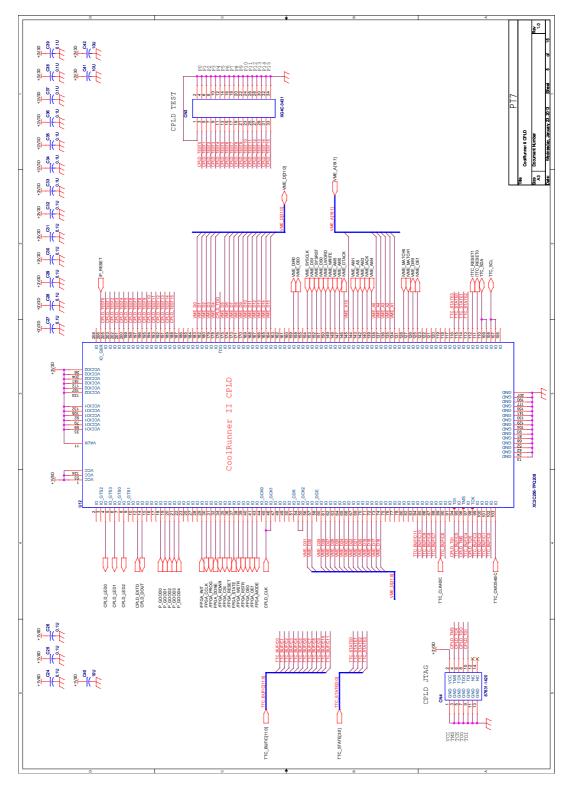

| C.1  | PT7の回路図 (1)                                                                                                          | 125 |

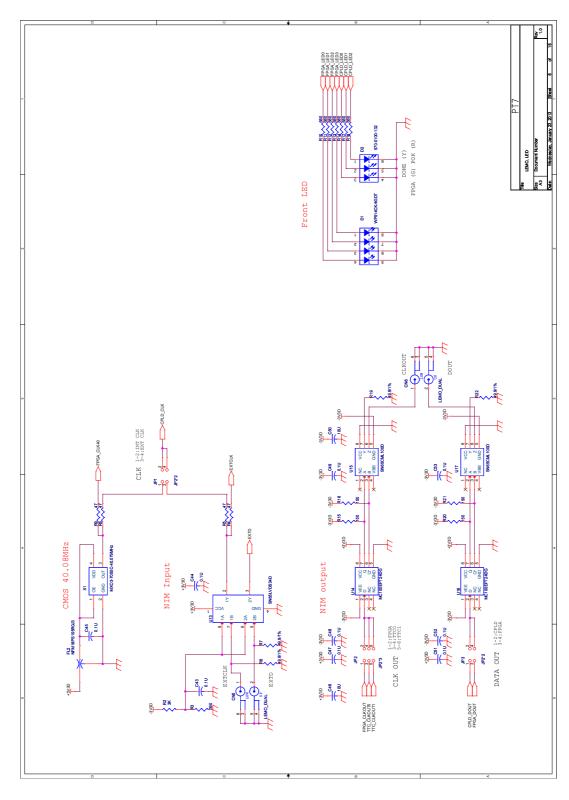

|      | PT7 の回路図 (2)                                                                                                         |     |

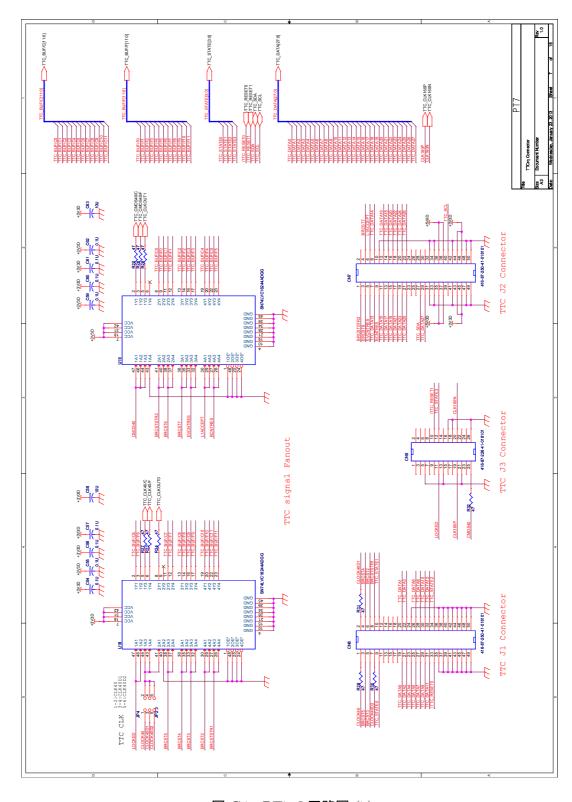

|      | PT7の回路図 (3)                                                                                                          |     |

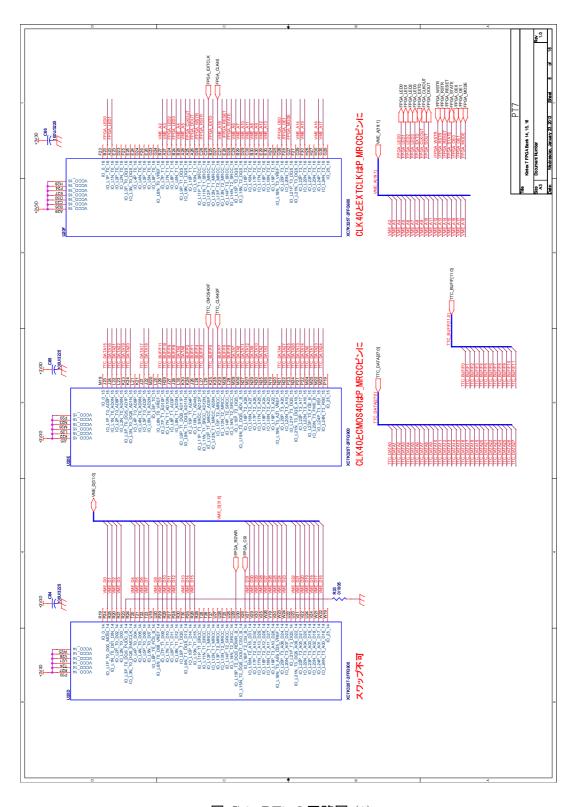

|      | PT7 の回路図 (4)                                                                                                         |     |

|      | PT7 の回路図 (5)                                                                                                         |     |

|      | PT7の回路図 (6)                                                                                                          |     |

|      | PT7 の回路図 (7)                                                                                                         |     |

|      |                                                                                                                      |     |

| C.8  | PT7 | の回路図 | (8)  |  |  |  |  |  |  |  |  |  | <br> |  |  |  |  |  |  | 132 |

|------|-----|------|------|--|--|--|--|--|--|--|--|--|------|--|--|--|--|--|--|-----|

| C.9  | PT7 | の回路図 | (9)  |  |  |  |  |  |  |  |  |  | <br> |  |  |  |  |  |  | 133 |

| C.10 | PT7 | の回路図 | (10) |  |  |  |  |  |  |  |  |  | <br> |  |  |  |  |  |  | 134 |

| C.11 | PT7 | の回路図 | (11) |  |  |  |  |  |  |  |  |  | <br> |  |  |  |  |  |  | 135 |

| C.12 | PT7 | の回路図 | (12) |  |  |  |  |  |  |  |  |  | <br> |  |  |  |  |  |  | 136 |

| C.13 | PT7 | の回路図 | (13) |  |  |  |  |  |  |  |  |  | <br> |  |  |  |  |  |  | 137 |

| C.14 | PT7 | の回路図 | (14) |  |  |  |  |  |  |  |  |  | <br> |  |  |  |  |  |  | 138 |

| C.15 | PT7 | の回路図 | (15) |  |  |  |  |  |  |  |  |  | <br> |  |  |  |  |  |  | 139 |

| C.16 | PT7 | の回路図 | (16) |  |  |  |  |  |  |  |  |  | <br> |  |  |  |  |  |  | 140 |

# 表目次

| 1.1 | LHC のデザイン値 [1]                                                |

|-----|---------------------------------------------------------------|

| 1.2 | LHC で行われている実験                                                 |

| 1.3 | ID の性能 [7]                                                    |

| 1.4 | ミューオンスペクトロメータの性能 [8]19                                        |

| 1.5 | 各ステーションの構成 (Large sector)[8]                                  |

| 1.6 | 生成断面積, 分岐比と結合定数                                               |

| 1.7 | HL-LHC へのロードマップ                                               |

| 2.1 | $	ext{L}1$ トリガーメニューと $p_{	ext{T}}$ の関係 $	ext{$                |

| 2.2 | レイテンシテーブルの例 [33]                                              |

| 2.3 | SLB ASIC と各エレクトロニクスの対応関係 [22]                                 |

| 3.1 | OSI 参照モデル                                                     |

| 3.2 | RBCP <b>アドレス</b> 空間 [47]                                      |

| 3.3 | イーサネットフレームの構造69                                               |

| 3.4 | SiTCP and TCP control register                                |

| 3.5 | $1G$ 環境 $1$ 対 $1$ でのスループット測定結果 $(\mathrm{Mbps})$ 70           |

| 3.6 | $1G$ 環境 $2$ 対 $1$ でのスループット測定結果 $(2$ 台の合計 $, Mbps)$ $\dots 72$ |

| 3.7 | $1G$ 環境 $3$ 対 $1$ でのスループット測定結果 $(3$ 台の合計 $, Mbps)$ $\dots 73$ |

| 3.8 | $100	ext{M}$ 環境 $1$ 対 $1$ でのスループット測定結果 $(	ext{Mbps})$         |

| 3.9 | 100M 環境 複数対 1 でのスループット測定結果 (Mbps)                             |

| 4.1 | Xilinx MGT の速度の変遷                                             |

| 4.2 | GTX のサポートするプロトコル [59] 83                                      |

| 4.3 | KC705 の使用する GTX [55]                                          |

| 4.4 | KC705 の電源レール [55]                                             |

| 4.5 | 測定対象のコンフィギュレーション                                              |

| 5.1 | 新 SL のコインシデンス部                                                |

| 5.2 | 新 SL のリードアウト部102                                              |

| 5.3 | Kintex-7 シリーズ性能比較 [52]                                        |

|     | PT7 <b>のクロック一</b> 覧                                           |

|     | PT7 <b>のアドレス</b> 空間                                           |

| 5.6 | VME <b>で使用する信号線</b>                                           |

| A.1 | イーサネット規格の命名118                                                |

| A 2 | 各規格のコーディング [66]                                               |

|     | オートネゴシエーションの優先順位        |    |

|-----|-------------------------|----|

| B.1 | Spartan-6 シリーズ性能比較 [51] | 22 |

|     | PT7 回路図中のリファレンスの意味      |    |

| D.1 | List of abbreviations   | 11 |

# 第1章 LHCにおけるATLAS実験

私はATLAS 実験に参加しており、特にアップグレードに向けた研究に従事している. 本章では前提知識となる LHC 及び ATLAS 実験、さらにアップグレード計画についての概説を行う.

# 1.1 LHC

ATLAS 実験の説明に入る前に、本節では ATLAS が利用しているシンクロトロン、LHC について述べる.

### 1.1.1 LHC 概要

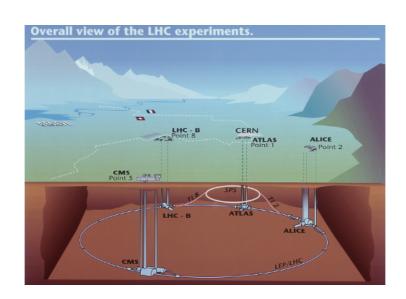

LHC こと Large Hadron Collider はスイス・ジュネーブ郊外の地下約 100m に建設された、世界最大のシンクロトロンである。図 1.1 に LHC の外観図を示す。LEP  $^1$  に使われていた周長約 27km のトンネルを利用して CERN  $^2$  が構築した。電子-陽電子衝突型であった LEP とは異なり、超伝導加速空洞と偏向用超伝導電磁石の導入により陽子-陽子衝突を可能にしている。2012 年現在ビームエネルギーは 4TeV であり、最大のエネルギースケールで実験を行える加速器となっている。

図 1.1: LHC 外観図 [4]

$<sup>^1 \</sup>rm Large~Electron$ -Positron collider: CERN が 1989 年から 2000 年にかけて実験していた電子-陽電子衝突型シンクロトロン. 重心系エネルギーは約 100GeV

<sup>&</sup>lt;sup>2</sup>Counseil Européen pour la Recherche Nucléaire: 欧州原子核研究機構

表 1.1 に LHC のパラメータ (デザイン値) を挙げる. ビームエネルギーとルミノシティはまだデザイン値に達しておらず, 後述の LHC アップグレードにより改善していく方針である. 2012 年はビームエネルギー 4TeV で稼働し、最大瞬間ルミノシティは  $7.7 \times 10^{33}~\text{cm}^{-2}\text{s}^{-1}$  を記録した.

表 1.1: LHC のデザイン値 [1]

| <br>リング周長 | $26.7~\mathrm{km}$  | 偏向磁場      | 8.33 T                                  |

|-----------|---------------------|-----------|-----------------------------------------|

| ビームエネルギー  | $7~{ m TeV}$        | 瞬間ルミノシティ  | $10^{34} \text{ cm}^{-2} \text{s}^{-1}$ |

| バンチ間隔     | $24.95~\mathrm{ns}$ | バンチあたり陽子数 | $1.15\times10^{11}$                     |

| バンチ ID 総数 | 3564                | 使用バンチ数    | 2808                                    |

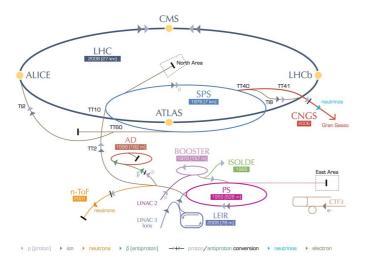

LHC に陽子ビームを入れる前に、複数の前段加速器により段階的にエネルギーを上げる必要がある。まず陽子イオン源から出た陽子イオンは線形加速器である Linac2 で加速される。これを PS (Proton Synchrotron) に入れる前に、PS Booster と呼ばれるシンクロトロンで 1.4GeV までエネルギーを引き上げる。その後 PS、SPS (Super Proton Synchrotron) により段階的にエネルギーを 450GeV まで上げ、LHC に入射させる。この概要を図 1.2 に示す。

# **CERN's accelerator complex**

|         | Length            | Energy          |

|---------|-------------------|-----------------|

| Linac2  | 30  m             | $50~{ m MeV}$   |

| Booster | $160~\mathrm{m}$  | $1.4~{\rm GeV}$ |

| PS      | $630~\mathrm{m}$  | $25~{ m GeV}$   |

| SPS     | $6.9~\mathrm{km}$ | $450~{\rm GeV}$ |

| LHC     | $27~\mathrm{km}$  | $7~{ m TeV}$    |

図 1.2: LHC と前段加速器 [4]

# 1.1.2 LHC で行われている実験

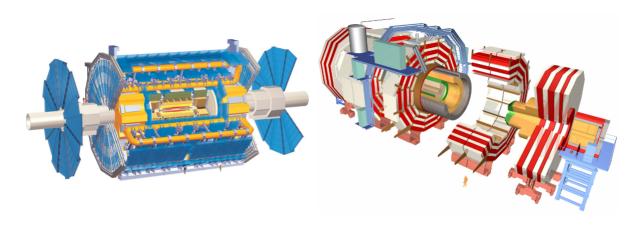

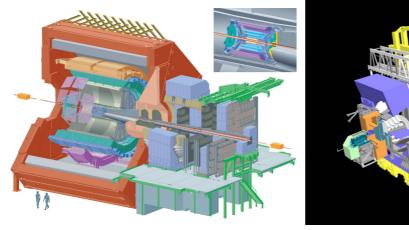

LHC で行われている実験のうち、ATLAS(A Toroidal LHC ApparatuS)と CMS(Compact Muon Solenoid)はどちらも汎用の大型検出器である。LHC リングの正反対の位置に居を据え、互いに成果を競い合っている。2012 年の 7 月には揃って 125-126 GeV 付近に  $5\sigma$  の確度で Higgs と みられる新粒子を発見したと発表した [2][3](ATLAS: 126 GeV,CMS: 125 GeV)。

ALICE (A Large Ion Collider Experiment) では陽子ではなく重イオン ( $^{208}$ Pb $^{82+}$ ) 同士を衝突させた実験により、宇宙初期の状況の再現及び Quark Gluon Plasma (QGP) の研究がなされてい

る. LHCb (Large Hadron Collider beauty) では b クオークの物理に焦点を当て, B メソンにおける CP 対称性の破れの測定を行っている.

ATLAS, CMS, LHCb, ALICE 実験についての概要を表 1.2 にまとめた. また, 各実験で用いられている検出器の概略図を図 1.3, 1.4 に示す.

| 表 1.2: LHC で行われてい | ۱ス | 宝騇 |

|-------------------|----|----|

|-------------------|----|----|

| 実験名   | サイト3    | 実験概要               |

|-------|---------|--------------------|

| ATLAS | point 1 | 大型汎用検出器による実験       |

| ALICE | point 2 | 重イオン検出器による QGP の物理 |

| CMS   | point 5 | 大型汎用検出器による実験       |

| LHCb  | point 8 | B メソンにおける対称性の破れの検証 |

図 1.3: ATLAS 検出器 (左), CMS 検出器 (右)[4]

図 1.4: ALICE 検出器 (左), LHCb 検出器 (右)[4]

$<sup>^3</sup>$ LHC を上空から見て 8 等分する点に point  $1\sim$  point 8 と時計回りに番号がついている. 各 point には検出器やビームダンプが配置されている

# 1.2 ATLAS 検出器

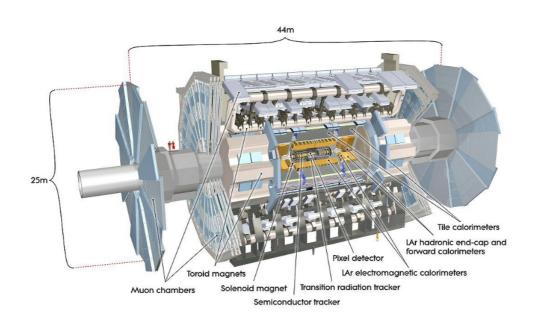

ATLAS では大型汎用検出器を用いて Higgs 粒子や標準理論を超える現象を追っている. 3000人を超える研究者が従事しており、日本からも多数の研究者や学生が研究に当たっている. 検出器は直径 25m、長さ 44m の円筒形をしており、LHC の検出器の中では最大規模を誇る.

本節では ATLAS 検出器の構成について簡単な説明を行う.

#### 1.2.1 検出器全体像

衝突型加速器における一般的な検出器は、内側から飛跡検出器、電磁カロリメータ、ハドロンカロリメータ、ミューオン検出器という構成をとる。飛跡検出器はソレノイド磁場で曲げられた荷電粒子をとらえ、飛跡の再構成を行い運動量を測定する。電磁カロリメータは電磁シャワーにより電子及び光子のエネルギーを測定する。ハドロンカロリメータは電磁カロリメータと同様にジェットのエネルギーを測定する。ミューオンは荷電粒子であるが断面積が小さくこれらを通り抜けてくるため、最外部に配置したミューオン検出器により位置を測定する。

ATLAS においても内部飛跡検出器, (電磁/ハドロン) カロリメータ, ミューオンスペクトロメータが内側から順に配置されている. ただし特徴的なのがマグネットで, 一般的なソレノイド磁石に加えてトロイド磁石を用いており, ミューオンスペクトロメータにおける運動量測定を可能にしている. 次小節以降でそれぞれについてもう少し詳しく説明する. 図 1.5 に ATLAS 検出器の全体像を載せる.

図 1.5: ATLAS 検出器全体像 [6]

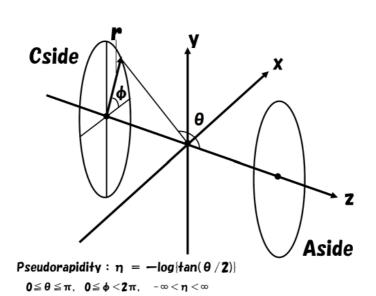

### 座標系について

ATLAS では主に xyz 座標系もしくは  $r\phi z$  座標系を用いる. xyz 座標系は一般的な三次元直交座標系であり、ビームパイプ方向を z 軸, LHC リング中心方向を x 軸, それらと垂直な方向を y 軸  $^4$  としている. また、円筒型である ATLAS 検出器の両サイドを表すのに z 軸が正の方向を A-side、負の方向を C-side と呼ぶことがある.

$r\phi z$  座標系は円筒座標系であり、ATLAS 検出器の各要素の位置を示すのに適している。 ビームパイプ方向を z 軸とするのは同じで、円筒の動径方向を r、方位角方向を  $\phi$  とする.

また、擬ラピディティ $\eta$  を使うことがしばしばある.これは衝突点からの天頂角  $\theta$  を用いて次式のように表される.

$$\eta = -\ln\left(\tan\left(\theta/2\right)\right)$$

$\eta, \phi$  で表すと生成粒子の分布が一様になることから、粒子のヒット位置を示すのによく用いられる. また、構成要素の検出器はシリンダー状の部分 (バレル部) とディスク状の部分 (エンドキャップ部) でできており、しばしば  $\eta$  の大小でこれらを区別する. 図 1.6 に座標系の概略図を示す.

図 1.6: ATLAS における座標系 [25]

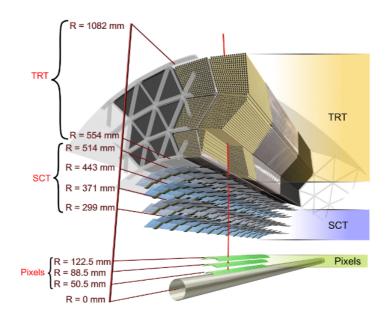

## 1.2.2 内部飛跡検出器

検出器の最内部において飛跡の再構成をするのが内部飛跡検出器 (ID: Inner Detecor) である. ATLAS の ID は内層のシリコン検出器及び外層の遷移放射検出器で構成される. 図 1.7 にバレル部 ID の概略図を示す. また, ID の性能は表 1.3 にまとめてある.

<sup>&</sup>lt;sup>4</sup>ATLAS 検出器がわずかに傾いて設置されているため、正確に天頂方向にはならない

図 1.7: バレル部 ID[6]

### シリコン検出器

ID 内層には飛跡再構成の要求精度を満たすため、分解能に優れるシリコン検出器を配置する. Pixel 検出器, Semi-Conductor Tracker (SCT) の 2 種類ある.

#### ● Pixel 検出器

シリコンピクセルを用いた高分解能の位置検出器である。バレル部は三層からなるが、第一層を特に B layer と呼び、2 次バーテックス $^5$ の同定に威力を発揮する

#### • SCT

シリコンマイクロストリップを用いた位置検出器である。ソレノイド磁場により曲げられた 荷電粒子の飛跡をとらえることで横運動量  $(p_{\mathrm{T}})$  の測定を可能にする

### 遷移放射検出器

ID を全てシリコンで作るのはコスト面で厳しい. 代わりに ID 外層には遷移放射 $^6$ を利用した検出器である Transition Radiation Tracker (TRT) を用いる. ストローチューブ検出器と, 遷移放射物質としてのポリプロピレンファイバーが互いに重なり合った構造をしており, ポリプロピレン

<sup>6</sup>荷電粒子が誘電率の異なる2つの物質の境界において起こす放射

からのX線をストローチューブ検出器が捉える。電子からは比較的エネルギーの大きNX線が放射されるため、弁別することができる。

表 1.3: ID の性能 [7]

| 検出器             | 検出領域 $( \eta )$ | 表面積 (m²) | チャンネル数 $(10^6)$ | 分解能 (μm)              |

|-----------------|-----------------|----------|-----------------|-----------------------|

| Pixel - B layer | -2.5            | 0.2      | 16              | $r\phi: 12, \ z: 66$  |

| Pixel - Barrel  | -1.7            | 1.4      | 81              | $r\phi:12,\ z:66$     |

| Pixel - Endcap  | 1.7 - 2.5       | 0.7      | 43              | $r\phi:12,\ z:77$     |

| SCT - Barrel    | -1.4            | 34.4     | 3.2             | $r\phi: 16, \ z: 800$ |

| SCT - Endcap    | 1.4 - 2.5       | 26.7     | 3.0             | $r\phi:16,\ z:800$    |

| TRT - Barrel    | -0.7            |          | 0.1             | 170/straw             |

| TRT - Endcap    | 0.7 - 2.5       |          | 0.3             | $170/\mathrm{straw}$  |

# 1.2.3 カロリメータ

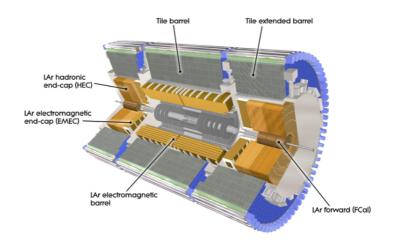

カロリメータは ID の外側において粒子のエネルギーや放出角度を測定する検出器である. 用途により電子や光子を検出する電磁カロリメータと, ジェットを検出するハドロンカロリメータに分かれる. 図 1.8 にカロリメータの概略図を示す.

図 1.8: カロリメータ [6]

### 電磁カロリメータ

鉛の吸収体とシンチレーション用の液体アルゴン (LAr) で構成されるサンプリングカロリメータである. 吸収体はアコーディオン構造になっており, 効率よくエネルギーを落とすことが可能. バレ

ル電磁カロリメータは  $|\eta|<1.48$  をカバーし、エンドキャップ電磁カロリメータは  $1.38<|\eta|<3.2$  をカバーする.

### ハドロンカロリメータ

バレル部  $(|\eta|<1.7)$  には鉄の吸収体とタイル状のシンチレータが交互に重ね合わさった構造をした Tile カロリメータが採用されている.一方エンドキャップ部  $(1.5<|\eta|<3.2)$  には鋼の吸収体と LAr で構成された Hadronic End-cap Calorimeter (HEC) を用いている.

#### フォワードカロリメータ

前方  $(3.1 < |\eta| < 4.9)$  をカバーするため、Forward Calorimeter (FCal) を設置している。第一層には銅の吸収体と LAr の電磁カロリメータ、第二、第三層にはタングステンと LAr のハドロンカロリメータを用いる。

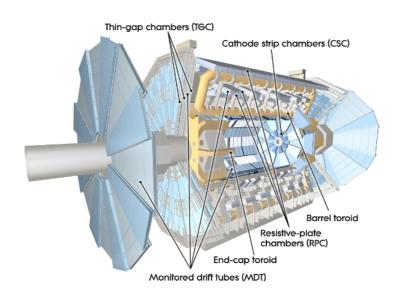

### 1.2.4 ミューオンスペクトロメータ

ミューオンスペクトロメータは ATLAS 検出器の最外部に配置されている, ミューオンの位置 測定等を行う一群の検出器のことである. 図 1.9 がミューオンスペクトロメータの概略図である. ATLAS のミューオンスペクトロメータは役割により Precision Chamber と Trigger Chamber に分かれる. Precision Chamber には磁場と垂直な方向 (r-z) の位置を  $50\mu m$  程度の精度で測定 することが求められる. 一方 Trigger Chamber には 25 ns 以内の応答,  $p_{\text{T}}$  測定によるトリガー, 数  $mm \sim 1 \text{cm}$  の精度での第二座標  $(\phi)$  測定が求められる. 各チェンバーの性能は表 1.4 にまとめてある.

図 1.9: ミューオンスペクトロメータ [6]

### **Precision Chamber**

高精度位置測定のため、Monitored Drift Tube (MDT) を用いる。 ただしフォワード領域 (2.1 <  $|\eta| < 2.7$ ) では高カウントレートに耐えられないため、Cathod Strip Chamber (CSC) を用いる.

#### • MDT

カソード径 30mm, アノード径  $50\mu m$  であるドリフトチューブが構成要素で, 1 本の位置分解能は  $80\mu m$  である. スペーサーフレームの両側に, ドリフトチューブを 3 本もしくは 4 本を層状に並べたものが 1 つのチェンバーになる

#### • CSC

ワイヤ間隔 2.54mm,ストリップ読み出し間隔 5.08mm の MWPC  $^7$  で,位置分解能  $60\mu$ m である.カウントレート上限が 150Hz/cm $^2$  の MDT に代わり,1000Hz/cm $^2$  の CSC がフォワード部の対応をする

### **Trigger Chamber**

ミューオントリガーはバレル部を Resistive Plate Chamber (RPC), エンドキャップ部を Thin Gap Chamber (TGC) が担当する.

### • RPC

高抵抗板を電極として用いるガス検出器の一種である。ATLAS では互いに直交するストリップを用いて  $z-\phi$  二次元情報を取得できるようにしており、バレル部のトリガーに用いられる

#### • TGC

ワイヤ間の間隔  $(1.8 \mathrm{mm})$  よりワイヤ・ストリップ間の距離  $(1.4 \mathrm{mm})$  の方が短いのが特徴的な MWPC である. これによりバンチ間隔である  $25 \mathrm{ns}$  以内に  $r-\phi$  二次元読み出しを可能にし, エンドキャップ部のトリガーに用いられる

|     | 表 1.4: ミュ       | ーオンスペクト     | ロメータの性能 [8]     |  |

|-----|-----------------|-------------|-----------------|--|

| 器出角 | 検出領域 $( \eta )$ | 表面積 $(m^2)$ | チャンネル数 $(10^4)$ |  |

| 検出器 | 検出領域 $( \eta )$ | 表面積 (m <sup>2</sup> ) | チャンネル数 $(10^4)$ | 分解能                |

|-----|-----------------|-----------------------|-----------------|--------------------|

| MDT | -2.7            | 5500                  | 37              | $80~\mu\mathrm{m}$ |

| CSC | 2.0 - 2.7       | 27                    | 6.7             | $60~\mu\mathrm{m}$ |

| RPC | -1.1            | 3650                  | 35.5            | ~1 mm              |

| TGC | 1.0 - 2.4       | 2900                  | 44              | ~ 1 cm             |

$<sup>^7</sup>$ Multi-Wire Proportional Chamber: 比例計数管の一種. ここではカソードをアノードワイヤと垂直なストリップ状にすることで二次元読み出しが可能なタイプである

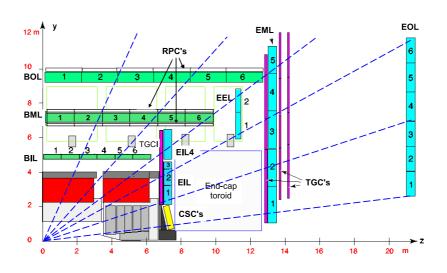

### レイアウト

ミューオンスペクトロメータを配置で分けると、いくつかのチェンバーでステーションという単位を作っている。 バレル部では 3 つのシリンダー状のステーション(Inner、Middle、Outer)、エンドキャップ部では 4 つのディスク状のステーション(I、M、O、Extra)が存在する。 これらをバレルを表す B、エンドキャップを表す E を用いて EM などと表記する。 また、EM ステーションを Big Wheel (BW)、EI ステーションを Small Wheel (SW) と呼ぶことがある。 これらのステーションはそれぞれ構成するチェンバーの種類が異なっており、内訳を表 1.5 にまとめる。

| ステーション | <b>検出領域</b> ( η ) | トラッキング               | トリガー | <br>第二座標測定           |

|--------|-------------------|----------------------|------|----------------------|

| BI     | -1.0              | MDT                  |      |                      |

| BM     | -1.0              | MDT                  | RPC  | RPC                  |

| В0     | -1.0              | MDT                  | RPC  | RPC                  |

| EI     | 1.0 - 2.0         | MDT                  |      | TGC                  |

|        | 2.0 - 2.7         | $\operatorname{CSC}$ |      | $\operatorname{CSC}$ |

| EM     | 1.0 - 2.4         | MDT                  | TGC  | TGC                  |

|        | 2.4 - 2.7         | MDT                  |      | TGC                  |

| EO     | 1.4 - 2.7         | MDT                  |      |                      |

| EE     | 1.0 - 1.4         | MDT                  |      |                      |

表 1.5: 各ステーションの構成 (Large sector)[8]

図 1.10: r-z 平面ステーション配置図 (Large sector)[6]

なお, 8 回対称のトロイド磁石に合わせて各ステーションも  $\phi$  方向に 16 分割されている. 8 つは バレルトロイド磁石の間の領域に位置し Large sector と呼ばれ, 8 つはバレルトロイドの直近に位

置し Small sector と呼ばれる. Large, Small で  $\eta$  の領域が若干ずれるが, 表 1.5 に載せたのは主に Large sector のものである. 図 1.10 に Large sector の配置図を示す.

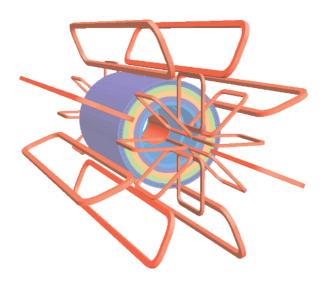

# 1.2.5 マグネット

荷電粒子の運動量測定のために、ATLAS では 2 種類の超伝導電磁石を用いている。 ソレノイド磁石と ATLAS の名前の由来にもなっているトロイド磁石である。 図 1.11 は 2 種類のマグネットの図である。

図 1.11: ソレノイド磁石, トロイド磁石 [6]

# ソレノイド磁石

ID の外側に z 方向約  $2{

m T}$  の磁場を発生させる超伝導ソレノイド磁石がある. 荷電粒子は  $\phi$  方向に曲げられ, ID で  $p_{

m T}$  が測定される.

# バレルトロイド磁石

バレル部はカロリメータの外側に長さ  $25\mathrm{m}$  のトロイド磁石がある. 8 つの超伝導コイルにより  $\phi$  方向に約  $0.5\mathrm{T}$  の磁場が発生する. 荷電粒子は  $\eta$  方向に曲げられ, RPC で  $p_\mathrm{T}$  が測定される.

# エンドキャップトロイド磁石

エンドキャップ部にも長さ  $5{\rm m}$  のトロイド磁石が存在する. 各コイルはバレル部のものと  $22.5^{\circ}$  ずつずれて配置されている.  $\phi$  方向約  $1{\rm T}$  の磁場により荷電粒子を曲げ,  ${\rm TGC}$  で  $p_{\rm T}$  を測定する.

# 1.3 トリガー及びデータ収集

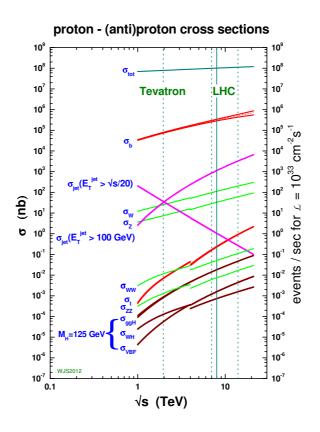

高エネルギー実験, 特に希少な事象を探索する ATLAS にとってトリガーシステムとデータ収集システム (DAQ: Data Acquisition) の性能は非常に重要である. 図 1.12 に断面積と重心エネルギーの関係を示す. これを見ればわかる通り, 14 TeV では Higgs は 10 億回に 1 回程度の割合しか生成されない. この膨大なバックグラウンドの中からいかに効率よく信号を選び出すかが ATLAS 実験の肝になる.

本節では ATLAS のトリガー及びデータ収集システム (TDAQ: Trigger and DAQ) について述べる.

図 1.12: 重心エネルギーに対する断面積プロット [13]

# 1.3.1 トリガー全体像

LHC では  $40 \mathrm{MHz}$  の頻度で衝突が起こり、一回の衝突で数 10 個の陽子が反応を起こす。そのうちほとんどは図 1.12 中の  $\sigma_{\mathrm{tot}}$  に表される minimum bias 事象である。エネルギーをほとんど落とさない "ケチな" 反応で、QCD (Quantum Chromodynamics) の効果で引き起こされる。これらを全て拾っていたのでは約  $1 \mathrm{GHz}$  でデータがくることになり、到底処理できない。

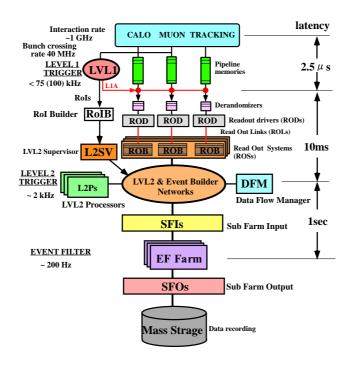

ATLAS では3段階のトリガーを用いてこのレートを200Hz 程度にまで落とす. Level 1 (L1) で75Hz, Level 2 (L2) で3.5kHz, Event Filter (EF) で200Hz, といった具合である(図1.13). L1 は

$2.5\mu s$  という厳しいレイテンシ条件からハードウェア処理により行われ、ソフトウェア処理の L2、 EF と区別される. このため L2、 EF をまとめて High Level Trigger (HLT) とも呼ぶことがある.

図 1.13: TDAQ 概要 [6]

# 1.3.2 Level 1 Trigger

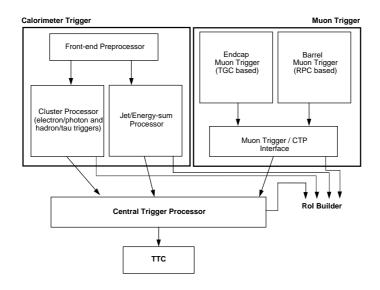

L1 はミューオンの  $p_{\rm T}$  情報及び電子、光子、ジェット等のエネルギー情報を用いてかけるトリガーである.  $p_{\rm T}$  情報は  ${\rm TGC}$ 、RPC から提供され、エネルギー情報は電磁/ハドロンカロリメータから精度を落としたものが提供される。 これら検出器のシステムと、情報を統合してトリガー判定を行う Central Trigger Processor (CTP)、さらにトリガーを分配する Timing Trigger and Control distribution system (TTC) [9] で L1 トリガーシステムを構成する。図 1.14 に L1 トリガーシステムの概要を示す。

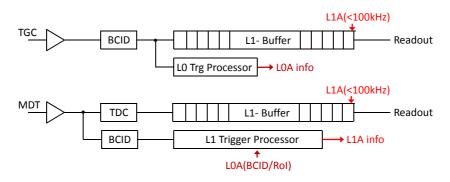

読み出しデータは L1 に与えられたレイテンシである  $2.5\mu s$  の間は保持しておかなければならないため、少なくとも 100 段のパイプラインメモリ (L1 Buffer) でトリガーの発行を待つ. CTP は現象に合わせて MU (muon), EM (electromagnetic), J (jet) 等のトリガーメニューを用意しており、いずれかの基準を満たした場合に  $Level\ 1$  Accept (L1A) 信号が発行される. L1A は TTC によりフロントエンドの L1 Buffer に行き着き、データが読み出される.

データはデランダマイザでトリガー発行のばらつきを吸収され, Read Out Driver (ROD) に送信される. ROD までを各検出器システムが担当しており, ROD はデータを ATLAS 共通のフォーマットに変換し, 後段の Read Out System (ROS) に送る. ROS は複数の Read Out Buffer (ROB) で構成されており, L2 の処理の間データを保持する. また, このデータフローとは別に, Region of Interest (RoI) 情報が L2 に渡される. RoI は L1 トリガーで得られた粒子の存在領域を  $\eta$  と  $\phi$  で表したものであり, L2 トリガーに使用される.

図 1.14: L1 トリガーシステム [6]

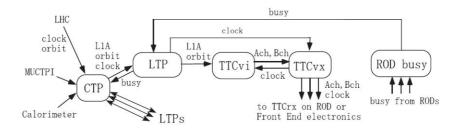

#### TTC

TTC は各検出器システムのフロントエンドにタイミング/トリガー信号をブロードキャストしたり、フロントエンドに個別にコマンドを送るために用いられる。タイミング/トリガー信号にはクロック、 ${

m L1A,\ ECR^{8}}$ , ${

m BCR^{9}}$  等がある。

図 1.15 のように、TTC は Local Trigger Processor (LTP)、TTCvi、TTCvx、ROD busy から構成されている。LTP は各検出器システムごとにおかれ、ローカルにおけるマスターの役割を果たす。CTP からタイミング/トリガー情報を受け取り、クロックを TTCvx に、他を TTCvi に渡す。この際、例えばトリガーに関して L1A をそのまま渡すか、ローカルに生成されたトリガーを用いることができるなど、ローカルでの運用も可能になっている。

図 1.15: TTC を構成するモジュール [23]

TTCvi は受け取った情報を元にトリガーを A-Channel, その他の信号を B-Channel としてコーディングして TTCvx に渡す. TTCvx は 2 種類の信号を TDM <sup>10</sup> により多重化し, 光信号により

$<sup>^8{\</sup>rm Event}$  Count Reset: イベントカウントのリセット

<sup>&</sup>lt;sup>9</sup>Bunch Count Reset: バンチカウントのリセット

<sup>&</sup>lt;sup>10</sup>Time Division Multiplexing: 時間ドメインを分割することで複数のチャンネルを同時に送信する技術

フロントエンドに分配する. RODbusy モジュールは ROD からの busy 信号をまとめ, LTP を経由して CTP へと受け渡す. busy は ROD が何らかの原因で処理が追いつかない場合に発行され, L1A の発行を停止させる.

フロントエンドで TTC 信号を受け取るには、TTCrx ASIC  $^{11}$  を搭載したモジュールを用いる。 TTCrx は TTC 信号をデコードしてタイミング/トリガー情報を再生する。例として TGC フロントエンドでは、TTCrx を載せた TTCrq メザニンカードによりデコードし、ファンアウトモジュールを介して各 L1 Buffer にトリガーを配っている。

# 1.3.3 High Level Trigger

L2 では L1 より高精度なトリガー判定を行うため、L1 で用いられなかった MDT、 CSC、ID 等の情報にもアクセスできるようにする。 ただし 40ms のレイテンシ制約があるため、RoI 情報を元に適切なデータを ROS から取り出す。 L2 トリガーメニューを用いて L2 判定が行われ、通ると L2 Accept (L2A) が発行される。 L2A が発行されると、ROS に格納されていた全データは Sub Farm Input (SFI) buffer に移され、所定のフォーマットに変換される。

EF では RoI で限定せず全てのデータを用いてトリガー判断を下す. トリガー判定は複数の EF Sub Farm から構成された EF Farm において、並列処理により行われている. EF Sub Farm は SFI からデータを受け取り、最大 4sec かけてトリガーを発行する. EF を通過すると、該当データとトリガー情報が Sub Farm Output (SFO) buffer に渡され、最終的なディスクへの書き込みが行われる.

# 1.4 ATLASで目指す物理

ATLAS の主目的の 1 つとして Higgs 粒子の探索及び精密測定が挙げられる. Higgs は存在を予言されてから 50 年近く様々な実験で探索が続けられてきた. 2011 年までには LEP により 114 GeV 以下の領域が, Tevatron 12 により 156-177 GeV の領域が, LHC により 141-476 GeV の領域がそれ ぞれ 95% の確度で棄却されており, 2012 年の結果に期待が寄せられていた.

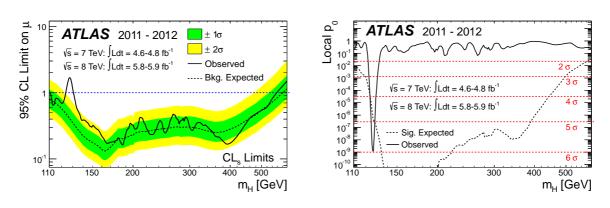

図 1.16: 2012 年 7 月時点でのプロット [5]

そしてついに 2012 年 7 月, ATLAS は 126GeV に "新しいボソン" を発見した (図 1.16). 今後はこの粒子が本当に Standard Model (SM) の Higgs 粒子なのか確認するとともに、プロパティ測定のフェーズに突入する.

本節ではLHCでのHiggsの精密測定を中心に、ATLASで検証する物理について説明する.

## 1.4.1 Standard Model Higgs

SM Higgs の簡単なおさらいをしておく. 電弱相互作用のラグランジアンは

$$\mathcal{L}_{1} = -\frac{1}{4} \mathbf{W}_{\mu\nu} \cdot \mathbf{W}^{\mu\nu} - \frac{1}{4} B_{\mu\nu} \cdot B^{\mu\nu}$$

$$+ \overline{L} \gamma^{\mu} \left( i \partial_{\mu} - g \frac{1}{2} \boldsymbol{\tau} \cdot \mathbf{W}_{\mu} - g' \frac{Y}{2} B_{\mu} \right) L$$

$$+ \overline{R} \gamma^{\mu} \left( i \partial_{\mu} - g' \frac{Y}{2} B_{\mu} \right) R$$

である. これではゲージボソンの質量が 0 であるため,  $W^\pm$  及び  $Z^0$  が質量をもち,  $\gamma$  は質量が 0 であるように, スカラー場  $\phi$  に対して  $SU(2)\times U(1)$  不変なラグランジアンを付け加える.

$$\mathcal{L}_{2} = \left| \left( i \partial_{\mu} - g \frac{1}{2} \boldsymbol{\tau} \cdot \boldsymbol{W}_{\mu} - g' \frac{Y}{2} B_{\mu} \right) \phi \right|^{2} - V(\phi)$$

$$V(\phi) = \mu^{2} \phi^{\dagger} \phi + \lambda (\phi^{\dagger} \phi)^{2} \quad \text{where } \mu^{2} < 0 \text{ and } \lambda > 0$$

さらにフェルミオンの質量を求めるには次のラグランジアンを加える.

$$\mathcal{L}_3 = -\left(G_1\overline{L}\phi R + G_2\overline{L}\phi_c R + \text{Hermitian Conjugate}\right)$$

対称性の自発的破れを考慮して

$$\phi = \frac{1}{\sqrt{2}} \begin{pmatrix} 0 \\ \nu + h \end{pmatrix}, \quad \phi_c = -i\tau_2 \phi^*$$

とすることにより、フェルミオンの質量項が無事に出てくる.ここで  $\nu$  は  ${

m Higgs}$  の真空期待値  $(246{

m GeV})$  である.ベクターボソン W 、 Z とフェルミオンの質量は  ${

m SM}$  では導くことのできないパラメータであり、結合定数と次のような関係になっている.

$$g_{ffH} = \frac{m_f}{\nu}$$

$$g_{VVH} = 2\frac{m_V^2}{\nu}$$

フェルミオンの質量と  ${

m Higgs}$  の結合定数 (湯川結合定数と呼ばれる) は比例関係になっているので、測定でこのリニアリティを再現できればボソンが  ${

m Higgs}$  だという傍証になる。また、 ${

m Higgs}$  の質量  $m_H=\sqrt{2\lambda}\nu$  は  ${

m SM}$  からは予言できない量であり、測定により求める。スピン及びパリティは  $J^{PC}=0^{++}$  とされているが、こちらも実験により確かめる必要がある。

# 1.4.2 Higgs 生成過程

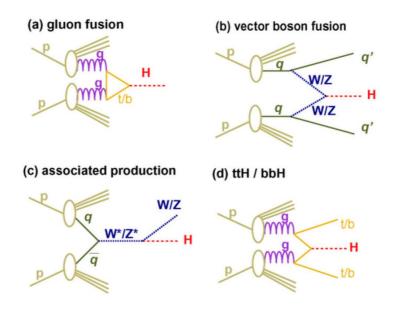

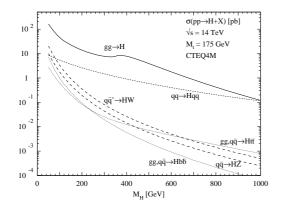

Higgs の主な生成過程として.  $gg \to H$  (gluon fusion),  $qq \to qqH$  (vector boson fusion),  $q\bar{q} \to (W/Z)H$  (W/Z associate production),  $gg \to ttH$  (top associate production) の 4 つが挙 げられる. 図 1.17 に各生成過程のファインマン図を示す. また, Higgs の生成断面積は図 1.18 のようになる.

図 1.17: Higgs 生成過程 [23]

gluon fusion (GF): ~30pb @ $m_H = 125 \text{ GeV}$

グルーオンは質量をもたないので Higgs とは結びつかないが、重いクオークのループを介して Higgs を生成する. LHC では最も断面積が大きいためメインの生成過程であるが、ほかに高い  $p_T$  の粒子が出てこないためバックグラウンドとの選別が難しい.

vector boson fusion (VBF): ~5pb @ $m_H = 125 \text{ GeV}$

クオークから出たベクターボソン (W,Z) が結合する過程で、2 番目に断面積が大きい. GF に比べて断面積は 1/6 程度だが、反跳クオークの高  $p_T$  ジェットが出るのでバックグラウンドとの選別は比較的容易.  $\eta-\phi$  平面でラピディティのギャップができることが特徴.

W/Z associated production (WH/ZH): ~3pb @ $m_H = 125$  GeV

粒子・反粒子の対消滅で生じたベクターボソンから制動放射の形で Higgs が放出される過程である. W/Z がレプトン崩壊を起こした場合にバックグラウンドとの識別が容易である. LHC では断面積が大きくならないが、LEP や Tevatron などではメインとなる生成過程である.

top associated production (ttH): ~0.5pb @ $m_H = 125 \text{ GeV}$

グル オンから対生成した t から  $\mathrm{Higgs}$  が生成される. t は b と W  $(qq \text{ or } l\nu)$  に崩壊し特徴的な信号を出すので識別が可能である.

図 1.18: Higgs 生成断面積 [11]

図 1.19: Higgs 崩壊分岐比 [11]

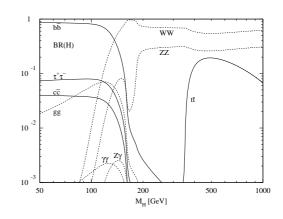

# 1.4.3 Higgs 崩壊過程

${

m Higgs}$  の崩壊過程は複数種類考えられるが、その中でも重要な 5 つのチャンネルを考える. 崩壊分岐比は図 1.19 のようになる.

$$H \rightarrow \gamma \gamma$$

: ~ 0.2% @ $m_H = 125 \text{ GeV}$

Higgs が 2 つの光子に崩壊する過程. 光子は電磁カロリメータでしか捕捉できないため, カロリメータの性能にかかっている. エネルギー, 角度を高い精度で測定することができれば, 不変質量が Higgs の質量の部分で鋭いピークが見える. このため質量の測定にも用いられる. 不変質量と測定値の間には次の関係がある.

$$m^2 = 2E_{\rm T1}E_{\rm T2}\left(\cosh(\Delta\eta) - \cos(\Delta\phi)\right)$$

$H \to WW^* \sim 22\% @m_H = 125 \text{ GeV}$

${

m Higgs}$  が 2 つの W に崩壊し、それぞれが  $l\nu$  (l は  $\mu$  もしくは e) に崩壊する過程で、最も発見感度の高いチャンネルの一つ.  $\nu\nu$  ペアの  ${

m mET}$  ( ${

m missing}$   $E_{

m T}$ ) と ll ペアで横方向質量  $(m_{

m T})$  を組むとヤコビアンピークが見える.

$$m_{\mathrm{T}} = \sqrt{\left(E_{\mathrm{T}}^{ll} + \cancel{E}_{\mathrm{T}}\right)^{2} + \left(\vec{p}_{\mathrm{T}}^{ll} + \cancel{p}_{\mathrm{T}}\right)^{2}}$$

${

m Higgs}$  のスピンが 0 であることを用いて, 2 つのレプトンが同じ方向に出てくることを要求すれば  ${

m S/N}$  が良くなる.

$H \to ZZ^* \sim 3\% @m_H = 125 \text{ GeV}$

Higgs が 2 つの Z に崩壊し、それぞれが ll に崩壊する過程で、Higgs が重い場合にはメインとなっていたチャンネルである (golden channel). on-shell の Z が崩壊したレプトンの組は不変質量が  $91 {\rm GeV}$  になるので、これを用いてバックグラウンドを落とせる。4 つのレプトンの不変質量を計算すると細いピークが現れるので質量測定に貢献できる上、角度分布からはスピンと  ${\rm CP}$  を決定することができる.

$$H \to \tau \tau \sim 6\% \ @m_H = 125 \ {\rm GeV}$$

${

m Higgs}$  が 2 つの au に崩壊する過程である. au は  $l\nu_l\nu_{ au}$  か  $h\nu_{ au}$  に崩壊するが, 2 つのうち少なくとも 片方がレプトン崩壊したものを用いる. バックグラウンドの  ${

m Drell}$   ${

m Yan}$  au のエネルギー分布の肩に 乗る形で緩やかなピークが立つ.  $g_{\tau\tau H}$  のためにも重要なチャンネル.

$$H \to bb \sim 58\% @m_H = 125 \text{ GeV}$$

${

m Higgs}$  が 2 つの b に崩壊するチャンネルで分岐比は最も大きい。しかし信号と区別できない QCD バックグラウンドが非常に多く, qar q o (W/Z)H と併せて用いられるため, 最終的な断面積は小さくなる。  $g_{bbH}$  の測定に必要なチャンネルだが, 他の湯川結合より精度は落ちる.

## 1.4.4 プロパティ測定のまとめ

ここで生成・崩壊過程を踏まえてこれからの Higgs のプロパティ測定についてまとめる.

#### 質量

質量は  $H\to\gamma\gamma$  及び  $H\to ZZ^*$  で測定される。 $300{\rm fb}^{-1}$  で ~ 0.1%程度の精度が見込まれる。質量からは SM Higgs の確証は得られないので、後述のスピン・パリティ及び湯川結合定数を求める必要がある。なお崩壊幅については、ATLAS の  $1{\rm GeV}$  の分解能を下回るので測定できない。

### スピン・パリティ

$H \to ZZ^*$  において 4 つのレプトンの放出された角度を調べることで、スピン及びパリティを調べることができる。レプトン対の作る平面同士の角を  $\phi$ , Z の方向からの天頂角を  $\theta$  とし、 $\theta$  と  $\phi$  の分布を次の関数でフィットする。

$$F(\phi) = 1 + \alpha \cdot \cos(\phi) + \beta \cdot \cos(2\phi)$$

$$G(\theta) = T \cdot (1 + \cos^2(\theta)) + L \cdot \sin^2(\theta)$$

$\alpha$ ,  $\beta$ , R=(L-T)/(L+T) を理論値と比較することで, スピンと CP を推測できる.  $300 {\rm fb}^{-1}$  あれば  $5\sigma$  でスピン・パリティを決定できると予想される.

### 結合定数

各結合定数を求めるには、生成断面積  $(\sigma)$  と分岐比 (BR: Branching Ratio) との積が、観測されたイベント数 N と次の関係にあることを用いる.

$$\sigma \times \mathrm{BR} = \frac{N-B}{L \cdot \epsilon}$$

B は推測されるバックグラウンド, L は積分ルミノシティ,  $\epsilon$  はアクセプタンスである. 表 1.6 に生成断面積, 分岐比と結合定数の関係を表す.  $\alpha$ ,  $\beta$  は SM から導ける数である.

|                | σ                                                                             |                       | BR                                                                               |

|----------------|-------------------------------------------------------------------------------|-----------------------|----------------------------------------------------------------------------------|

| GF             | $lpha_{	ext{GF}} \cdot g_{ttH}^2$                                             | $H \to \gamma \gamma$ | $(\beta_{\gamma W} \cdot g_{WWH} - \beta_{\gamma t} \cdot g_{ttH})^2 / \Gamma_H$ |

| VBF            | $\alpha_{\mathrm{WF}} \cdot g_{WWH}^2 + \alpha_{\mathrm{ZF}} \cdot g_{ZZH}^2$ | $H \to WW^*$          | $eta_Z \cdot g_{ZZH}^2/\Gamma_H$                                                 |

| WH             | $lpha_{	ext{WH}} \cdot g_{WWH}^2$                                             | $H 	o ZZ^*$           | $eta_W \cdot g_{WWH}^2/\Gamma_H$                                                 |

| ZH             | $lpha_{	ext{ZH}} \cdot g_{ZZH}^2$                                             | H 	o 	au	au           | $eta_	au \cdot g_{	au	au H}^2/\Gamma_H$                                          |

| $\mathrm{ttH}$ | $lpha_{	ext{ttH}} \cdot g_{ttH}^2$                                            | H 	o bb               | $eta_b \cdot g_{bbH}^2/\Gamma_H$                                                 |

表 1.6: 生成断面積, 分岐比と結合定数

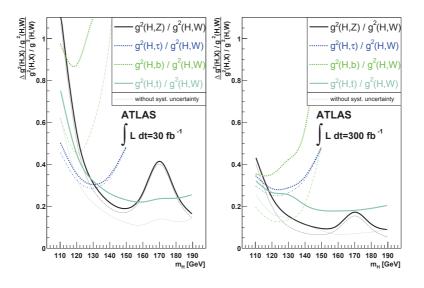

湯川結合定数のリニアリティが確かめられれば SM Higgs であることの証拠になることは述べた。これには  $g_{ttH}$ ,  $g_{bbH}$ ,  $g_{\tau\tau H}$  の 3 点を測定すればよい。生成過程の中では GF, ttH が  $g_{ttH}$  測定に使える。  $g_{bbH}$ ,  $g_{\tau\tau H}$  の測定にはそれぞれ  $H\to bb$ ,  $H\to \tau\tau$  の崩壊を用いる。 ただし  $\Gamma_H$  を測定することができないので,結合定数を直接求めるのではなく相対値を用いる。  $g_{WWH}$  を基準とした場合の結合定数の測定精度を図 1.20 に示す。図より  $300 {\rm fb}^{-1}$  では  $20 \sim 40\%$  で測定可能であることがわかる。しかしより精密に測定するためにルミノシティを上げて多くのデータを貯める必要がある。

図 1.20: 結合定数の測定精度 [12]

また、Higgs には3点及び4点自己結合が存在し、それぞれ結合定数は次の式で表される。

$$\lambda_{HHH} = 3 \frac{m_H^2}{\nu}$$

$$\lambda_{H\!H\!H\!H} = 3 \frac{m_H^2}{\nu^2}$$

これらは  ${

m Higgs}$  を 2 つ生成する過程を経なければならず、生成断面積が非常に小さいので現状では到達できない。 少なくとも  $3000{

m fb}^{-1}$  程度ないと発見には至れないため、ルミノシティ増加が望まれる。

# 1.4.5 アップグレードに向けて

2012 年までに Higgs らしきボソンを発見したが、あくまで LHC の 1 つの目的を果たしたに過ぎない。LHC は TeV 領域を探索できる唯一の加速器であるため、LHC にしかできない物理探索のためにも邁進すべきである。本章で説明した Higgs の精密測定の他にも、超対称性粒子(SUSY  $^{13}$ )を始めとした Beyond Standard Model (BSM) 物理の探索が求められる。これらを達成するにはより高いルミノシティを目指してアップグレードする必要があり、LHC 並びに ATLAS はすでに準備を進めている。

LHC ではビームエネルギーをデザイン値の 7TeV に, ルミノシティをデザイン値の 5 倍の  $5\times 10^{34}~\rm cm^{-2}s^{-1}$  まで引き上げる計画を立てている。これを High-Luminosity LHC (HL-LHC) 計画と呼び, 2030 年頃までに積分ルミノシティ $3000 {\rm fb^{-1}}$  を目指している。それに対応できるよう ATLAS でも損傷した検出器の交換やエレクトロニクスのアップグレードをしていく予定である。

この HL-LHC で期待される物理について、ほんの一部であるが以下に例を挙げる.

- ◆ Higgs の結合定数の精密測定,及び自己結合定数の観測

- TeV スケールにおけるベクターボソン散乱過程を通した SM 精密測定

- SUSY の一種である squark (~3TeV), gluino (~2.5TeV) の制限

- W', Z' による新しい相互作用や余剰次元の探索

次節からは具体的なアップグレードの中身について見ていくことにする.

<sup>&</sup>lt;sup>13</sup>SuperSynmetry: ボソンとフェルミオンの入れ替えに対する対称性

# 1.5 LHC アップグレード計画

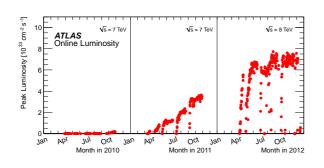

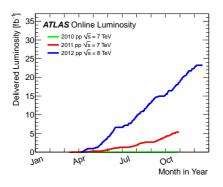

LHC は 2009 年の  $900 {\rm GeV}$  ランに始まり 2010, 2011 年の  $7 {\rm TeV}$  ラン、2012 年の  $8 {\rm TeV}$  ランと順調に重心系エネルギーを増強してきた。積分ルミノシティについては 2010 年は  $50 {\rm pb}^{-1}$  程度しか貯められなかったが,2011 年には  $5 {\rm fb}^{-1}$  を超え,2012 年はその 4 倍もの積分ルミノシティを貯めることができた。図 1.21 に瞬間ルミノシティ及び積分ルミノシティの変遷を載せる.

図 1.21: ルミノシティの変遷 [5]

2012 年が終わると断続してきた物理ランに一区切りがつき、Long Shutdown (LS) に入る. LS 中は LHC の補修作業やアップグレードに充てられ、一切の物理ランは行われない. LS は今後 10 年程度の間に 3 回予定されており、そのたびに少しずつ LHC をアップグレードしてエネルギー及びルミノシティを増強していく。2013-2014 年が LS1、2018 年が LS2、2022 年が LS3 となっており、LS3 をもって瞬間ルミノシティ $5 \times 10^{34}$  cm $^{-2}$ s $^{-1}$  の HL-LHC となる。表 1.7 にこのロードマップをまとめる。

| 年               | エネルギー (TeV) | 瞬間ルミノシティ $(cm^{-2}s^{-1})$ |

|-----------------|-------------|----------------------------|

| 2012<br>2013-14 | 4           | $6 \times 10^{33}$ (LS1)   |

| 2015-17<br>2018 | 6.5 ~ 7     | $1 \times 10^{34}$ (LS2)   |

| 2019-21<br>2022 | 7           | $2 \times 10^{34}$ (LS3)   |

| 2023-           | 7           | $5 \times 10^{34}$         |

表 1.7: HL-LHC へのロードマップ

なお、 $\rm HL\text{-}LHC$  ではルミノシティのレベリングを行う予定である。つまり何もしなければ  $10 \times 10^{34} \rm cm^{-2} s^{-1}$  程度出るところを、あえてビーム軸をずらしたりビームの絞りを動的に変更したりして  $5 \times 10^{34} \rm cm^{-2} s^{-1}$  に抑える。こうすることで高ルミノシティに伴うパイルアップの増加を抑制し、効率的にデータを収集できる。また、程度の差こそあれ  $\rm LS1$ 、 $\rm LS2$  後の  $\rm LHC$  でもレベリングを行う可能性はある。

以下に各LSでどのような作業が予定されているか、検討中のものも含めて記す.

# 1.5.1 Long Shutdown 1 (2013-2014)

主にエネルギーを 4TeV から 6.5 または 7TeV に引き上げる準備のためのシャットダウンである. 加速管同士の接合を強化する, 弱くなっている磁石を交換する, 放射線対策のためにエレクトロニクスを移動する, 等の作業が考えられている.

# 1.5.2 Long Shutdown 2 (2018)

ルミノシティを 2 倍に引き上げる. LIU (LHC Injectors Upgrade) と呼ばれるインジェクタのアップグレードが予定されており, Linac2 から Linac4 への移行, PS Booster のエネルギー増加, SPS の電子雲対策などが考えられている. Linac2 では 50MeV までしか加速しないが, Linac4 では 160MeV になり, PS Booster は 1.4GeV から 2GeV になる. PS Booster においては, J-PARC 14 の金属磁性体合金を用いた高周波加速空洞が採用されるなど、日本の寄与が大きい.

# 1.5.3 Long Shutdown 3 (2022)

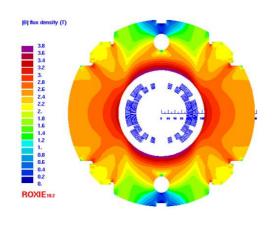

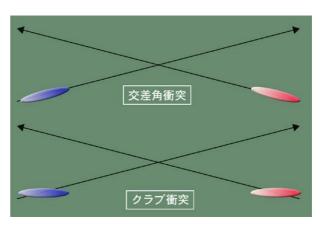

ルミノシティを最終的な  $5\times 10^{34} {\rm cm}^{-2} {\rm s}^{-1}$  まで上げる. Interaction Region (IR) の磁石の強化、超伝導クラブ空洞の導入が挙げられる. IR の磁石にはビーム収束用の四重極磁石 (Q1, Q2, Q3) とビーム分離・再結合用の双極子磁石 (D1, D2) がある. このうち KEK  $^{15}$  が D1 を制作することを検討しており、 $6{\rm T}$  級の大口径磁石を作るための R&D が行われている. 図 1.22 に現在検討中の磁石の断面図を載せる. また、クラブ空洞を用いると、バンチの向きを回転させることでビーム強度が少なくなっても高ルミノシティを保つことができる. これは KEKB 加速器 $^{16}$  で世界で初めて実用化した技術であり、技術協力等を通して日本が貢献していく方針である. 図 1.23 にクラブ衝突の概念図を載せる.

図 1.22: 検討中の D1 磁石 [32]

図 1.23: クラブ衝突の概念図 [31]

<sup>14</sup> Japan Proton Accelerator Research Complex: KEK と日本原子力研究開発機構による大強度陽子加速器

<sup>&</sup>lt;sup>15</sup>高エネルギー加速器研究機構: 高エネルギー物理や加速器物理, 物質構造化学等の総合研究機関

$<sup>^{16}{</sup>m KEK}$  の所有する周長約  $3{

m km}$  の加速器.  $8{

m GeV}$  の電子と  $3.5{

m GeV}$  の陽電子を衝突させる

# 1.6 ATLAS アップグレード計画

ルミノシティが上がるにつれ、パイルアップの他にもさまざまな問題が噴出する.

- 読み出し回路やトリガー回路の負担が大きくなる

- 検出器自体の放射線損傷が早まる

- cavern background <sup>17</sup>が増える

これらに対応していくため、ATLAS のアップグレードは 3 回の LS に合わせて部分的に行われていく、LS1 におけるアップグレードを phase-0 upgrade, LS2 は phase-1 upgrade, LS3 は phase-2 upgrade と呼んでいる。以下それぞれのフェーズでどこをアップグレードしていくかを説明する.

# 1.6.1 phase-0

phase-0 ではデザインルミノシティとエネルギーに対して弱いと思われる部分を補強するアップグレードを行う. 具体的には Insertable B Layer の導入及びミューオンシステムの改善が挙げられる.

# Insertable B Layer

現在の Pixel 検出器のバレル部は 3 層構造になっていて、最も内側の B Layer はバーテックスの特定、ひいては b タグに必須の検出器である。ルミノシティ上昇に伴い、B Layer を交換する代わりに B Layer とビームパイプの間に新たにピクセル検出器 (IBL: Insertable B Layer) を挿入する。IBL は最も IP  $^{18}$  に近い (3.27cm) 部分に位置するのでトラッキングの精度が向上し、b タグの効率が向上する。ピクセル検出器としてはプラナー型のものと、新しい技術である 3D 型のものを混載させるようである。3D 型はプラナー型に比べ消費電力が小さい、電荷収集時間が短い等のメリットがある。逆に欠点としてはプラナー型より厚い、制作コストが高い、等が挙げられる。

図 1.24 に現在の Pixel の写真と IBL のイメージを示す.

図 1.24: IBL 挿入前後のイメージ [15]

<sup>&</sup>lt;sup>18</sup>Interaction Point: 陽子と陽子の衝突地点

## ミューオンスペクトロメータの改善

現在 Endcap Extra (EE) Chamber は穴があり、エンドキャップ部とバレル部の境の領域( $1.0 < |\eta| < 1.3$ )のトラッキング効率がひどく低い、そのため残りをインストールすることでこの穴を埋めることは重要課題である。また、カロリメータとシールディングディスクの間 ( $z \simeq 7 \mathrm{m}$ ) はビームパイプがシールドされておらず、光子や中性子が漏れ出てくる。この対策のため新たなシールドを設置する。

# 1.6.2 phase-1

phase-1 ではL2 で行われていたトリガーの一部をL1 に移すなど、トリガーの強化が行われる. 主なアップグレードには New Small Wheel, High Granularity Calorimeter Trigger, Fast TracKer, Forward Physics System の導入が挙げられる.

#### New Small Wheel

現在 Small Wheel (SW) の MDT 及び CSC が  $1.3 < |\eta| < 2.7$  におけるトラッキング情報を生成している。この SW を、高精度のトラッキング用検出器とトリガー用チェンバーからなる New Small Wheel (NSW) に取り換える計画である。動機としては以下の 2 点存在する.

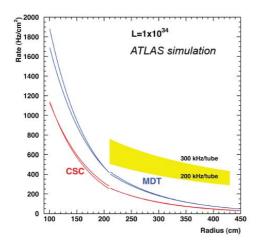

1. SW の MDT がデザインルミノシティ以上で性能が劣化する 図 1.25 のように MDT は  $1\times10^{34} {\rm cm}^{-2} {\rm s}^{-1}$  の時点で対レートマージンが少ないため, phase-1 の前に適切な検出器に取り換える必要がある

# 2. フェイクトリガーを落とす

現在 L1 ミューオントリガーの約 98% はフェイクミューオンでかかってしまっている. これはミューオン以外の荷電粒子によるバックグラウンドの存在や,  $p_{\rm T}$  分解能が悪いために生じる. 詳細は後の章で述べるが, NSW のヒット情報を用いることでこれらを排除し, 3 割程度にレートを落とすことができる

図 1.25: 予測されるカウントレート [14]

図 1.26: MicroMegas の概略図 [14]

ATLAS Phase-1 Upgrade Letter of Intent[14] 発行時点では、NSW 候補として既存の SW を改善した形の small tube MDT (sMDT)+ small wheel TGC (sTGC), sMDT + RPC の 2 案及び、新しい技術である MicroMegas (MM) の 3 種類が挙がっていたが、最終的には MM + sTGC の組み合わせに決定した。

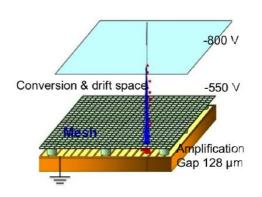

${

m MM}$  に入射したミューオンは電極と金属製のメッシュの間の数  ${

m mm}$  にわたる領域でイオン対を生成し、電子はメッシュに向かってドリフトする。 メッシュと読み出し電極の間には  $100\mu{

m m}$  しかなく高電場  $(40{

m kV/cm}$  程度) がかかっているので、ドリフト電子はメッシュを通過して電子雪崩により  $10^4$  倍に増幅する。 陽イオンが比較的早く ( $\sim 100{

m ns}$ ) 捌けるのでトリガーとしても用いることができる。図 1.26 に  ${

m MM}$  の概略図を示す。

${

m sTGC}$  はカソードストリップの抵抗率を低減することで、 $30~{

m kHz/cm^2}$  の高レートまで耐えられるようにした TGC である。 ${

m MM,\,sTGC}$  ともに  $100\mu{

m m}$  よりも良い分解能が得られる。

# High Granularity Calorimeter Trigger

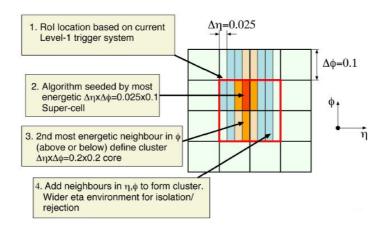

ルミノシティが上がると、ジェットを電子と誤ることに起因して、カロリメータによる L1 トリガーレートが大きくなる。トリガーレートを  $20 \mathrm{kHz}$  に保つには閾値を  $40 \sim 50 \mathrm{GeV}$  程度まで上げるしかないが、そうすると W , Z からの大事な信号をロスしてしまう。そこでシャワーの横方向の形を用いたカットにより電子由来のシャワーとジェットを分離するアルゴリズムが考えられた。

3層の電磁カロリメータのうち 2 層目において、従来の L1 であれば  $\Delta\eta \times \Delta\phi = 0.2 \times 0.2$  の RoI で取っていたが、その中から最もエネルギーの大きい  $0.025 \times 0.1$  を "Super-cell" として選び、そこを中心に  $0.075 \times 0.2$  及び  $0.175 \times 0.2$  の領域を定義してエネルギーの比をとる:

$$R_{\eta} = \frac{E_{3\times2}}{E_{7\times2}}$$

この R でカットをかけると効率的にジェットを落とせる (1/3 程度). L2 で行っていたことを L1 に持ち込んでいるということだが、フロントエンド読み出し回路及び L1 トリガー入力部の部分的 なアップグレードによりこれを達成する. 図 1.27 にこの概念図を示す.

☑ 1.27: High Granularity Calorimeter Trigger[14]

#### Fast TracKer

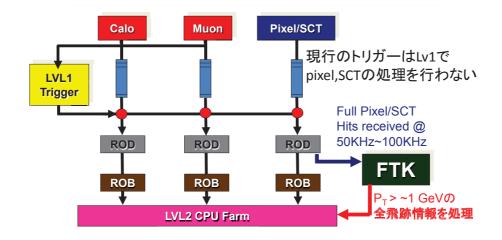

Fast TracKer (FTK) は L1 と L2 の間の "L1.5" として機能するプロセッサである. 通常トラッキングは L2 で行われ数  $100 \mathrm{ms}$  かかるが、粗いトラックを  $100 \mu \mathrm{s}$  以内に出して L2 に渡すことを目的とする.

入力データは L1 トリガーを通過した Pixel と SCT を用いる. FTK はこれらのコピーを受け取り、ハードウェアによりパターン認識とトラックフィットを行う. 平均  $25\mu s$  でオフラインに近い精度でトラックを割り出せることが確かめられている. FTK により b タグ、 $\tau$ -ID、レプトンアイソレーション等の効率が上がることが期待される. 図 1.28 に FTK とトリガーフローの関係を示す.

図 1.28: FTK とトリガーフロー [21]

# Forward Physics System

IP から約 210m の部分に ATLAS Forward Proton detector (AFP) を置き, フォワード領域の 物理探索を行うものである. BSM である  $\gamma-W/Z$  のアノーマラスカップリング測定, 及び QCD 回折物理検証が含まれる.

これらの測定のため、2 種類の AFP を用意する。206m の AFP1 は 3D シリコン検出器であり、214m の AFP2 は 3D シリコン検出器及びタイミング検出器からなる。このタイミング検出器は水晶チェレンコフ検出器とマイクロチャネル PMT  $^{19}$  で構成され、時間分解能 10ps を達成する。

## 1.6.3 phase-2

phase-2 に関してはまだ詳細が決まっているわけではないが、ここでは現段階で考案されている主なものについて述べる.

<sup>&</sup>lt;sup>19</sup>Photomultiplier Tube: 光電効果で出てきた電子を増幅する仕組みの, 高感度の光検出器

## 内部飛跡検出器

一点目には ID の総取り換えが挙げられる。 Pixel と SCT については総線量が許容量に達するため,TRT は瞬間ルミノシティ $5 \times 10^{34} {

m cm}^{-2} {

m s}^{-1}$  に耐えられないため,交換が必要になる。 その際 TRT を撤廃して全てシリコンベースの検出器にすることが検討されている。 現段階の案では, Pixel はチャンネル数は 5 倍になり  $|\eta| < 2.7$  をカバーし,SCT はチャンネル数 7.5 倍で  $|\eta| < 2.5$  をカバーする。図 1.29 に新しい ID の例を示す.

図 1.29: 新しい ID のイメージ [16]

# カロリメータ

カロリメータに関しても、やはりデザインルミノシティを大きく超える phase-2 ではアップグレードが必要になる。一点目は、総線量の限界から各種エレクトロニクスを交換することである。 Tile カロリメータと電磁カロリメータでは読み出しエレクトロニクスをアップグレードしたものに交換する。 HEC のプリアンプとエレクトロニクスは冷却器の中にあるので、後述の FCal の議論と合わせて交換が必要かを慎重に検討する必要がある。

二点目に、瞬間ルミノシティの増加により FCal が正常に働かなくなることが予期されているので、その対策を講じることである。 2 案考えられていて、1 つは FCal を完全に交換してしまう案 (sFCal) と、現在の FCal の手前に小さなカロリメータを配置する案 (Mini-FCal) である。 sFCal にする場合は FCal を取り出すために冷却器を開かなければならない。

# トリガースキーム

フェイクミューオンを減らすため、大幅なトリガースキームの変更が検討されている。 ハードウェアによるトラッキングトリガーを導入するために HLT 以前を 2 段階に分割する。 これを新しい L0/L1 トリガーとするが、まだ詳細は決まっていない。

# 第2章 レベル1エンドキャップミューオントリ ガーシステム

L1 ミューオントリガーは W や Z の崩壊からくる高  $p_T$  ミューオンをとらえるためにも非常に重要であり、Higgs の探索等に大きく貢献している。本章ではこのトリガーのエンドキャップ部を担当する TGC と、付随するエレクトロニクスの解説を通して、L1 エンドキャップミューオントリガーシステムの全体像を俯瞰する.

# 2.1 TGC について

まずはTGCの動作原理から配置、用語について説明する.

# 2.1.1 TGC 動作原理

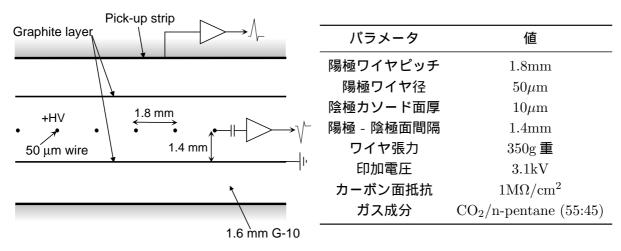

TGC は MWPC の一種であり、直交するアノードワイヤとカソードストリップにより 2 次元読み出しが可能になっている。ワイヤ間の距離が 1.8mm なのに対してワイヤとストリップの間は 1.4mm と短いのが特徴で、25ns 以内の読み出しが可能になっている。 $4 \sim 33$  本のワイヤが R 方向の 1 チャンネルにあたり、1 本のストリップが  $\phi$  方向の 1 チャンネルに相当する。図 2.1 に TGC の内部構造を示す。

図 2.1: TGC の内部構造 [6]

電離ガスとしての CO<sub>2</sub> とクエンチャーとしての n-pentane が 55:45 の割合で混合したガスを用いている. ガス中を荷電粒子が通過した際電離によって生じた一次電子は, チェンバー内の強電場によって電気力線に沿って移動する. そして最も近傍のワイヤに近づくと急激に加速され, 電子雪

崩を起こす. ワイヤはこの電子雪崩を信号として取り出し, またストリップ側も同時に誘起している電荷を読み出す. 電離の際に生じる紫外線はn-pentane が吸収し, 必要以上の電子雪崩が発生するのを抑えている.

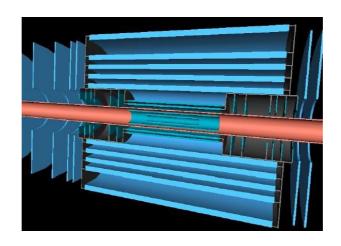

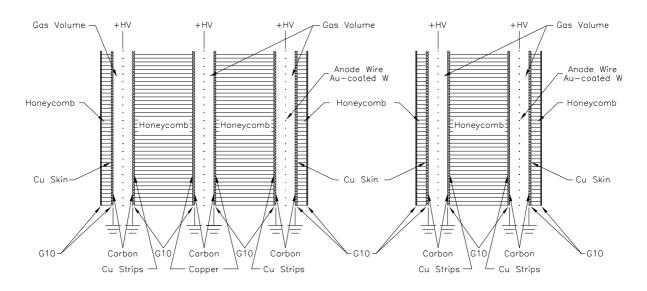

#### 2.1.2 TGC の分類

チェンバーを層の数で分類すると、ダブレットとトリプレットの2種類ある。ダブレットは2つのガスギャップをハニカム構造で支えるようになっており、2つのワイヤ層と2つのストリップ層を読み出す。一方トリプレットでは3つのガスギャップをハニカム構造で支えており、3つのワイヤ層と3つのうち真ん中を除いた2つのストリップ層を読み出す。図2.2にダブレット及びトリプレットの構造を示す。

図 2.2: ダブレット, トリプレットの構造 [6]

また、一枚のチェンバーの大きさで分けると  $T1\sim T9$  までの区分がある。T1 と T2 は  $\phi$  方向に  $2\pi/24=0.26$ rad の広がりを持ち、 $T3\sim T9$  の 2 倍の  $\phi$  をカバーする。トリプレットの T1、T3、T6、T7、T8 チェンバーをこの順に R の小さい方向から並べて  $\phi$  方向に一周させたものが TGC1 (M1) と呼ばれる。T1 を 24 枚、そのほかを 48 枚使って 1 つの大きな円盤状の検出器群を形作るわけである。同様にダブレットの T2、T4、T6、T7、T8、T9 で作ったのが TGC2 (M2)、ダブレットの T2、T5、T6、T7、T8、T9 で作ったのが TGC3 (M3) である。M1、M2、M3 は MDT とともに BW の構成要素となっている。図 2.3 が BW の写真である。

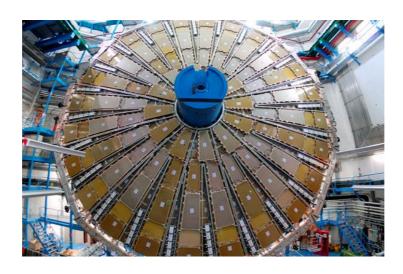

**図** 2.3: Big Wheel[6]

# 2.1.3 TGC の配置

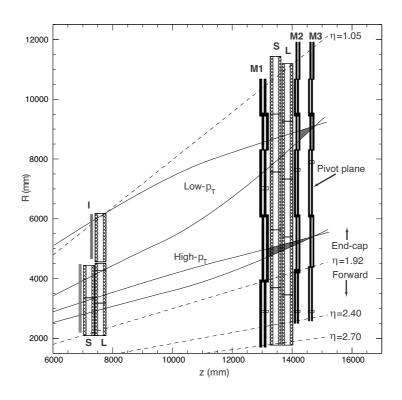

BW の最も内側  $(z \simeq 13\mathrm{m})$  に  $\mathrm{M1}$ , 真ん中  $(z \simeq 14\mathrm{m})$  に  $\mathrm{M2}$ , 外側  $(z \simeq 14.5\mathrm{m})$  に  $\mathrm{M3}$  が配置されている. IP から見るとワイヤ層が 7 層, ストリップ層が 6 層あることになる.  $\mathrm{M1}$  と  $\mathrm{M2}$  の間は  $1\mathrm{m}$  ほど間隙があるが, ここに  $\mathrm{MDT}$  が入っている. 図 2.4 に  $\mathrm{TGC}$  の配置図を示す.

図 2.4: TGC の配置図 [6]

${

m TGC}$  では  $1.05<|\eta|<1.92$  の範囲を通常エンドキャップと呼び、 $1.92<|\eta|<2.70$  を特にフォワードと呼び名をつけている。チェンバーにして  ${

m T1}$ ,  ${

m T2}$  が当たる範囲がフォワードということになる。トリガーや  ${

m DAQ}$  はこの 2 つの領域で分けて処理している。なおフォワードのうち $2.40<|\eta|<2.70$  の領域は  ${

m M1}$  しかカバーしていないため,トリガー情報生成は行われず位置測定のみ行われる。

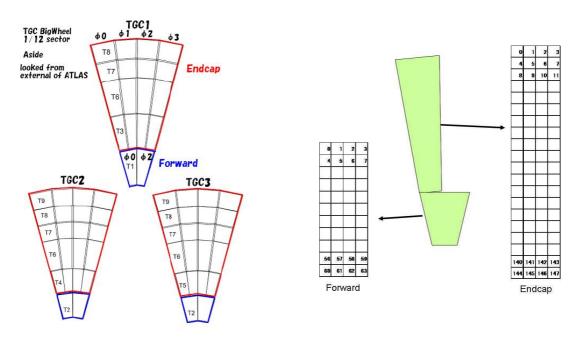

#### 2.1.4 TGC のセクター

$\mathrm{TGC}$  の組み立てや実際のデータ処理等は、円盤を  $\phi$  方向に 1/12 分割したセクターという単位で行われる。また、フォワード部はチェンバー 1 枚、エンドキャップ部は R 方向に連続した 4 枚( $\mathrm{M1}$ )または 5 枚( $\mathrm{M2}$ 、 $\mathrm{M3}$ )の集合をトリガーセクターと呼ぶ。1 セクターにはフォワードのトリガーセクターが 2 つ  $(\phi0,\phi2)$ 、エンドキャップのトリガーセクターが 4 つ  $(\phi0\sim\phi3)$  含まれることになる。トリガーセクターは文字通りトリガー情報を生成する際の単位となる。

これらはさらに小さいサブセクターに分けることができる. 1 つのサブセクターをワイヤ・ストリップともに 8 チャンネルで構成すると、エンドキャップでは 37  $(R) \times 4$   $(\phi) = 148$  サブセクター、フォワードでは 16  $(R) \times 4$   $(\phi) = 64$  サブセクターに分割される. サブセクターはトリガーする位置の最小単位であり、TGC における RoI に相当する. 図 2.5 にセクター及びサブセクターの概略図を示す.

図 2.5: TGC におけるセクター及びサブセクター [25][29]

# 2.2 トリガースキーム

TGC を用いたトリガーはトロイド磁場によるミューオンのずれを測るものである. 本節でその 具体的な測定方法を解説する.

# 2.2.1 $p_{\rm T}$ 算出の概要

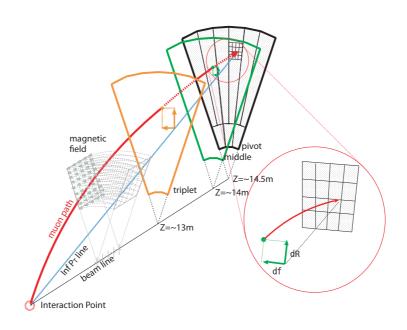

TGC による  $p_T$  推定の流れは次のようなものである.

- 1. IP で陽子の衝突が起こり、W や Z の崩壊などによりミューオンが生成される

- 2. ミューオンは BW に到達する前にエンドキャップトロイド磁場によって曲げられる

- 3. 磁場を通過した後, BW の M1, M2, M3 の順にヒットする. ヒットした点ではフロントエンドエレクトロニクスにより 2 次元情報  $(R,\phi)$  が生成される

- 4. M3 のヒット点と IP を結んだ直線がミューオンが無限運動量を持った時の飛跡であると考えられる。この直線と磁場で曲がった実際の飛跡とのずれ  $(dR, d\phi)$  から  $p_T$  を推定できる

図 2.6 に概略図を載せる.  $p_{\rm T}$  が高いほど磁場で曲げられにくいので  $dR,\,d\phi$  は小さくなるはずである. なお理想的には磁場は  $\phi$  方向なので  $d\phi=0$  のはずであるが, 磁場の非一様性から  $\phi$  方向にもずれる.

図 2.6: p<sub>T</sub> 決定の仕組み [23]

# 2.2.2 段階的なコインシデンス

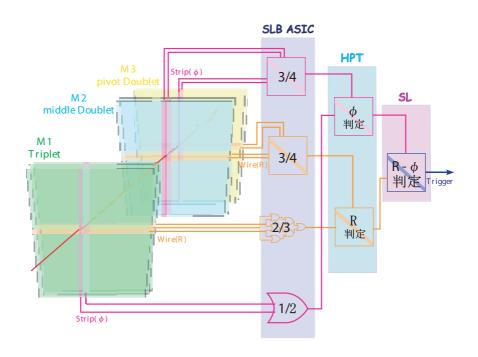

ここでもう少し詳細を見ていく、TGC はヒット情報のコインシデンスを段階的に行っていき、 $p_T$  計算に必要な量をそろえていく、各段階で必要になるエレクトロニクスとともに記すと、以下のような手順になる、図 2.7 を参照、なお各エレクトロニクスについては後で詳細を述べる。

#### 1. SLB ASIC

ダブレット内のコインシデンスとトリプレット内のコインシデンスは、ワイヤとストリップ独立に  ${

m SLB}$  ( ${

m Slave\ Board}$ ) ${

m ASIC}$  により行われる。つまり  ${

m SLB\ ASIC}$  は役割としてダブレット・ワイヤ/ストリップ ( ${

m WD/SD}$ )、トリプレット・ワイヤ/ストリップ ( ${

m WT/ST}$ ) の 4 種類が必要になる。図のように  ${

m WD}$ ,  ${

m SD\ }$  では 3/4 コインシデンス,WT では 2/3 コインシデンス,ST では 1/2 コインシデンスがとられる。さらに WD,SD ではコインシデンスマトリックスにより  ${

m Low}$ - $p_{

m T}$  1情報が生成される

# 2. HpT ボード

次のコインシデンスはダブレットとトリプレットの間で,  $\operatorname{HpT}$  ( $\operatorname{High-}p_{\operatorname{T}}$ ) ボードにより行われる. つまり  $\operatorname{HpT}$  ボードは役割としてワイヤ, ストリップの 2 種類が必要になる. コインシデンスマトリックスにより  $\operatorname{High-}p_{\operatorname{T}}$   $^2$ 情報が生成され, 複数の  $\operatorname{Low-}p_{\operatorname{T}}$ ,  $\operatorname{High-}p_{\operatorname{T}}$  トラックから高いものを選択して  $\operatorname{SL}$  に送る

#### 3. SL ボード

最後のコインシデンスはワイヤとストリップの間で、Sector Logic (SL) ボードにより行われる。Coincidence Window と呼ばれる特別なマトリックスを用いて最終的な  $p_{\rm T}$  情報が生成される

図 2.7: 段階的なコインシデンス [23]

$<sup>^1{</sup>m M2}$  と  ${

m M3}$  の間の  $\Delta$  の度合い. 2 つのダブレットの距離が短く高い  $p_{

m T}$  が測れないことから  ${

m Low-}p_{

m T}$  と呼ぶ

# 2.2.3 Coincidence Window

$\rm L1$  ミューオントリガーでは閾値を複数設定してミューオンの  $p_{\rm T}$  を  $\rm pt1$  ~  $\rm pt6$  の 6 段階に分ける (表 2.1). Coincidence Window (CW) とは SL に届いた (dR,  $d\phi$ ) の組に対してそれが 6 段階のどの  $p_{\rm T}$  に相当するかをマップしたものである. CW は SL に LUT  $^3$  として実装されており, SL は dR,  $d\phi$  情報をアドレスに変換して対応する  $p_{\rm T}$  値を読み出す.

表 2.1: L1 トリガーメニューと  $p_{\rm T}$  の関係

| L1 menu    | pt1 $\sim 6$ | condition               |

|------------|--------------|-------------------------|

| L1_MU0     | pt1          | $p_{ m T}~6{ m GeV}$ 未満 |

| $L1\_MU6$  | pt2          | $p_{ m T}$ 6GeV 以上      |

| $L1\_MU10$ | pt3          | 現在使用されていない              |

| L1_MU11    | pt4          | $p_{ m T}$ 11GeV 以上     |

| $L1\_MU15$ | pt5          | $p_{ m T}$ 15GeV 以上     |

| $L1\_MU20$ | pt6          | $p_{ m T}$ 20GeV 以上     |

図 2.8: CW の例 [29]

図 2.8 は CW の例である. 横軸が  $d\phi$ , 縦軸が dR であり, dR の大きさによって  $p_T$  の領域が移っていくのが見える. 中心にきていないのは, 各チェンバーの占める  $\eta$  の範囲はずれており無限運動量でも dR=0 にならないためである.

CW は RoI の数だけ存在する. 磁場の 8 回対称性から 1/8 円について考えればよいので、含まれる RoI の数を数えると  $6\times 148+3\times 64=1080$  の CW を用意する必要がある. CW はモンテカルロシミュレーションを用いた解析により適宜修正が施され、トリガー効率を落とさない最適な分布が採択される.

$<sup>^3 {</sup>m Look~ Up~ Table}$ : 演算結果をあらかじめメモリに格納しておくことで高速な応答が可能になる. この用意したテーブルのこと

# 2.3 トリガーエレクトロニクス

前節で説明を省略したものも含めて,  $p_{\rm T}$  算出に寄与するものを中心にエレクトロニクスの解説をする.

#### FPGA, ASIC について

FPGA (Field Programmable Gate Array) とは、ユーザーが自由に内部回路を書き換えることのできる LSI である。内部構造は無数のロジックセルからなっており、1 つのセルは組み合わせ回路を記述する LUT と、順序回路を記述する FF (Flip Flop) で構成されている。LUT やロジックセル間をつなぐインターコネクトは RAM であり、これらに値を書き込む(コンフィギュレーション)ことで目的の回路を形成することができる。ただしこのように RAM ベースのアーキテクチャなので、電源を落とすと回路は初期化される。FPGA は目的の回路を得るためのコストや時間が大幅に削減できるため、広範な用途で用いられている。

また、同様の IC に CPLD (Complex Programmable Logic Device) がある。FF と AND/OR アレイからなるマクロセルをスイッチングマトリックスで接続することにより、目的の回路を形成する。不揮発性のメモリをベースにしているので、FPGA と異なり電源を落としても回路が消えることはない。FPGA より規模は小さいが、LSI 間を相互接続したり、不揮発性を生かしてブートローダに使用されたりする。

一方 ASIC (Application Specific Integrated Circuit) もプログラマブルな LSI であるが、こちらは設計が第一に来て、その回路を元に業者が製造するものである。 完成後には通常の LSI と同様にユーザーが回路を書き換えることはできない。 大量生産する場合には FPGA よりも単価が安くなる、コンフィギュレーションの必要がないという特徴がある。

放射線耐性の面からいうと、FPGA や CPLD よりも ASIC の方が強い. そのため高エネルギー実験のフロントエンドでは ASIC を用いることが多い. また、FPGA でも RAM ではなくヒューズ を用いて構成された anti-fuse FPGA は放射線に強く、こちらもしばしば用いられる.

それぞれのデバイスには一長一短あるが、高度な機能を持たせようとすると FPGA を選択する他はない、FPGA はロジックセルの他にも Block RAM や DSP  $^4$ , 高速トランシーバ等の様々な機能をハードで提供しており、FPGA にできないことはなくなりつつある。高エネルギー実験においてもこれから FPGA の重要性は増していくと思われる。

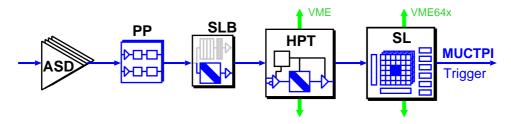

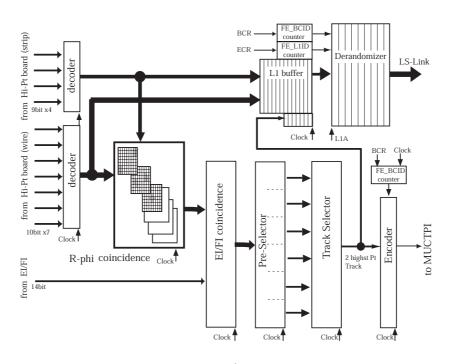

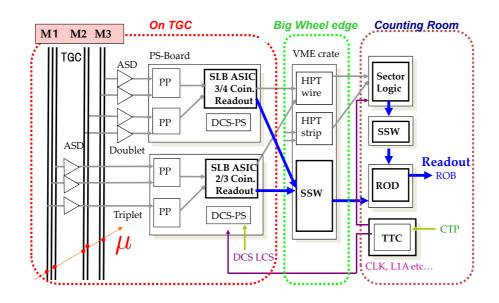

# 2.3.1 全体のフロー

トリガー系のフローにおいては、検出器から出たデータが ASD, PP, SLB, HpT, SL という順に処理される(図 2.9)。各データが一定のレイテンシのもとに処理されることが非常に重要であり、この目的のために要所要所に可変ディレイ回路が備わっている。参考までに現在のレイテンシテーブルの一部を表 2.2 に示す。PS ボードは後述するが、簡単に言うと PP と SLB が含まれたボードのことである。MUCTPI ( $Muon\ trigger\ to\ CTP\ Interface$ ) は TGC のトリガー系と CTP のインターフェースとなるモジュールである。

<sup>&</sup>lt;sup>4</sup>Digital Signal Processor: デジタル信号処理に特化したプロセッサ

図 2.9: トリガーフロー [24]

表 2.2: レイテンシテーブルの例 [33]

|        | ASD | cable | PS Board | cable | НрТ | fibre | SL   | cable | MUCTPI |

|--------|-----|-------|----------|-------|-----|-------|------|-------|--------|

| クロック消費 | 0.5 | 2.5   | 6        | 3     | 6.5 | 18    | 9.5  | 2     | 11     |

| 総クロック  | 5   | 7.5   | 13.5     | 16.5  | 23  | 41    | 50.5 | 52.5  | 63.5   |

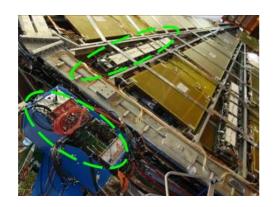

それぞれのエレクトロニクスの詳細は次小節以降に譲るが、どの位置に配置されているかを簡単に記す。 ASD は増幅器であるため TGC の読み出し口に直取り付けられる。 そこから LVDS  $^5$  信号をフラットケーブルで PS ボードに送る。 PS ボードは複数でまとめられて BW の側面に取り付けられている。 PS ボード内の PP と SLB での処理が終わると, LVDS 信号をツイストペアケーブルで  $_{\rm HpT}$  ボードに送る。  $_{\rm HpT}$  ボードの入った  $_{\rm HSC}$  クレートは  $_{\rm BW}$  の外縁に取り付けられている(図  $_{\rm 2.10}$ )。

図 2.11: USA15 のラック [24]

これまでは実験ホール (UX15) であるが、これ以降のエレクトロニクスは 100m ほど離れたカウンティングルーム (USA15) にある。遠いのでデータを運ぶのに光ファイバーを用いなければならず、ATLAS では G-Link  $^6$ と呼ばれる規格で光通信を行っている。HpT から SL も G-Link でつながれており、40 クロック程度かけて SL に到達する。図 2.11 に USA15 の様子を載せる。

$<sup>^5</sup> Low$  Voltage Differential Signaling: 高速差動信号の規格. ANSI/TIA/EIA-644 において最大 655Mbps (理想的な伝送路で 1.923Gbps) と記されている

<sup>&</sup>lt;sup>6</sup>Agilent Technologies 社のトランシーバチップ HDMP-1032/1034 で用いられている通信規格. TGC では 20bit × 40MHz = 800Mbps で使用する

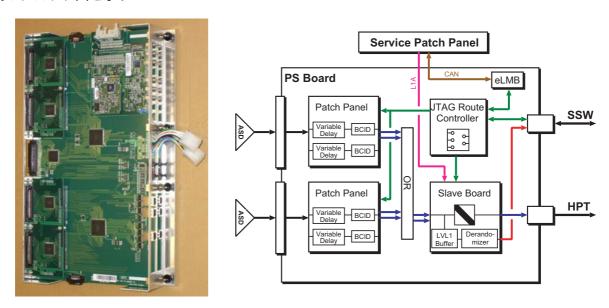

### 2.3.2 フロントエンド

ここでは TGC に直結された ASD から, PS ボードに含まれるエレクトロニクスの紹介をする. PS ボード (Patch panel and Slave board ASIC Board) は PP, SLB を含む各種 ASIC が搭載されており, フロントエンドにおける読み出しから制御まで行う多機能プラットフォームである. ここでは PP ASIC と SLB ASIC の説明にとどめる. 1/2 セクターごとにまとめられており, トリプレット用は 10 個, ダブレット用は 17 個の PS ボードが連結されている. 図 2.12 に PS ボードの写真とブロック図を示す.

図 2.12: PS ボードの概要 [24]

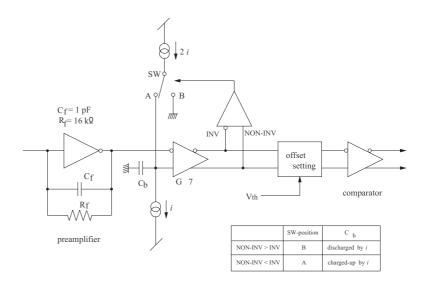

# ASD

ASD (Amplifier Shaper Discriminator) ASIC は TGC のアナログ信号を増幅、整形したのち、閾値電圧を超えていたらデジタルパルスを出力する ASIC である. 1 つの ASD ボードは 4 チャンネルを処理する ASD ASIC を 4 つ搭載しており、計 16 チャンネルを担当している. また、7 層のワイヤ及び 6 層のストリップには全て同一の ASD ボードが取り付けられている. 処理されたデジタル信号は LVDS にして PS ボードに送られる. 図 2.13 に ASD の写真とブロック図を示す.

#### PP ASIC

PP (Patch Panel) ASIC は PP に届く信号のタイミング調整及びベンチ識別の役割を担っている。各 PP に信号が届くタイミングは  $TOF^7$  の差やケーブル長の差によりばらつきが生じているので, 25/32=0.78ns を単位として  $0\sim24.2ns$  の範囲でディレイをかけることで, このばらつきを吸収させる。PP より前には可変ディレイ回路は存在しない上, 後段にバンチ識別が控えているため非常に重要な機能である。

PP のもう一つの重要な役割がバンチ識別である. 具体的には  ${

m TTC}$  から供給される  ${

m LHC}$  クロックと同期をとることを行っている. これにより同じバンチクロッシングのデータは同じクロック

<sup>&</sup>lt;sup>7</sup>Time Of Flight: 粒子の飛行時間

図 2.13: ASD の概要 [23]

のエッジにそろえられる. なお, 1 つの PP ASIC は 32 チャンネル, つまり 2 つの ASIC ボードからの入力を処理できる.

#### SLB ASIC

SLB ASIC は多機能の ASIC で、大きくトリガー部とリードアウト部に分けられる。 入力は共通で、複数の PP からくるヒット情報を適切に並べて、最大  $160\mathrm{bit}$  のヒットマップと呼ばれる形にしたものである。 WD 及び SD のヒットマップは 4 層のワイヤ/ストリップを  $32\mathrm{bit} \times 4$  のように並べた形になっている。 同様に WT のヒットマップは 3 層のワイヤを  $32\mathrm{bit} \times 3$  に並べた形である。 ST はストリップが 2 層なので 2 枚分のチェンバーの並べて 1 つのヒットマップとしている。

トリガー部では、前述の通り WD, SD, WT, ST の 4 種類のコインシデンスをとる。1 つの ASIC はこれら 4 種類のマトリックスを実装しており、レジスタでこれらを切り替える。WD, SD では 2 ヒット分の位置データと  $Low-p_T$  情報が生成される。同様に WT では 3 ヒット分の位置データ,ST では 4 ヒット  $\times 2$  チェンバー分の位置データが生成される。これらトリガーデータはシリアル化されて HpT に送信される。

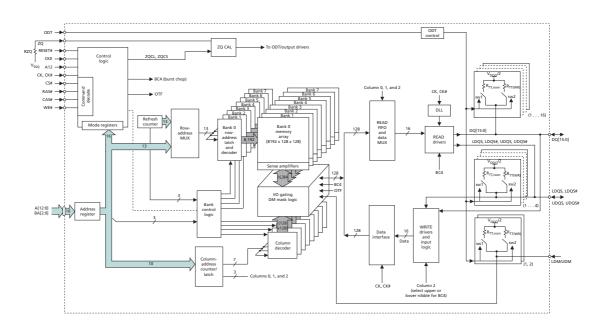

リードアウト部は L1 Buffer とデランダマイザで構成される. SLB の L1 Buffer は  $212 \mathrm{bit} \times 128$  段のシフトレジスタであり、最大  $3.2 \mu s$  の間データを保持できる.  $212 \mathrm{bit}$  のうち  $160 \mathrm{bit}$  は入力されたヒットマップである. 残りの  $52 \mathrm{bit}$  の内訳はトリガー部で生成されたデータが  $40 \mathrm{bit}$ , バンチカウンタの値 (BCID: Bunch Crossing ID) が  $12 \mathrm{bit}$  である.

L1A が TTC により供給されると、前後  $\pm 1$  イベントが L1 Buffer から取り出され、デランダマイザに入れられる。その際 4bit のイベントカウンタの値(L1ID: Level 1 ID)が付加され、データ長は 216bit になる。デランダマイザでタイミングを調整された後、3 バンチ分のデータは別々のシリアライザに入れられ、フラグビット用のシリアルデータと合わせて 4bit の LVDS 出力として取り出される。イベントカウンタとバンチカウンタは TTC の ECR、BCR に従って SLB 内でカウントしており、データの目印になる。

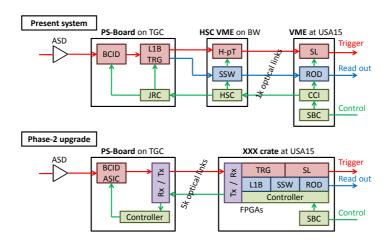

# 2.3.3 HSC クレート

HSC クレートは HpT SSW Crate の略で文字通り HpT 及び SSW のための VME <sup>8</sup> 9U クレートである. 1 セクターにつき 1 つの HSC クレートが対応するため, 合計で 24 のクレートが用意されている. クレート自体が BW の外縁にあり, 放射線環境下にあることから, HSC (HpT SSW Controller board) という特殊なモジュールを VME マスターとしている. HSC は G-Link で USA15 にある CCI (Control Configuration Interface board) から遠隔操作される.

# HpT

${

m HpT}$  ボードはダブレット-トリプレットのコインシデンスをとるためのモジュールである.  ${

m HpT}$  ASIC は 1 枚でワイヤとストリップの両方で使えるように設計されており, 外付けのスイッチで選択できる. コインシデンスマトリックスにより, 最大で 6 トラック分のトラックが  ${

m High}$ - $p_{

m T}$  トラック候補として挙がる. セレクタにより, このうち  $p_{

m T}$  の高い 2 トラックが選出される. 2 トラックに達しない場合, ダブレットの SLB ASIC で生成された  ${

m Low}$ - $p_{

m T}$  トラックを加えて 2 トラックにする.

${

m HpT}$  ボードにはエンドキャップ・ワイヤ (EW), エンドキャップ・ストリップ (ES), フォワード (FW) の三種類がある. EW- ${

m HpT}$  ボードはトリガーセクター 1 つ分のデータを複数の  ${

m SLB}$  ASIC より受け取り, 4 つの  ${

m HpT}$  ASIC で処理する. 最大 7 トラック9のデータが生成され,  ${

m G-Link}$  により  ${

m SL}$  に送られる. 一方 ES- ${

m HpT}$  ボードはトリガーセクター 2 つをカバーしており, 1 つのトリガーセクターにつき 2 つの  ${

m HpT}$  ASIC が処理する. それぞれ最大 4 トラックのデータが生成され, 対応する  ${

m SL}$  に送られる. 図 2.12 に  ${

m FW-HpT}$  ボードの写真と  ${

m EW-HpT}$  のブロック図を示す.

図 2.14: HpT の写真 [23]

図 2.15: SL の写真 [24]

<sup>&</sup>lt;sup>8</sup>VERSAmodule Eurocard bus: バスの規格の一種. 高エネルギー実験でしばしば用いられる <sup>9</sup>4 つのうち 1 つの ASIC は TGC の端に相当し、1 トラックしか選出しない

# 2.3.4 SL クレート

SL のクレートは USA15 にある VME9U+6U クレートであり, 4 セクター分の SL と TTC 信号 のファンアウトモジュール, VME マスターとしての SBC  $^{10}$  が収められている. USA15 にあるので HpT とは G-Link で接続されている.

#### SL

$\operatorname{SL}$  は R 方向と  $\phi$  方向の情報を用いて最終的な  $p_{\mathrm{T}}$  を生成するモジュールである.  $\operatorname{SL}$  ボードはエンドキャップ (EC) とフォワード (FW) の 2 種類存在し、どちらも 2 つの独立したトリガーセクターをカバーする. つまり EC-SL を 2 枚と FW-SL を 1 枚で 1 セクターがカバーされる.

SL ボードの 1 つのトリガーセクターにつき、コインシデンス用の FPGA が 1 つと読み出し用の SLB ASIC を 1 つ用いる。 2 つのトリガーセクターは独立なため、1 枚のボードには FPGA と SLB ASIC が 2 つずつ載る。 EC-SL ではトリガーセクターごとに EW-HpT と ES-HpT のコインシデンス処理をする。 FW-SL でも同様に FW-HpT のデータのコインシデンス処理をする。

FPGA ではまず CW を用いて Sub Sector Cluster (SSC) ごとに 6 段階の pt 判定を行う. SSC は R 方向に 2 つ  $\phi$  方向に 4 つのサブセクターの集まりで、SL でトリガー判定する際の単位となる. 次にプリセレクタにより各 pt につき 2 トラックが選ばれる. 最後にトラックセレクタにより pt の優先順に 2 トラックが選出され、MUCTPI に送信される. このデータはそれぞれのトラックの RoI、pt、BCID 等が含まれ、32bit のパラレルデータとなっている. SL への入力は PS ボード中の SLB ASIC で BCID が付けられたデータではないので、SL 中のバンチカウンタの値を付加している.

図 2.16: SL のブロック図 [23]

<sup>&</sup>lt;sup>10</sup>Single Board Computer: CPU や HDD を積んでおり、 ログインして VME を直接コントロールできるモジュール

表 2.3: SLB ASIC と各エレクトロニクスの対応関係 [22]

| PS Board | SLB ASIC | HpT ASIC | $\operatorname{SL}$ |

|----------|----------|----------|---------------------|

| EWD0     | EWD0-0   | EW0      | EC                  |

|          | EWD0-1   | EW1      |                     |

| EWD1     | EWD1-0   |          |                     |

|          | EWD1-1   |          |                     |

| EWD2     | EWD2-0   | EW2      |                     |

|          | EWD2-1   |          |                     |

| EWD3     | EWD3-0   |          |                     |

|          | EWD3-1   | EW3      |                     |

| EWD4     | EWD4-0   |          |                     |

|          | EWD4-1   |          |                     |

| ESD0     | ESD0-0   | ES0/2    |                     |

|          | ESD0-1   |          |                     |

| ESD1     | ESD1-0   | ES1/3    |                     |

|          | ESD1-1   |          |                     |

|          | ESD1-2   |          |                     |

| FWD0     | FWD0-0   | FW0      | FW                  |

|          | FWD0-1   |          |                     |

| FWD1     | FWD1-0   |          |                     |

|          | FWD1-1   | FW1      |                     |

| FSD      | FSD0-0   | FW2      |                     |

| PS Board | SLB ASIC | HpT ASIC | SL |

|----------|----------|----------|----|

| EWT0     | EWT0-0   | EW0      | EC |

|          | EWT0-1   | EW1      |    |

|          | EWT0-2   |          |    |

| EWT1     | EWT1-0   | EW2      |    |

|          | EWT1-1   |          |    |

| EWT2     | EWT2-0   | EW3      |    |

|          | EWT2-1   |          |    |

| EST      | EST0-0   | ES0/2    |    |

|          | EST0-1   | ES1/3    |    |

| FT0      | FWT0-0   | FW0      | FW |

|          | FWT0-1   |          |    |

| FT1      | FWT1-0   | FW1      |    |

|          | FWT1-1   |          |    |

|          | FST0-0   | FW2      |    |

SL に載せられた SLB ASIC は PS ボードのものと同一であり、SL よりのち読み出し系と同じ手順で読み出すこととなる。この読み出しデータには  $32 \mathrm{bit}$  のトリガーデータに SL の入力データを加えたものを用いている。図 2.15 に EC-SL ボードの写真を、図 2.16 にブロック図を示す。また、表 2.3 に SLB ASIC と他のエレクトロニクスの対応関係を示す。

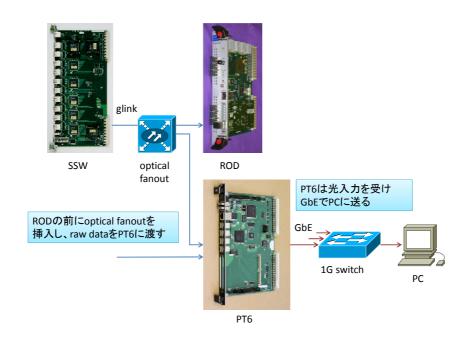

# 2.3.5 SL からの読み出し

SL の読み出しデータは PS ボードからの読み出しと同様に SLB ASIC, SSW, ROD という順番で読み出される. ただしここでの SSW は HSC クレートではなく USA15 にある SSW 専用のクレートに収められている. 図示すると図 2.17 のようになる.

# $\mathbf{SSW}$

SSW (Star Switch) はスター型のトポロジーで SLB ASIC から読み出しデータを集め、圧縮する役割を持っている. 全ての SSW ボードの構成は同一で、放射線耐性のある anti-fuse FPGA をデータ受信用に 6 つ、送信用に 1 つ積んでいる. 1 つの受信 FPGA につき最大 4 つの SLB ASIC からのデータを受けられる.

データの圧縮にはゼロサプレスと呼ばれる手法を用いている。これはデータを8bitずつのセルに分割して、全て0であるセルは完全に落としてしまい、1が1つでもあったセルはセルの番号を

図 2.17: リードアウトフロー [24]

付加して送る方法である.  $\operatorname{TGC}$  のデータのように 0 が連続するデータストリームに対して有効だが、1 が多いと逆にデータ量が多くなることがある. 圧縮されたデータは送信用の anti-fuse FPGA に渡され、 $\operatorname{G-Link}$  に変換してから ROD に送られる.

用途で分けるとダブレット・エンドキャップ/フォワード, トリプレット・エンドキャップ/フォワードの 4 種類がある. ダブレット・エンドキャップはトリガーセクター 1 つ分, その他は 2 つ分をカバーし, 全部で 8 枚の SSW ボードが HSC クレートに収められている. SL 用の SSW は 2 枚の EC-SL と 1 枚の FW-SL からのデータを処理するので, 1 枚で 1 セクター分に相当する. SSW は 12 セクターでまとめられて USA15 の専用のクレートに収められている. 図 2.18 に SSW の写真を示す.

図 2.18: SSW の写真 [23]

図 2.19: ROD の写真 [25]

#### ROD

ROD (Read Out Driver) は TGC の読み出しデータが最終的に集まるモジュールであり、後段の ROB のためのフォーマットに整形する役目を持つ。 ヘッダ・トレイラの情報を入手するために TTC 信号を受けるためのメザニンカードを載せている。 1 セクター分の SSW のデータを受け取り、フォーマット変換の後に S-Link[10] という光信号の規格で ROB に送る。また、何らかの原因でエラーが起きた場合には busy 信号を CTP に送信する。図 2.19 に ROD の写真を示す。

#### 2.3.6 TTC

TGC のエレクトロニクスで TTC の信号を用いるのは主に PS ボード及び SL の SLB ASIC, そして ROD である. まず, BW 上の PS ボードには SPP (Service Patch Panel board) が連結されている. これは TTCrq というメザニンカードを用いて TTC の光信号をデコードし, フラットケーブルにより各 PS ボードに TTC 信号をファンアウトするモジュールである. ダブレットの 17 個連結された PS ボードに供給できるように、最大 18 個にファンアウトできる構造になっている.

USA15 において、SL は VME クレートに収められているため、CO SPP を CME 用に改良した CME が用いられている。これによりクレート内の CME 個の CME に関しては CME では CME と呼ばれるメザニンカードを用いてデコードしている。ROD ごとにカード を搭載しているため、光信号をファンアウトして入れる必要がある。このためには CME という 光ファンアウトモジュールを用いる。

# 2.4 レベル1ミューオントリガーの改善に向けて

LHC は HL-LHC を目指して段階的にアップグレードしていくが、それに伴いミューオングループの担当する L1 ミューオントリガーシステムもアップグレードが求められる。物理ランが終わる 2012 時点で、最も対策を講じなければならないと思われるのはフェイクミューオンの多さであり、実にミューオントリガーの約 98% はこのような IP 由来以外のミューオンでかかってしまっている。

本節では現状トリガーシステムの問題点の把握と、改善に向けたミューオングループの取り組みを述べる.

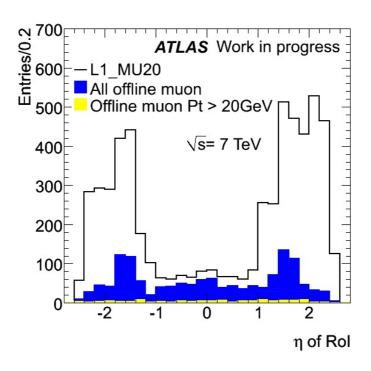

# 2.4.1 現状の問題

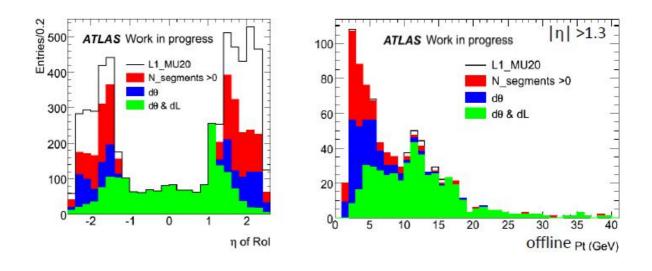

ミューオンスペクトロメータの L1 トリガーメニューのうち、最も重要度の高い L1\_MU20 について考える。これはミューオンが  $p_{\rm T}20{\rm GeV}$  以上を持っていると判断された場合に発行されるトリガーで、2012 年時点で  $4.5{\rm kHz}$  使っている。しかしこのままルミノシティが上がると L1\_MU20 レートも上がり、ミューオンに割り当てられている  $15{\rm kHz}$  を phase-1 で超えてしまう恐れがある。ここで L1\_MU20 のエントリーを  $\eta$  の分布で見ると図 2.20 のようになっている.黒線が L1\_MU20 のイベント数,青がオフラインで再構成されたイベント数,黄がオフラインミューオンのうち実際に  $p_{\rm T}20{\rm GeV}$  以上であったイベント数である.

このように, L1\_MU20 で本来発行すべきなのはたった 2% しかないことがわかる. 残りの 98%はフェイクミューオンであり, できる限り減らさなければならない. これらのほとんどが  $|\eta|>1.0$

のエンドキャップ領域 (TGC が担当) からきており, エンドキャップのトリガー方法を改善し, ルミノシティが上がっても 15kHz 以内に収める必要がある.

図 2.20: L1\_MU20 の  $\eta$  分布 [17]

# 2.4.2 フェイクミューオンの原因

フェイクの原因としては大きく分けて 2 つある. 一点目は, そもそもミューオンでない別の荷電 粒子が磁場に曲げられ, IP から来たように見えるものである. 図 2.20 においてオフラインで再構 成されていないイベント (黒線-青) に相当する. このような荷電粒子には高エネルギー中性子が ビームパイプをたたいて生成される陽子や, ビームハロー<sup>11</sup>が考えられる.

二点目は、IP 由来のミューオンであっても、ミューオントリガーシステムの  $p_T$  分解能が悪いため  $20 {\rm GeV}$  以上と誤ってしまうものである。図 2.20 において  $20 {\rm GeV}$  を下回るオフラインミューオン (青-黄) に相当する。 $p_T$  を決定する際 BW において行っていたのは、トラックの角度を測ることである。3 枚の TGC を用いて  $3 {\rm mrad}$  程度の分解能で測定していたわけだが、これをさらにゆがませる要因が複数存在する。

- 1. エンドキャップトロイド領域で起こる多重散乱: ~0.5mrad

- 2. カロリメータ領域で起こる多重散乱: ~3mrad

- 3. nominal IP からのずれの影響: ~2mrad

$<sup>^{11}</sup>$ 陽子ビームがビームパイプ内残留ガスと弾性/非弾性散乱したり、ビーム同士が弾性衝突したりして生じる二次粒子. 実験装置を横切るようにして通過するのが特徴

# 2.4.3 phase-0 での対策

phase-0 では、SW に存在する現在トリガーに用いられていない TGC の情報を用いる。この TGC (EI/FI) のヒットを要求することで、ビームパイプからくるフェイク粒子を落とせる。実際、 $2012 \pm 4 \sim 5$  月のデータで解析したところ、3 割弱のレートを削減できることが示されている [20]. そこで EI/FI の情報を BW の TGC の情報とコインシデンスをとるロジックを追加する.

このロジックは  $\operatorname{SL}$  の  $R-\phi$  コインシデンスの後に挿入される.  $\operatorname{EI}/\operatorname{FI}$  からの入力は現状のボードでは  $64\mathrm{bit}$  分が入っているので, デコードして  $\operatorname{BW-SW}$  コインシデンスをとる. すでにファームウェアの開発 [19] は終わり, 現在は  $\operatorname{BW}$  と  $\operatorname{SW}$  の間のディレイの調整中である.

# 2.4.4 phase-1 での対策

phase-1 では NSW が導入される. NSW を用いてフェイクを減らすには, NSW にヒットのあるトラックのみ考え, さらに NSW においてミューオンの角度の精密測定ができればよい. まず NSW にヒットがあること前提なので, ビームパイプからくる粒子は完全に除ける. さらに IP と NSW のヒット位置を結ぶ直線とミューオンの角度の差  $d\theta$  を用いることで, IP からきていないミューオンやビームハローが除ける. 1mrad 程度の角度分解能の検出器を用意することでこれらは達成できる. こうして IP からきているとみなされたトラックを, BW で  $R-\phi$  コインシデンスのとれているトラックとコインシデンスをとることにより、多くのフェイクを落とすことができる.

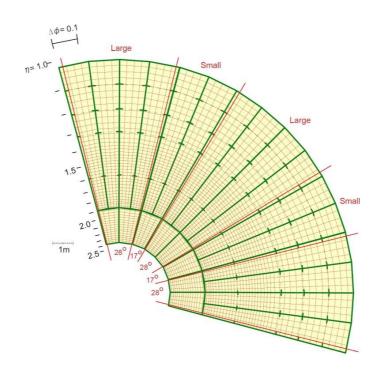

ここで SW のセグメント (精密位置検出器におけるトラック) 情報を用いた 3 段階のカットにより,  $L1\_MU20$  のレートがどれほど落ちるかを見積もる. 手順は以下の通りである.

- 1. 全ての L1\_MU20 のイベントに対して、セグメントを要求する (InnerSeg)

- 2. 1のイベントに対して、 さらに  $d\theta$  がある一定値以内であることを要求する  $(d\theta$  カット)

- 3. 2 のイベントに対して、さらに dL がある一定値以内であることを要求する (dL カット)

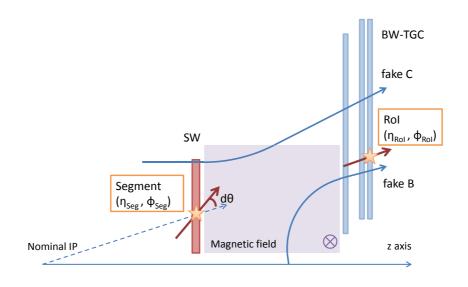

2 の  $d\theta$  は図 2.21 のように IP とセグメントを結んだ線とトラックの向く方向の差である.  $d\theta\simeq 0$  を要求することで IP 指向性が確保される. 一方 3 の dL はセグメントと BW-TGC の RoI における  $(\eta,\,\phi)$  の差である.

$$dL = \sqrt{(\eta_{\rm RoI} - \eta_{\rm Seg})^2 + (\phi_{\rm RoI} - \phi_{\rm Seg})^2}$$

こちらも本来の高  $p_T$  ミューオンなら  $dL \simeq 0$  のはずなので、フェイクを落とすことができる.

図 2.22 にこれらカットをかけた場合の  $L1\_MU20$  のイベント数の変化を示す. レートは低い  $p_T$  で大幅に減り、全体では 31.5% まで落ちている. これらカットの効率は 96.6% と高く、本物のミューオンを落とさずにフェイクを削ることができていることがわかる.

図 2.21:  $d\theta$ , dL カットの模式図

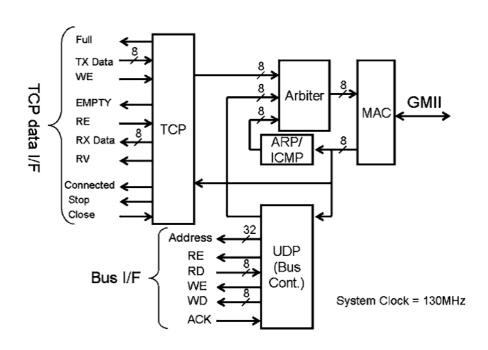

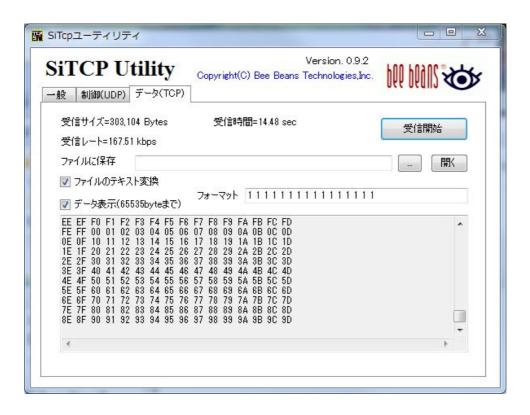

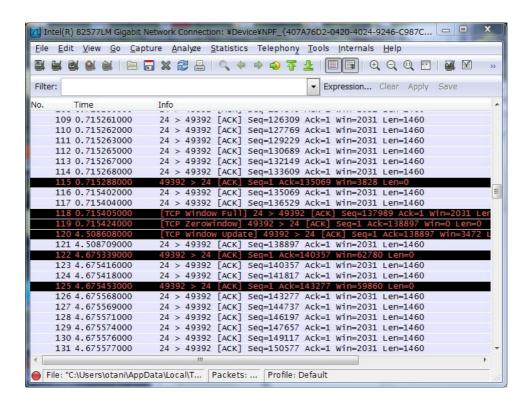

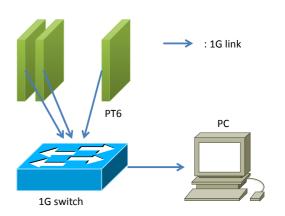

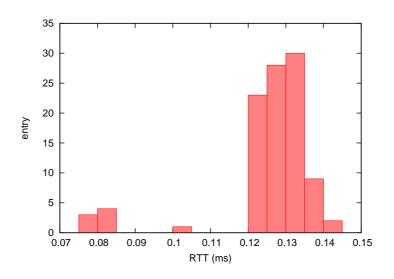

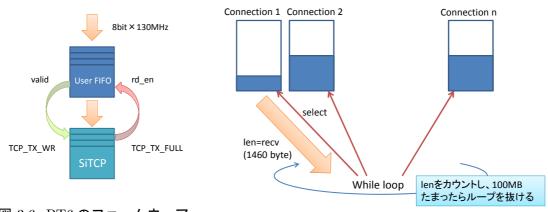

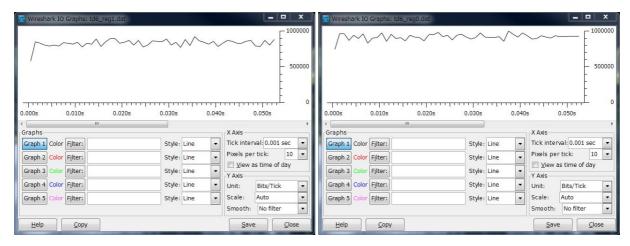

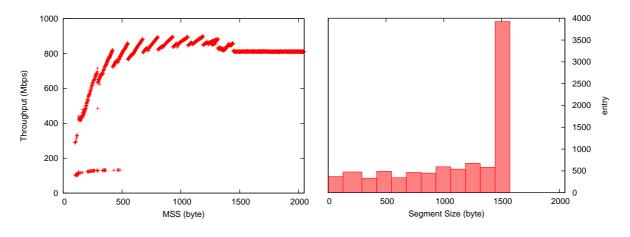

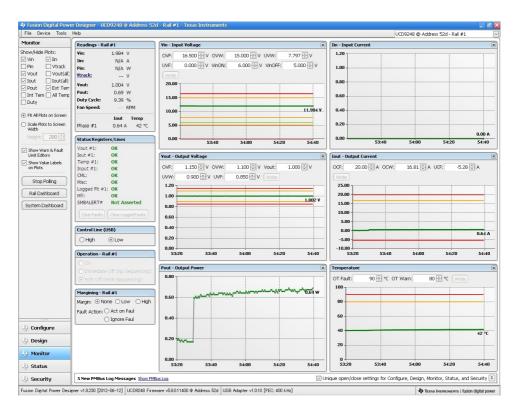

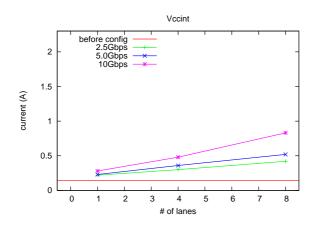

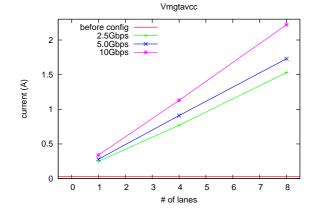

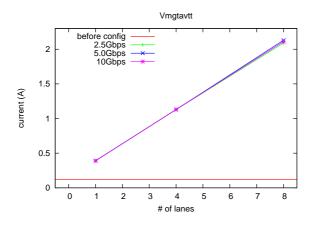

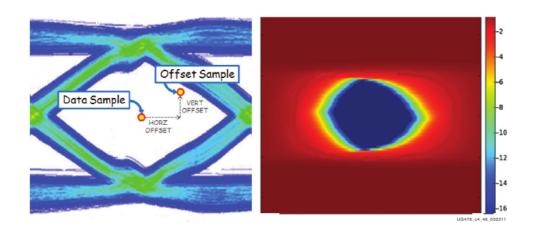

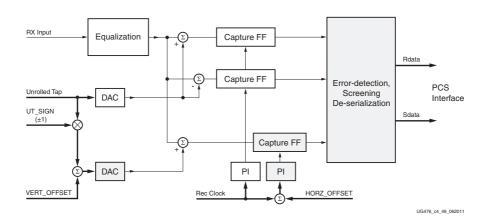

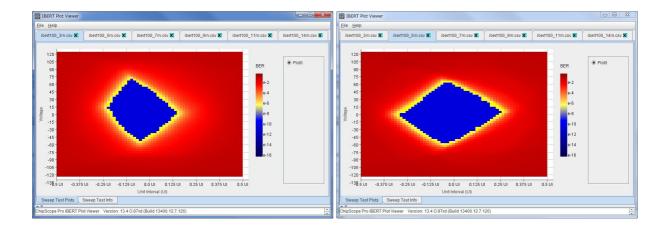

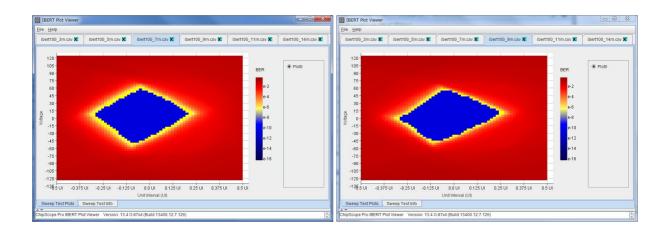

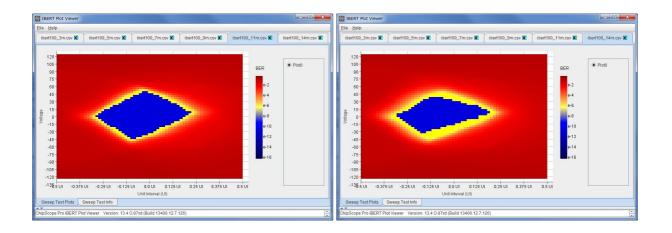

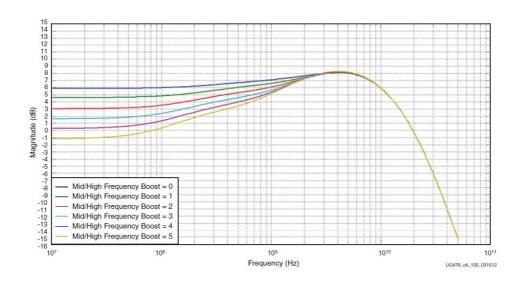

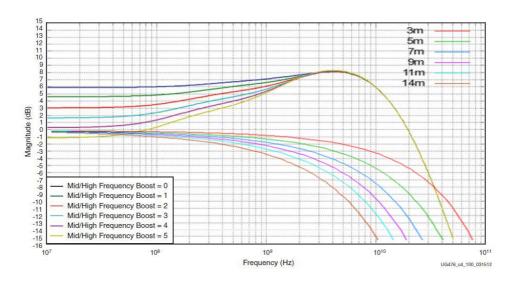

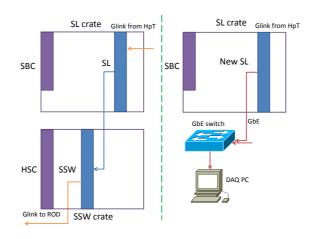

図 2.22:  $d\theta$ , dL カットの結果 [17]